Bom dia, querido leitor! Me pediram para escrever sobre UHCI - bem, eu escrevo.

Você pode achar este artigo útil se, por exemplo, você não tiver habilidades suficientes de escrita para drivers e leitura de documentação para um hardware. Um exemplo simples: você deseja gravar seu sistema operacional para um mini PC, para que algumas distribuições do Windows ou de outro Linux não façam o download do ferro, e você use todo o seu poder exclusivamente para seus próprios fins.

O que é UHCI?

Penso que, para não falar novamente sobre o que e por quê, basta deixar um link para o meu artigo anterior sobre EHCI.

Pique aquiUHCI - Universal Host Controller Interface, opera como um dispositivo PCI, mas, diferentemente do EHCI, usa portas em vez de MMIO (Memory-Mapped-IO).

Termos a serem usados a seguir

- Driver USB (USBD) - o próprio driver USB

- HC (Host Controller) - um controlador host ou apenas o nosso UHCI

- Host Controller Driver (HCD) - um driver que conecta hardware e USBD

- Dispositivo USB - o próprio dispositivo USB

Tipos de transferência de dados

Isócrono - transmissão isossíncrona, que possui uma determinada frequência de transferência de dados. Pode ser usado, por exemplo, para microfones USB, etc.

Interrupção - Transferências de dados pequenas e espontâneas de um dispositivo. O tipo de transmissão de interrupção suporta dispositivos que requerem um intervalo de serviço previsível, mas não fornecem necessariamente um fluxo de dados previsível. Geralmente usado para dispositivos como teclados e dispositivos apontadores que podem não fornecer dados por longos períodos de tempo, mas exigem uma resposta rápida quando eles têm dados para enviar.

Controle - Tipo de transmissão de informações sobre o status, status e configuração do dispositivo. O tipo de transferência de controle é usado para fornecer um canal de controle do host para os dispositivos USB. As transmissões de controle sempre consistem em uma fase de configuração e zero ou mais fases de dados seguidas por uma fase de status. É imperativo que a transferência de controle para um determinado terminal seja processada no modo FIFO. Se o controle for passado para o mesmo terminal, a intercalação pode levar a um comportamento imprevisível.

Bulk - tipo de transferência de matrizes de dados. Usado, por exemplo, em dispositivos MassStorage.

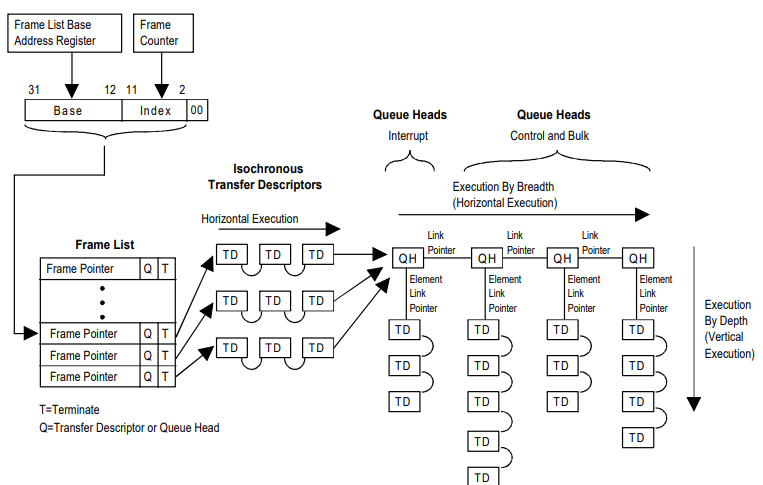

É assim que se parece a distribuição de tempo de 1 ms - processamento de um quadro.

Distribuição de tempo

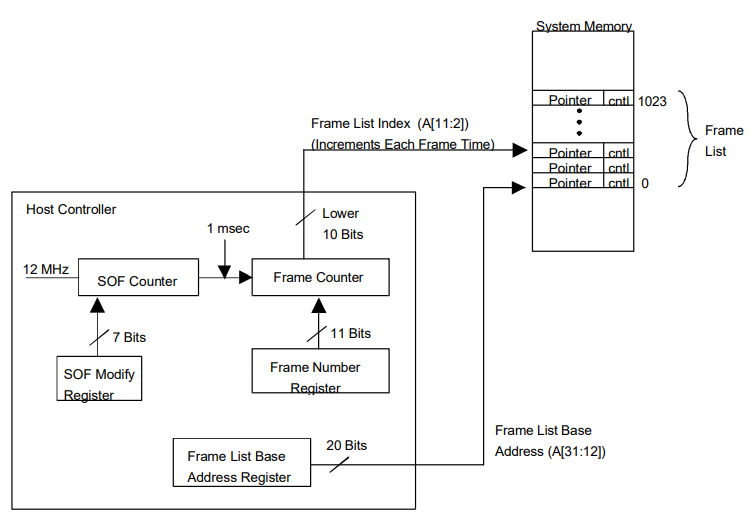

O controlador host suporta a entrega de dados em tempo real, gerando um pacote Start Of Frame (SOF) a cada 1 ms. Um pacote SOF é gerado quando o contador SOF no controlador host expira (Figura 3). O controlador host inicializa o contador SOF por um tempo de quadro de 1 ms. Pequenas alterações podem ser feitas nesse valor (e, portanto, no período de tempo do quadro) programando o registro de alterações SOF. Esse recurso permite que você faça pequenas alterações no período do quadro, se necessário, para manter a sincronização em tempo real em todo o sistema USB.

O controlador host inclui o número do quadro em cada pacote SOF. Esse número de quadro determina exclusivamente o período do quadro em tempo real. A condição de fim de quadro (EOF) ocorre no final do intervalo de 1 ms quando o controlador host inicia o próximo tempo de quadro, gerando outro pacote SOF com o número de quadro correspondente. Durante o período do quadro, os dados são transmitidos como pacotes de informações. O período do quadro é rigorosamente imposto pelo controlador host, e os pacotes de dados no quadro atual não podem ir além do EOF (consulte o Capítulo 11 na especificação USB). O controlador host suporta a sincronização da transmissão de dados entre quadros em tempo real, vinculando o número do quadro para executar uma entrada específica na lista de quadros. O contador de quadros do controlador host gera um número de quadro (valor de 11 bits) e o inclui em cada pacote SOF. O contador é programado através de registradores e cada período de quadro é incrementado. O controlador host usa os 10 bits inferiores do número de quadros como um índice na lista de quadros com 1024 quadros, armazenados na memória do sistema. Assim, como o contador de quadros controla a seleção de uma entrada da lista de quadros, o controlador host processa cada entrada da lista em um determinado período de quadros. O controlador host se expande para a próxima entrada na lista de quadros para cada novo quadro. Isso garante que as transmissões isócronas sejam executadas em um quadro específico.

Figura 3:

Estrutura UHCI

Tudo é exatamente igual ao EHCI. Solicitações de exemplo para HC:

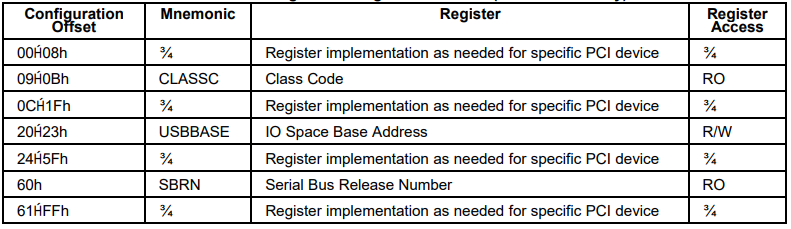

Configurar e acessar UHCI

E assim, como eu disse anteriormente, o UHCI funciona através de portas, portanto, do PCI, precisamos descobrir a base dos registros UHCI.

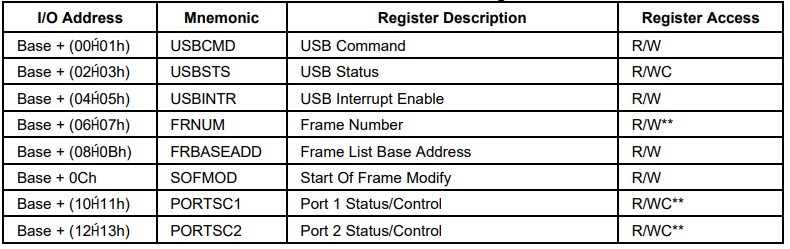

No deslocamento 0x20, existem 4 bytes - IO Base. Em relação ao IO Base, podemos usar os seguintes registros:

Registradores UHCI

- USBCMD é um registro para controlar o HC. Bits:

- Bit 6 é um sinalizador que o dispositivo está configurado e inicializado com sucesso.

- Bit 1 - Redefinição HC. Defina para redefinir HC.

- Bit 0 - Executar / Parar. Exibe o status HC. 1 - obras, 0 - não.

- USBSTS - Registro de status. Bits:

- Bit 5 - HC parado. Ocorreu um erro ou o controlador concluiu com êxito a redefinição do HC.

- Bit 4 - Erro no processo do controlador host. O bit é definido como 1 quando ocorre um erro crítico e o HC não pode continuar na fila e no TD.

- Bit 3 - Erro no sistema host. Erro de PCI.

- Bit 1 - Erro de interrupção. Indica que ocorreu um erro e o HC gerou uma interrupção.

- Bit 0 - Interromper. Indica que HC gerou uma interrupção.

- USBINTR - Registro das configurações de interrupção. Bits:

- O Bit 2 - COI - Interromper na conclusão - gera uma interrupção no final da transação.

- FRNUM - Número do quadro atual (pegue & 0x3FF para o valor correto).

- FLBASEADD - Endereço base da lista de quadros - endereço da lista de quadros.

- PORTSC - Status e controle da porta - registro de status e controle de porta. Bits:

- Bit 9 - Redefinição de porta - 1 - porta a redefinir.

- Bit 8 - indica que um dispositivo de baixa velocidade está conectado à porta

- Bit 3 - Indica que a porta no estado mudou

- Bit 2 - Indica se a porta está ativada

- Bit 1 - indica que o status do dispositivo está conectado à porta

- Bit 0 - indica que o dispositivo está conectado à porta.

Estruturas

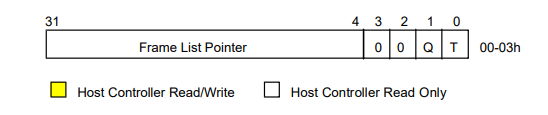

Ponteiro da lista de quadros

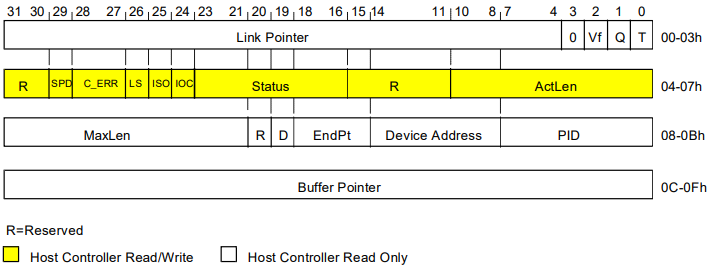

Descritor de transferência

TD CONTROLE E ESTADO

. Bits:

- Bits 28-27 - contador de erros, semelhante ao EHCI.

- Bit 26 - 1 = Dispositivo de baixa velocidade, 0 = Dispositivo de velocidade total.

- Bit 25 - 1 = TD isossíncrono

- Bit 24 - COI

- Bits 23-16 - Status:

- Bit 23 - Indica que é um TD ativo

- Bit 22 - Parado

- Bit 21 - Erro no Buffer de Dados

- Bit 20 - Babble Detected

- Bit 19 - NAK

- Bits 10–0: O número de bytes transmitidos pelo controlador host.

TD Token

- Bits 31:21 - Max Packet Len, semelhante ao EHCI

- Bit 19 - Alternância de dados, semelhante ao EHCI

- Bits 18:15 - Número do ponto final

- Bits 18:14 - endereço do dispositivo

- Bits 7: 0 - PID. Entrada = 0x69, Saída = 0xE1, Instalação = 0x2D

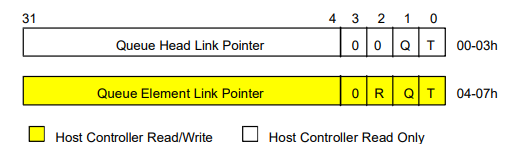

Cabeça da fila

Código

Inicialize e configure o HC:

PciBar bar; PciGetBar(&bar, id, 4); if (~bar.flags & PCI_BAR_IO) {

Solicitações de terminal e controle: