Nos comentários do meu

artigo sobre o controle de LEDs RGB usando o bloco PSoC do microcontrolador UDB da Cypress, sugeriu-se que seria bom dizer brevemente no início do artigo o que é UDB. Como já observei no artigo, não posso escrever sobre o UDB brevemente, mas você pode simplesmente transferir a documentação da empresa para familiarizar o leitor doméstico com uma ferramenta tão poderosa para implementar as funções de firmware.

Mas primeiro, vejamos o que é PSoC. PSoC é uma família de chipsets Cypress para implementar sistemas integrados. Famílias diferentes têm um núcleo de processador diferente (para PSoC 3 é MCS-51, para PSoC 4 é Cortex M0, para PSoC 5LP é Cortex M3 e para PSoC 6 são duas de uma vez: Cortex M0 + e Cortex M4) e um conjunto de lógica programável. Além disso, essa lógica não é puramente digital; há coisas analógicas lá. Além de um conjunto de diferentes ADCs, também existem comutadores analógicos. Você pode até conectar programaticamente as pernas através de circuitos analógicos, no entanto, a resistência do circuito será medida em quilogramas. Existem amplificadores operacionais dentro do PSoC que podem ser alternados programaticamente, o que significa que você pode construir diferentes blocos analógicos neles.

A propósito, os PSoCs podem ser alimentados por qualquer voltagem de 2,7 a 5,5 volts. Ou seja, você não precisa pensar em nenhum tipo de estabilizador com energia da bateria ou com USB.

Mas eu escrevi sobre coisas analógicas puramente para uma palavra vermelha. Agora vamos nos concentrar nas coisas digitais. A maioria dos controladores modernos possui unidades periféricas poderosas que fornecem uma enorme variedade de funções. Mas, na prática, em cada desenvolvimento de software específico, esses blocos não são totalmente utilizados, mas apenas parcialmente. E no PSoC, em vez de um monte de coisas boas, a lógica do programa é implementada, semelhante à lógica dos FPGAs clássicos. Dessa forma, é possível implementar exatamente os blocos necessários, incluindo-os nos modos necessários. E os recursos não devem ser gastos em modos não utilizados, dando-os para a implementação de algum tipo de coisas próprias.

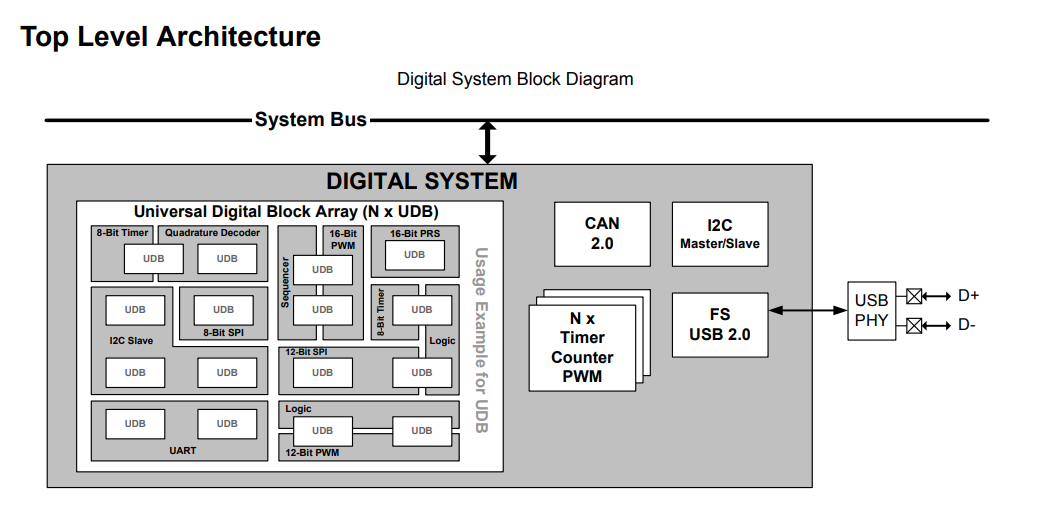

E aqui muitas vezes surgem alguns mal-entendidos. Muitos desenvolvedores estão acostumados ao fato de que existem dois tipos de circuitos integrados de lógica programável (FPGAs): CPLD e FPGA. Portanto, muitos que ouviram falar do PSoC acreditam que existe um tipo de CPLD-box que pode ser programado no Veriolg. De fato, sim e não. Um certo número de PLDs (sem "C", apenas PLDs) está realmente lá, e você pode realmente programá-los no Verilog. Mas, realmente, esses PLDs fazem parte dos blocos UDB. E é o UDB que é o principal elemento da lógica programável implementada no PSoC. Este bloco é extremamente original e oferece simplesmente as mais amplas oportunidades para o desenvolvedor. Considere a figura da documentação corporativa que explica a essência do uso de blocos UDB.

Como estudei tudo usando a família PSoC 5LP como exemplo, vou traduzir a documentação para ele. Mas antes de começar, direi algumas palavras sobre o preço desses controladores. Se você for ao Ali Express e olhar a tábua de pão para eles, terá uma sensação triste. Francamente falando, em comparação com STM32-DISCOVERY, eles ainda não são nada, mas em comparação com os protótipos STM32F103C8T6, eles são um pouco caros. Antes de tudo, isso se deve ao fato de que os modelos corporativos sempre não têm um, mas dois controladores. As funções JTAG são implementadas no PSoC 5LP, mesmo que o controlador de destino e o PSoC 4 (o último geralmente não possua uma porta USB).

Mas dividindo o preço por dois, ainda conseguimos que seja mais alto que o do STM32F103, que é semelhante no núcleo do processador. No entanto, se adicionarmos o CPLD mais simples ao mesmo STM32 do lado de fora, o preço total sairá a favor do PSoC. E adicionaremos as pernas perdidas à conexão desses dois casos (o PSoC tem todas as conexões internas). E também o preço de centímetros quadrados do tabuleiro. Portanto, se você precisar trabalhar apenas com o núcleo do processador, o PSoC realmente não será necessário. Se você precisar trazer alguma funcionalidade ao nível do firmware ou hardware, precisará do PSoC. Nele, o sistema sairá mais barato e fácil.

Na verdade, tenho uma ideia maníaca de tentar fazer suporte de hardware para o kernel do nosso RTOS MAX. Para fazer isso, estudei a metodologia para o desenvolvimento de aplicativos Bare Metal para o Altera V SoC (infelizmente, o recurso de arquitetura existe de tal forma que o sistema operacional pode ser mais lento, mas você não pode acelerá-lo - solicitações únicas ao hardware vêm com latência louca). Para isso, comecei a dominar o PSoC. Não cheguei ao overclock do kernel (existem apenas pensamentos gerais), mas gostei muito da ideia da programação UDB. Obviamente, agora estou interessado em levar essa idéia ao número máximo de programadores domésticos. Portanto, prosseguimos com a tradução da parte correspondente da documentação proprietária do Cypress no UDB. A numeração dos capítulos e figuras é mantida de acordo com o documento original.

O conteúdo geral do ciclo “UDB. O que é isso? "

Parte 1. Introdução. Pld. (Artigo atual)

Parte 2. Datapath.Parte 3. Datapath FIFO.Parte 4. Datapath ALU.Parte 5. Caminho de Dados. Pequenas coisas úteis.Parte 6. Módulo de gerenciamento e status.Parte 7. Módulo de controle de tempo e redefiniçãoParte 8. Endereçando UDBUDB. O que é isso? Parte 1

21. Blocos digitais universais

Neste capítulo, veremos como os UDBs (Universal Digital Blocks) permitem o desenvolvimento de funções periféricas digitais programáveis. A arquitetura UDB encontra um equilíbrio entre granularidade de configuração e implementação eficiente. Os UDBs consistem em uma combinação de lógica não comutada semelhante a uma matriz lógica programável (PLM, inglês PLD), lógica estruturada (autômatos operacionais, a seguir denominados Datapath) e um esquema de rastreamento flexível.

21.1 Recursos

- Para uma flexibilidade ideal, cada UDB contém os seguintes componentes:

• Caminho de dados de 8 bits baseado na ALU (Unidade Aritmética e Lógica, ALU) com repositório de instruções de 8 instruções, vários registradores e buffers FIFO;

• dois PLDs, cada um com 12 entradas, oito termos conjuntivos (Termos do Produto, PT) e quatro saídas de macrocélulas;

• registros de gerenciamento e status;

• módulos de relógio e redefinição. - O PSoC 5LP contém uma matriz de até 24 UDB de tamanho.

- Rastreamento flexível entre elementos da matriz UDB.

- Os elementos UDB podem ser divididos ou encadeados para criar funções maiores.

- Implementação flexível de várias funções digitais, incluindo temporizadores, contadores, moduladores de largura de pulso (incluindo PWM com um gerador de banda morta), UART, barramento I2C, barramento SPI e verificação / geração de CRC.

21.2 Diagrama de blocos

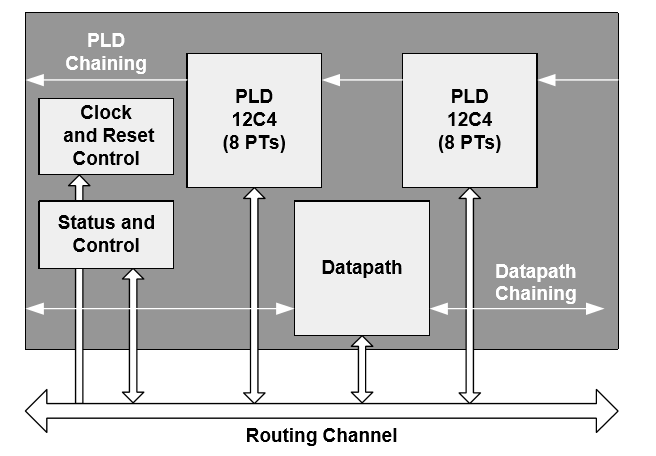

A Figura 21-1 mostra o UDB como uma construção que contém dois blocos lógicos básicos, PLD, Datapath e as funções de controle, status, relógio e redefinição.

Figura 21-1. Diagrama de blocos do UDB.

Figura 21-1. Diagrama de blocos do UDB.21.3 Como funciona

Os principais componentes do UDB são:

- PLD (2). Dados de recursos de rastreio são alimentados para as entradas desses blocos. Eles implementam lógica combinacional e captura de dados, o que permite implementar máquinas de estados finitos, controlar as operações do bloco Datapath, configurar condições de entrada e controlar saídas.

- Datapath. Este bloco contém ALU programável dinamicamente, quatro registros, dois buffers FIFO, comparadores e geração de condição.

- Gerenciamento e status (Status e Controle). Esses módulos fornecem um mecanismo para a interação dos microprogramas do processador central (CPU) e a sincronização com as operações UDB. Os registros de controle atuam nos elementos internos, e os registros de status lêem o estado dos elementos externos.

- Controle de relógio e redefinição Esses módulos fornecem seleção de tempo e habilitam, além de redefinir a seleção no UDB.

- Sinais de encadeamento. O PLD e o Datapath possuem sinais que permitem encadear blocos adjacentes em uma cadeia para criar funções de bits mais altos.

- Canal de rastreamento Os UDBs são conectados ao canal de rastreamento por meio de matrizes de comutação programáveis para comunicação entre blocos dentro do mesmo UDB e para comunicação com outros UDBs na matriz.

- Interface de barramento do sistema (Sysytem Bus Interface). Todos os registros e RAM em cada UDB são projetados no espaço de endereço do sistema e o acesso a eles pode ser obtido usando o processador central ou através do acesso direto à memória (English Direct Memory Access, DMA) na forma de 8 bits e 16 bits dados.

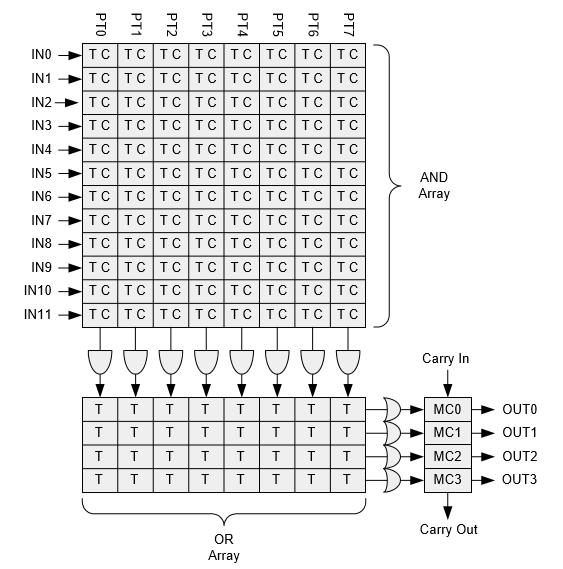

21.3.1 Pld

Cada UDB possui dois PLDs 12C4. Os blocos PLD mostrados na Figura 21-1 podem ser usados para implementar máquinas de estado, processar dados de E / S e criar lógica de tabela (Eng. Lookup Table, LUT). Além disso, o PLD pode ser configurado para executar funções aritméticas, definir a sequência do Datapath e gerar status. A lógica geral pode ser sintetizada e projetada em blocos PLD. Esta seção fornece uma visão geral da arquitetura do PLD.

O PLD possui 12 entradas que transmitem informações em 8 termos conjuntivos em um array AND. Em cada termo conjuntivo, você pode escolher uma entrada direta (verdadeira, T) ou inversa (complemento, C). A saída de termos conjuntivos vai para a entrada da matriz OR. A letra 'C' em 12C4 indica que os termos OR são constantes para todas as entradas e cada entrada OR pode obter acesso programático a qualquer termo conjuntivo. Essa estrutura fornece flexibilidade máxima e garante que todas as entradas e saídas possam ser movidas.

Figura 21-2. A estrutura do PLD 12C4.

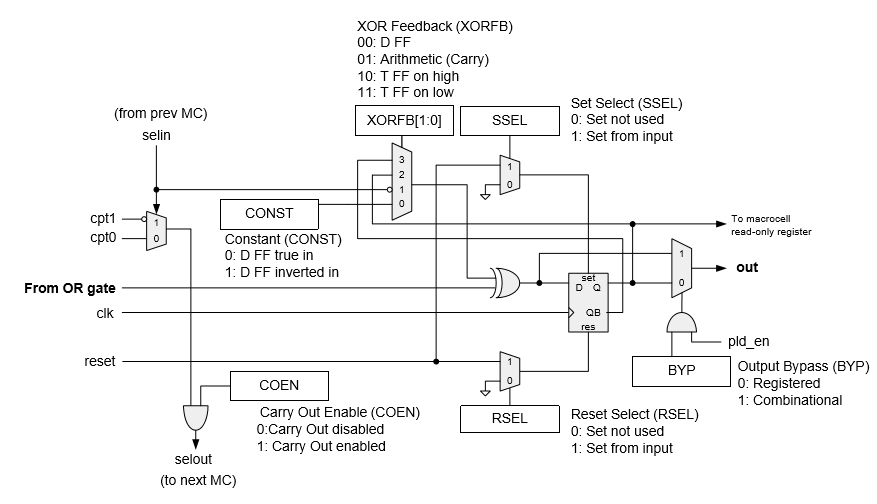

Figura 21-2. A estrutura do PLD 12C4.21.3.1.1 Macro PLD

A arquitetura das macrocélulas é mostrada na Figura 21-3. A saída controla a matriz de rastreio e pode ser travada ou Raman. Para travamento, é usado um gatilho D com entrada direta ou inversa ou um gatilho T com um nível de entrada alto ou baixo. O gatilho de saída pode ser configurado ou redefinido durante a inicialização ou de forma assíncrona durante a operação normal, por um sinal externo do canal de rastreamento.

Figura 21-3. Arquitetura de macrocélula.Registro de célula de macro PLD somente leitura

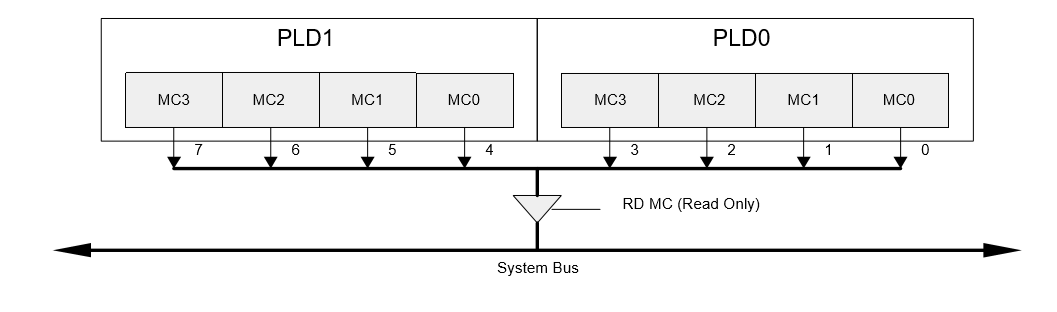

Figura 21-3. Arquitetura de macrocélula.Registro de célula de macro PLD somente leituraAlém de controlar a matriz de rastreamento, as saídas de macrocélulas dos dois PLDs são projetadas no espaço de endereço na forma de um registro somente leitura de 8 bits, que pode ser acessado usando a CPU ou o DMA.

Figura 21-4. O registro de macrocélula PLD somente leitura.

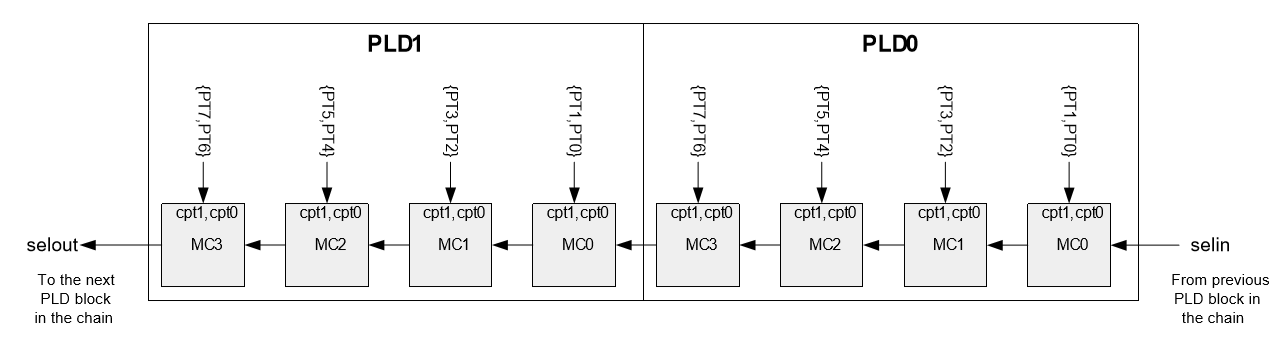

Figura 21-4. O registro de macrocélula PLD somente leitura.21.3.1.2 cadeia de hifenização PLD

Os PLDs são vinculados no endereçamento UDB. Como mostra a Figura 21-5, a entrada da cadeia de transporte de selina é encaminhada do UDB anterior para o circuito, através de cada macro célula em ambos os PLDs, depois é encaminhada para o próximo UDB como saída da cadeia de transporte de selagem. Para apoiar o posicionamento eficiente de funções aritméticas, são gerados termos conjuntivos especiais (PT), usados em macrocélulas juntamente com uma cadeia de hifenização.

Figura 21-5. Cadeia de hifenização do PLD e entradas especiais de termos conjuntivos.

Figura 21-5. Cadeia de hifenização do PLD e entradas especiais de termos conjuntivos.21.3.1.3 Configuração do PLD

Cada PLD aparece antes da CPU ou DMA na forma de RAM com acesso de 16 bits. A matriz AND possui 12 × 8 × 2 bits ou 24 bytes para programação, e a matriz OR possui 4 × 8 bits ou 4 bytes para programação. Além disso, cada célula de macro possui um byte de configuração, totalizando 32 bytes de configuração por PLD. Como cada UDB possui 2 PLDs, a configuração total de cada UDB é de 64 bytes.

Da próxima vez, consideraremos os Autômatos Operacionais (Datapaths).