Continuamos a traduzir a documentação proprietária do Cypress para blocos UDB. Além disso, tudo coincide muito bem. Para continuar o

artigo prático sobre UDB, você precisará usar o FIFO e, na parte teórica, chegamos à própria descrição deles. Portanto, começamos a estudá-los em detalhes.

O conteúdo geral do ciclo “UDB. O que é isso? "

Parte 1. Introdução. Pld.Parte 2. Datapath.Parte 3. Datapath FIFO. (Artigo atual)

Parte 4. Datapath ALU.Parte 5. Caminho de Dados. Pequenas coisas úteis.Parte 6. Módulo de gerenciamento e status.Parte 7. Módulo de controle de tempo e redefiniçãoParte 8. Endereçando UDB21.3.2.2 FIFO do Datapath

Modos e configurações FIFO

Cada buffer FIFO possui vários modos e configurações operacionais disponíveis:

Tabela 21-2. Modos e configurações FIFO.

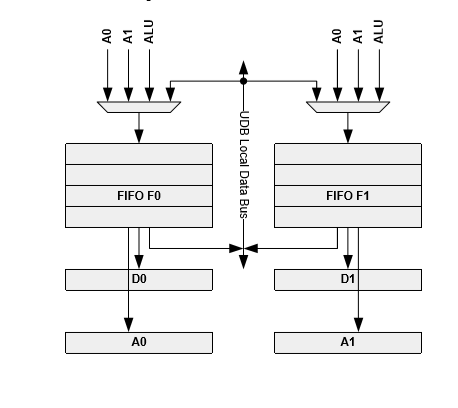

A Figura 21-7 mostra as opções de configuração possíveis para o par FIFO, dependendo dos modos de entrada / saída selecionados para cada um deles. Se um FIFO estiver no modo de entrada e outro no modo de saída, obteremos a configuração RX / TX. Um exemplo típico em que essa configuração é necessária é o controlador de barramento SPI. A configuração

Dual Capture (ambos os FIFOs estão configurados para saída) fornece captura independente dos pares A0 e A1 ou duas capturas independentes dos registros A0 ou A1. Finalmente, no modo

Dual Buffer (ambos na entrada), é possível usar um par de registradores ou dois registradores independentes para carregar ou comparar.

Figura 21-7. Configurações FIFO.

A Figura 21-8 mostra em detalhes as fontes e receptores do FIFO.

Figura 21-8. Fontes e receptores FIFO.

Quando o FIFO opera no modo de buffer de entrada, a fonte é o barramento do sistema e os receptores são os registros Dx e Ax. Ao trabalhar no modo de buffer de saída, as fontes são os registros Ax e ALU e o receptor é o barramento do sistema. A seleção do multiplexador é definida estaticamente no registro de configuração do UDB CFG15, conforme mostrado na tabela para F0_INSEL [1: 0] ou F1_INSEL [1: 0]:

Tabela 21-3. Um conjunto de multiplexadores FIFO no registro de configuração do UDB.

Status FIFO

Cada FIFO gera dois sinais de status, "barramento" e "bloco", que são transmitidos aos recursos de rastreio do UDB por meio do multiplexador de saída do Datapath. O status do barramento pode ser usado para interromper ou solicitar uma leitura / gravação de DMA ao FIFO. O estado "bloco" é destinado principalmente a passar o estado FIFO para entidades internas do UDB. a finalidade dos bits de status depende da direção configurada (Fx_INSEL [1: 0]) e dos bits de nível FIFO. Os bits de nível FIFO (Fx_LVL) são definidos no registro de Controle Auxiliar no espaço de registro de trabalho. As opções de status são mostradas na tabela a seguir:

Tabela 21-4. Opções de status FIFO.

Ilustração de trabalho FIFO

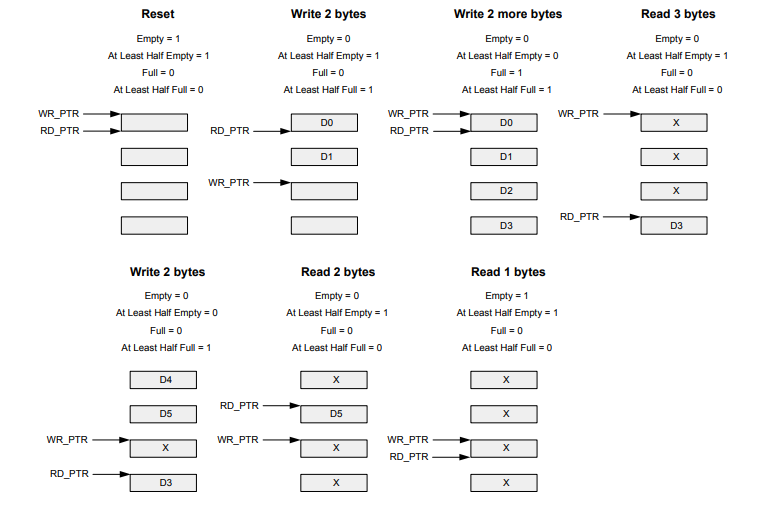

A Figura 21-9 mostra uma sequência típica de leitura e escrita, bem como a geração de status associados a essas operações. Na figura, a leitura e a escrita ocorrem em momentos diferentes, mas podem ser realizadas simultaneamente.

Figura 21-9 Operação dos receptores FIFO.

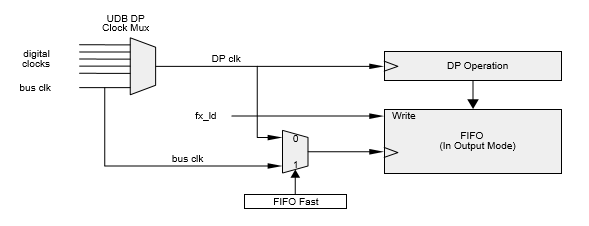

Modo rápido FIFO (FIFO RÁPIDO)

Quando o FIFO está no modo de buffer de saída, a operação de inicialização do FIFO normalmente usa a frequência do clock do Datapath selecionado para registrar o sinal de gravação. Como mostra a Figura 21-10, ao selecionar o modo rápido FIFO (FIFO FAST), você pode selecionar a frequência do barramento para esta operação específica. Quando usada em conjunto com o modo

Nível / Borda = Borda , essa operação reduz o atraso da transmissão da bateria para o FIFO do período do relógio do Datapath para o período do relógio do barramento, pois a frequência do barramento pode ser muito maior. Isso permite que a CPU ou o DMA leia o resultado FIFO recebido com um atraso mínimo.

Conforme mostrado na Figura 21-10, a operação de inicialização rápida é executada independentemente do relógio atual do Datapath, no entanto, o uso da velocidade do relógio do barramento pode aumentar o consumo de energia.

Figura 21-10. Receptores de configuração rápida FIFO.

Modo de gravação FIFO Edge / Level (diferencial / nível)

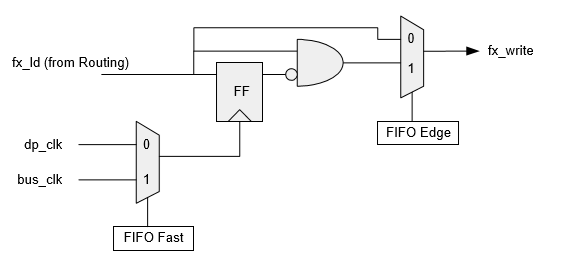

Existem dois modos de gravação no FIFO do Datapath. No primeiro modo, os dados são transferidos de forma síncrona das baterias para o FIFO. O sinal de controle desse registro (FX_LD) geralmente é gerado por uma máquina de estado ou por uma condição sincronizada com o relógio do Datapath. A gravação no FIFO será realizada em qualquer ciclo em que o sinal de controle de carga de entrada seja '1'. No segundo modo, o FIFO é usado para capturar os valores da bateria em resposta a uma margem positiva do sinal FX_LD. Nesse modo, o formato do sinal é arbitrário (no entanto, seu período deve ser igual a pelo menos um ciclo de relógio do Datapath). Um exemplo desse modo é capturar o valor da bateria usando a entrada do pé externo como gatilho. Uma limitação deste modo é que o parâmetro de entrada deve retornar ao valor '0' pelo menos um ciclo antes que outra diferença positiva seja detectada.

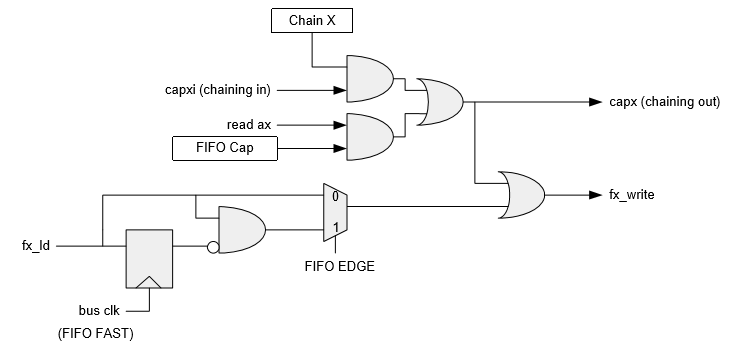

A Figura 21-11 mostra a implementação do modo de detecção diferencial na entrada FX_LD. O modo de ambos os FIFOs no UDB é controlado pelo mesmo bit, alternando esta opção. Observe que a detecção diferencial é cronometrada em uma frequência igual à frequência do FIFO selecionado.

Figura 21-11. Detecção diferencial para receptores de gravação FIFO internos.

Modo de captura de software FIFO

Um requisito comum e importante é permitir que a CPU e o DMA leiam de forma confiável o conteúdo da bateria durante a operação normal. Isso é feito usando a captura de software e ativado usando o bit de configuração FIFO Cap. Este bit se aplica a ambos os FIFOs no UDB, mas só funciona quando o FIFO está no modo de buffer de saída. Ao usar a captura de software, F0 deve ler de A0 e F1 de A1.

Como mostra a Figura 21-12, a leitura da bateria inicia a gravação no FIFO a partir da bateria. O sinal é vinculado em uma cadeia, de modo que a leitura de um byte específico captura ao mesmo tempo os valores da bateria de todos os UDBs da cadeia. Isso permite que o processador de 8 bits leia com êxito 16 bits ou mais ao mesmo tempo. Os dados retornados ao ler a bateria devem ser ignorados e o valor capturado pode ser lido imediatamente no FIFO.

O sinal FX_LD rastreado, que gera a carga FIFO, é enviado para o termo OR junto com o sinal de captura do programa. Quando a captura de hardware e software é usada ao mesmo tempo, o resultado pode ser imprevisível. Como regra, essas funções devem ser mutuamente exclusivas, no entanto, a captura de hardware e software pode ser usada simultaneamente nas seguintes condições:

- O modo de relógio de captura FIFO está definido como FIFO FAST.

- O modo de gravação FIFO está definido como FIFO EDGE.

Sob as condições descritas acima, as capturas de hardware e software funcionam essencialmente da mesma maneira e, durante qualquer ciclo de clock do barramento, qualquer um desses sinais pode desencadear uma captura.

Também é recomendável que você limpe o FIFO de destino no código do programa (registro ACTL) antes do início da captura do programa. Graças a isso, os indicadores de leitura e gravação FIFO serão configurados para um estado conhecido.

Figura 21-12. Configuração de captura de software.

Nota do tradutor:

Durante muito tempo, não consegui entender o significado desta seção. Por um longo tempo, tive certeza de que a seção foi escrita para o PSoC3, cujo núcleo de oito bits não pode acessar mais do que byte. Mas, ao criar a oitava parte da tradução , descobriu-se que, mesmo no PSoC5LP, para todo o núcleo do processador ARM de 32 bits, o acesso aos registros UDB em funcionamento pode ser realizado no modo de oito ou dezesseis bits. A julgar pelo documento, não mais. É aqui que a funcionalidade descrita é útil.

Bocados de controle FIFO

O registro do Controle Auxiliar, que pode ser usado para controlar o FIFO durante a operação normal, contém 4 bits.

Os bits FIFO0 CLR e FIFO1 CLR são usados para redefinir ou limpar FIFOs. Quando um desses bits recebe o valor '1', o FIFO associado é redefinido. O bit deve ser restaurado ao seu valor original ('0') para que o FIFO continue trabalhando. Se o valor do bit permanecer igual a um, o FIFO correspondente será desativado e funcionará como um buffer de byte único sem status. Os dados podem ser gravados no FIFO, os dados são imediatamente legíveis e podem ser substituídos a qualquer momento. A direção dos dados com os bits de configuração FX INSEL [1: 0] ainda pode ser definida.

Os bits FIFO0 LVL e FIFO1 LVL determinam o nível em que o FIFO armará o bit de status

"bus" (quando o barramento lê ou grava no FIFO). Ou seja, o status do

"barramento" depende da direção especificada, conforme mostrado na tabela abaixo.

Tabela 21-5. Bocados de controle de nível FIFO

Operação assíncrona FIFO

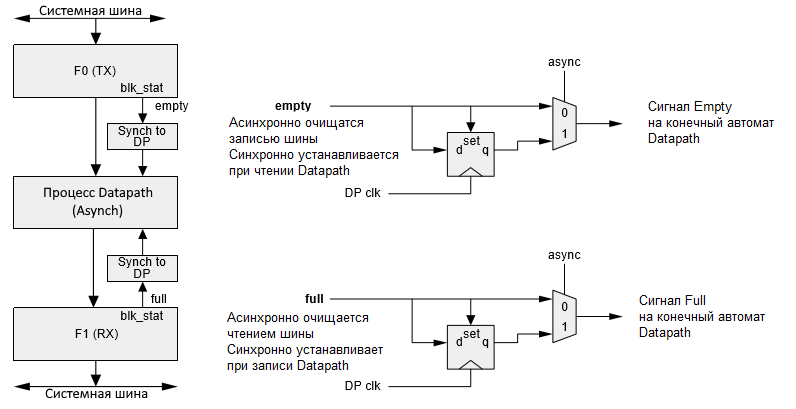

A Figura 21-13 mostra o princípio da operação assíncrona de FIFO. Como exemplo, imagine que F0 opere no modo buffer de entrada e F1 no modo buffer de saída, que é uma configuração típica dos registros TX e RX.

Figura 21-13. Operação FIFO assíncrona.

No lado TX, a máquina de estado Datapath usa o sinalizador

Vazio para determinar se existem bytes disponíveis para recebimento. O valor

Vazio é definido de forma síncrona com a máquina de estado Datapath e é limpo de forma assíncrona devido à gravação do barramento. Após a limpeza, o status é novamente sincronizado com a máquina de estado do Datapath.

No lado do RX, a máquina de estado do RX usa

Full para determinar se há espaço livre para gravar no FIFO. O valor

Total é configurado de forma síncrona com a máquina de estado Datapath e é limpo de forma assíncrona devido à leitura do barramento. Após a limpeza, o status é novamente sincronizado com a máquina de estado do Datapath.

Um bit FIFO ASYNCH é usado para habilitar esse método de sincronização; após a ativação, esse método é aplicado aos dois FIFOs.

Aplica-se apenas ao status do

bloco , pois é assumido que o status do

barramento é naturalmente sincronizado pelo processo de interrupção.

Tabela 21-6.

Bloquear opções de sincronização de status FIFO.

Excesso de FIFO durante a operação

Para a implementação segura de operações de leitura e gravação internas (Datapath) e externas (CPU ou DMA), devem ser utilizados sinais de status FIFO. Não há proteção integrada contra condições de esvaziamento e transbordamento. Se o FIFO estiver cheio e as operações de gravação subseqüentes forem executadas (estouro), os novos dados substituirão o início do FIFO (os dados que estão sendo produzidos no momento são os próximos na fila de leitura). Se o FIFO estiver vazio e as leituras subsequentes forem executadas (esvaziamento ou exaustão), o valor da leitura será indefinido. Os indicadores FIFO permanecem precisos, independentemente do fluxo insuficiente e insuficiente.

Inversão do Relógio FIFO

Cada FIFO possui um bit de controle Fx CK INV, responsável pela polaridade do relógio FIFO Em relação à polaridade do relógio Datapath. Por padrão, o FIFO trabalha com a mesma polaridade que o relógio do Datapath. Quando esse bit é 1, o FIFO opera com polaridade reversa em relação ao Datapath. Isso fornece suporte de protocolo para troca de dados em ambas as frentes, como SPI.

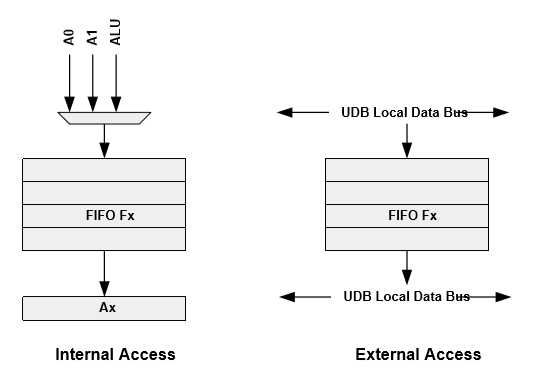

Controle FIFO dinâmico

Normalmente, os FIFOs são configurados estaticamente no modo de buffer de entrada ou no modo de buffer de saída. Como alternativa, cada FIFO pode ser configurado para operar em um modo no qual a direção é controlada dinamicamente (sob a influência de sinais externos). Um bit de configuração por FIFO (Fx DYN) é responsável por ativar este modo. A Figura 21-14 mostra as configurações disponíveis no modo dinâmico FIFO.

Figura 21-14. Modo FIFO dinâmico.

No modo de Acesso Interno, o Datapath pode ler e gravar no FIFO. Nesta configuração, para selecionar a fonte de operações de gravação no FIFO, os bits Fx INSEL devem ser definidos como 1. Fx INSEL = 0 (fonte do barramento da CPU) neste modo está incorreto, pode apenas assumir os valores 1, 2 ou 3 (A0, A1 ou ALU ) Vale ressaltar que a leitura tem acesso apenas à bateria apropriada, a direção dos registros de dados neste modo não está disponível.

No modo de acesso externo, a CPU ou o DMA pode ler ou gravar no FIFO.

A configuração alterna dinamicamente entre o acesso externo e interno, encaminhando sinais do Datapath. Para isso, os sinais de entrada Datapath d0_load e d1_load são usados. Vale ressaltar que no modo de controle dinâmico, d0_load e d1_load não estão disponíveis para seu uso normal ao carregar os registros D0 / D1 de F0 / F1. Os sinais Dx_load podem ser acionados por qualquer sinal de rastreamento, incluindo constantes.

Considere um exemplo no qual, começando com o acesso externo (dx_load == 1), a CPU ou o DMA pode gravar um ou mais bytes de dados no FIFO. Em seguida, ao alternar para o acesso interno (dx_load == 0), o Datapath pode executar operações nos dados. Depois disso, ao alternar para acesso externo, a CPU ou o DMA pode ler o resultado dos cálculos.

Como o Fx INSEL sempre deve ser 01, 10 ou 11 (A0, A1 ou ALU), que corresponde ao "modo de buffer de saída" durante a operação normal, os sinais de status FIFO têm as seguintes definições (dependendo do parâmetro Fx LVL):

Tabela 21-7. Status FIFO.

Como o Datapath e a CPU podem gravar e ler a partir de FIFOs, esses sinais não são mais considerados status de bloco e barramento. O sinal blk_stat é usado para o status de gravação e o sinal bus_stat para o status de leitura

21.3.2.3 Status FIFO

Existem quatro sinais de status FIFO, dois para cada FIFO: fifo0_bus_stat, fifo0_blk_stat, fifo1_bus_stat e fifo1_blk_stat. O significado desses sinais depende da direção do FIFO específico, que é determinado pela configuração estática. O status FIFO é descrito em detalhes na seção

21.3.2.2 FIFO do Datapath .

Na próxima parte, passaremos para a análise da Unidade Lógica Aritmética (ALU).