O tamanho das características dos transistores está diminuindo, apesar dos constantes rumores sobre a morte da lei de Moore e o fato de que a indústria está realmente próxima dos limites físicos da miniaturização (ou mesmo passou por eles com alguns truques inteligentes da tecnologia). A lei de Moore, no entanto, criou o apetite do usuário por inovação, difícil de lidar com a indústria. É por isso que os produtos microeletrônicos modernos não são apenas dimensionados para o tamanho dos recursos, mas também empregam vários outros recursos, geralmente ainda mais complicados do que o dimensionamento de chips.

Isenção de responsabilidade: Este artigo é uma tradução ligeiramente atualizada de minha própria peça publicada neste site aqui . Se você fala russo, pode verificar o original. Se você fala inglês, vale a pena notar que o inglês não é minha língua nativa, por isso ficarei muito agradecido pelo feedback, se você encontrar algo estranho no texto. Eu disse intencionalmente “produto microeletrônico” em vez de apenas “chip”, porque este artigo é sobre a tecnologia System in Package (SiP) que permite conectar muitos chips em um único pacote.

O termo Sistema no Pacote é muito menos popular que o do System on Chip (SoC), que é rotineiramente usado por todas as empresas de semicondutores e, por um bom motivo, quase todos os chips modernos são, de alguma forma, um sistema com muitas funções fundidas. Os tempos de chipsets abundantes se foram há muito, pois as vantagens do SoC são claras: menos pacotes no PCB, menos área (leia-se "mais barato"), menos capacitâncias e indutâncias parasitas (leia-se "mais rápido"), mais fáceis de implementar e usar, mais barato projetar e fabricar um único chip complexo do que um monte de outros mais específicos.

Mas nada é de graça, e os SoCs obviamente têm algumas desvantagens.

Primeiro, ao tentar juntar todas as peças, você corre o risco de ficar com um chip grande demais para caber em qualquer pacote ou, pior ainda, na janela do fotolitógrafo. A última restrição pode ser superada, mas quase sempre é irracionalmente cara (com as câmeras fotográficas sendo a exclusão mais notável).

Aqui está o sensor de imagem Kodak Kaf39000, que possui uma área de 2000 milímetros quadrados e usa pontos de máscara. O maior chip não costurado é o NVIDIA Volta de 815 milímetros quadrados, que é apenas 20 milímetros menor que o maior tamanho possível.

Segundo, quanto maior o chip, menor o rendimento, pois qualquer grão de poeira pode arruinar o seu dia. E adivinhe? Menor rendimento significa preço mais alto.

Terceiro, se o seu sistema contiver componentes heterogêneos, como núcleo do processador, DRAM e módulo de RF, combiná-los pode ser tecnologicamente impossível ou, novamente, excessivamente caro. Por exemplo, as células DRAM requerem capacitores específicos de alta densidade, e os circuitos de RF à base de silício podem ser piores do que seus equivalentes produzidos em vários materiais A3B5 (GaAs e curtidas). Mesmo uma combinação simples de processamento digital e condicionamento de sinal analógico no mesmo chip cria problemas significativos de ruído. E eu nem digo sobre o fato de que o ADC de 180 nm seria facilmente duas ordens de magnitude mais barato do que adicionar seu analógico de 14 nm ao chip MCU de 14 nm.

A combinação de todos os fatores acima levou à mudança de tendência de “vamos empacotar tudo em um único chip” para uma abordagem mais pragmática - e ao rápido desenvolvimento de várias tecnologias de embalagem.

Desempenho e rendimento

O primeiro exemplo que vem à mente é o renascimento recente da AMD, amplamente reconhecido como resultado de seu sucesso com sistemas com vários chips (também ajudado pelos problemas da Intel com rendimento em enormes chips de 10 nm).

Na foto acima está o Xeon de 28 núcleos da Intel. A área de chips desses processadores pode chegar a 456 milímetros quadrados, enquanto o tamanho máximo dos chips AMD é de apenas 200 milímetros quadrados para oito núcleos, seus muitos produtos principais são na verdade PCBs de duas camadas com até quatro dados dentro do pacote.

Esta figura mostra a PCB dentro dos processadores EPYC e Threadripper. No caso do Threadripper de 16 núcleos, ainda temos quatro chips, mas metade dos núcleos está desativada. Por que não usar apenas dois dados? Ou usar dados menores de quatro núcleos?

Primeiro, ter um único chip para todos os fins é obviamente muito mais barato do que projetar uma família.

Segundo, o mesmo vale para PCB, pacotes, etc. É mais fácil desativar peças excessivas do que projetar uma família de produtos.

Terceiro e provavelmente o mais importante, rendimento de 200 mm². O die ainda está longe de 100%, e desativar alguns núcleos já não funcionais é uma boa maneira de usar esses dados de defeito. A Intel faz o mesmo com seus dados de defeito, mas seus problemas de rendimento são mais graves devido à maior área de chip.

Aqui temos um exemplo ainda mais interessante, novamente da AMD. Fiji é uma GPU com memória de alta velocidade incorporada colocada dentro do pacote. Porque linhas de sinal mais curtas permitem atingir maior velocidade e, portanto, maior desempenho. Juntar fichas diferentes faz a diferença entre este e o exemplo anterior. A propósito, não há cinco dados dentro, como se pode sugerir, mas vinte e dois! Vejamos a seção transversal:

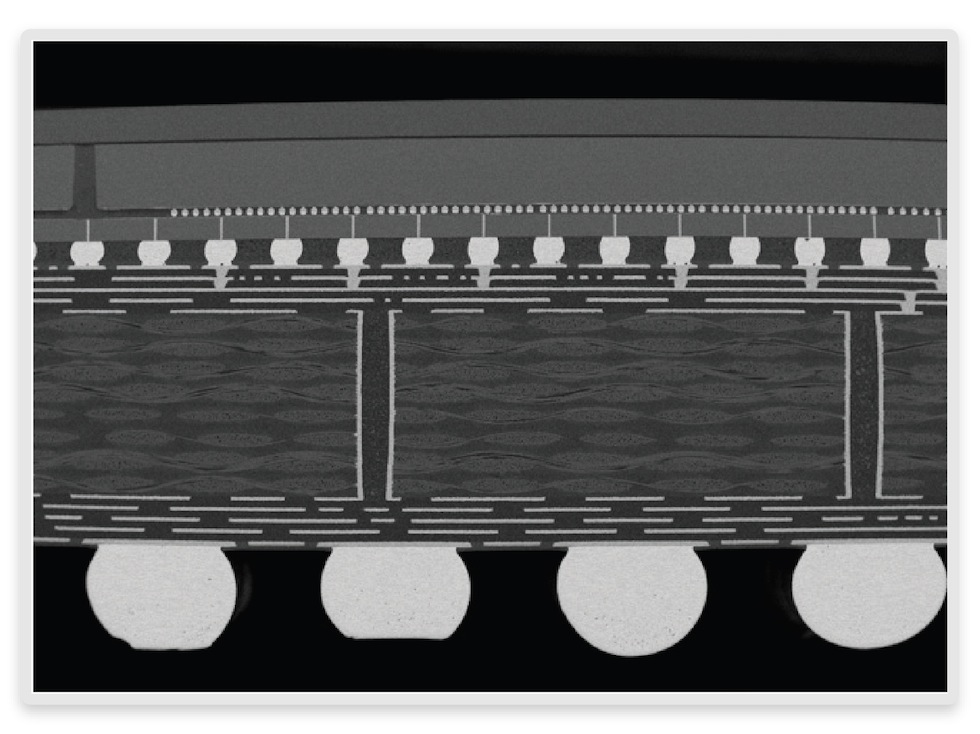

O nível superior é a própria GPU e uma pilha de quatro dados de memória conectados pelo chamado TSV (através de vias de silício) - conduzindo contatos perfurando todo o chip.

É assim que o TSV se parece.

A tecnologia TSV foi criada para a memória (não se pode ter muita memória, certo?), Mas está difundida agora, em parte graças à matriz sob a GPU e a memória.

O dado é chamado Silicon Interposer e é um substituto para PCB feito de silício com alguns (ou muitos) níveis de metalização e com TSV. Esses interposers existem para conectar vários chips acima deles com um substrato de pacote. A tecnologia de silício permite ter um tamanho de recurso menor do que qualquer PCB (até alguns mícrons), mas isso seria considerado muito simples e barato para uma tecnologia de silício. Tamanho de recurso menor e TSV significam melhor desempenho do que qualquer PCB pode oferecer, enquanto o rendimento será muito alto. Os intermediários (ao lado dos MEMS) são um mercado muito interessante e importante, especialmente porque também permitem a reutilização de equipamentos antigos para wafers de 200, 150 e até 100 mm.

A propósito, você pode identificar um erro na figura acima?Xilinx é outro pioneiro da integração 3D. Seus produtos são semelhantes aos da AMD (especialmente produtos com quantidades significativas de memória) e pelo mesmo motivo. O FPGA é um mercado em que a mudança antecipada para um nó de processo menor pode oferecer uma enorme vantagem sobre a concorrência. Diz-se que a diminuição do tamanho do chip três a quatro vezes proporciona aumento de duas ou três vezes nos estágios iniciais da vida útil do nó do processo, de 20% para mais da metade. Além disso, o FPGA é uma estrutura complexa, mas regular, quase ideal para investigar um amplo espectro de problemas de fabricação. Isso torna os fornecedores de FPGA os melhores clientes madrugadores para fabs, porque essa colaboração é proveitosa para ambas as partes. Fab recebe um ótimo chip de teste enquanto o fornecedor é capaz de superar a concorrência por alguns meses.

Aqui podemos ver um FPGA do Xilinx. A matriz superior é uma peça FPGA com toneladas de contatos de 40 micrômetros para a matriz intermediária denominada interposer. O mais baixo é um pacote, que possui uma dúzia de suas próprias camadas de metal.

Enorme Altera FPGA morre para a comparação. Quinhentos e sessenta milímetros quadrados! Se você vir engenheiros de processo por perto, cuide deles, existe o risco de derrame cardíaco.

Intel / Altera, obviamente, não apenas olha para o progresso dos concorrentes. Aqui está sua nova solução SiP chamada EMIB (Embedded Multi-Chip Interconnect Bridge). Um bom exemplo é o Intel Stratix 10 FPGA.

O EMIB conecta um dado FPGA (ainda apenas um), dados de memória e dados de periferia. O que é o EMIB? O interposer típico é muito mais barato que o dado “computacional” do mesmo tamanho que o interposer usa um nó de processo muito maior; no entanto, o interposer ainda é enorme e, portanto, é razoavelmente caro. Pode-se torná-lo menor?

A resposta da Intel é "sim, podemos". A idéia por trás do EMIB é usar alguns pequenos interposers em vez de um único grande e integrá-los ao pacote.

Aqui está uma pequena galeria de produtos criados com interposers. Veja como elas são enormes e como o Xilinx é criado a partir de peças.

Mais do que apenas desempenho

A figura abaixo é o ADC da Analog Devices e um diagrama esquemático. Parece o seu PCB típico, apenas menor, certo? Sim, é um PCB, mas o uso de dados simples em vez de pacotes permite diminuir os parasitas e sua influência no desempenho. O fato de toda a placa ter sido projetada em Analog Devices também adiciona uma camada de proteção contra erros de design do sistema e leva a uma melhor experiência do usuário.

Há também um truque: você vê dois dados empacotados um sobre o outro? O mais alto integra componentes ativos (transistores) do ADC e provavelmente um amplificador operacional duplo, enquanto o dado mais baixo é composto por passivos (resistores e capacitores). A colocação de passivos em um dado separado permite torná-los muito maiores e, portanto, diminuir a variação de parâmetros sem tornar o dado principal maior e mais caro. A diminuição da variação de parâmetros é importante para os circuitos analógicos, e é conseguida com baixo custo aqui.

Tudo poderia ser feito em uma única matriz (e geralmente é feito, especialmente em ADCs incorporados), mas essa matriz será maior (o que poderia significar "mais caro" e "com menor rendimento"), e a tecnologia deve suportar todos os opções necessárias (o que também significa "mais caro" devido ao maior número de máscaras). Além disso, quando você combina muitos blocos heterogêneos no mesmo chip, precisa lidar com a influência cruzada deles. A influência do ruído digital nas partes analógicas é provavelmente a mais importante, mas não a única.

Funcionalidade adicional do pacote

Como vimos anteriormente, as embalagens podem tornar o produto mais barato e até melhorá-lo. Mas e se usarmos o pacote como uma parte significativa do produto?

A Intel implementou o chamado FIVR (Fully Integrated Voltage Regulator) em seus microprocessadores Haswell. O objetivo do FIVR é converter uma tensão de entrada relativamente alta (1,8 V) em tensão de alimentação de núcleo baixa e controlável em tempo real. Os componentes ativos estão no chip, enquanto os passivos (capacitores e indutâncias) são incorporados ao pacote do processador.

A indutância integrada é uma dor de cabeça para os projetistas de chips, porque é ruim, grande e com baixa indutância. É usado em chips de radiofrequência, mas quase não há possibilidade de transferência de energia. A Intel resolveu o problema integrando dezenas de pequenos indutores no pacote do processador. Esses indutores estão trabalhando a 160 MHz sem núcleos ferromagnéticos. Ao fazer isso, a Intel simplificou significativamente os requisitos de fornecimento para o dispositivo.

No entanto, a Intel acabou com o FIVR e voltou à abordagem de fornecimento mais tradicional para as novas gerações. Havia alguns rumores de que o FIVR pode estar de volta, mas no final eram apenas rumores.

Uma das outras opções para a integração de passivos na embalagem é a LTCC (cerâmica com cofragem a baixa temperatura). Existem algumas limitações e problemas (como valores nominais limitados e precisão), mas essa tecnologia é ativamente desenvolvida. O pacote LTCC multicamada é assim:

Todos os tipos de componentes passivos são representados aqui, até dissipadores de calor de metal (é um pacote para IC de potência de RF). Pode-se dizer que não é apenas um pacote, mas uma mistura de pacote e PCB de cerâmica, essas coisas são muito populares para circuitos de RF e relativamente baratas em pequenas quantidades.

O que mais?

Existem muitas aplicações em potencial para sistemas em pacote, e é impossível listar todas elas. Também é importante notar que eles são significativamente mais baratos que os novos nós de processo, o que impulsiona sua atratividade comercial.

Os sistemas optoeletrônicos são o último, mas não menos importante, exemplo para este artigo. A capacidade de combinar receptor / transmissor óptico (geralmente construído em semicondutor composto) com chips de controle e fornecimento de silício é muito promissora. A figura abaixo mostra um protótipo de link óptico de 400 Gbit / s (e 1 Tbit / s é prometido para o futuro) projetado no IMEC.

Existem também inúmeras outras aplicações, como interpositores com capilares integrados para refrigeração a água (não apenas para jogos e mineração, mas também para interruptores e lasers), MEMS integrado e apenas Deus sabe o que mais. E, obviamente, não podemos escapar da onipresente Internet das Coisas, onde o tamanho pequeno, as baixas perdas e a capacidade de integrar blocos de rádio e computadores são de extrema importância.

Acredita-se que o pacote de chips seja o próximo grande passo na microeletrônica por muitos, e provavelmente veremos muitas idéias brilhantes no futuro próximo.