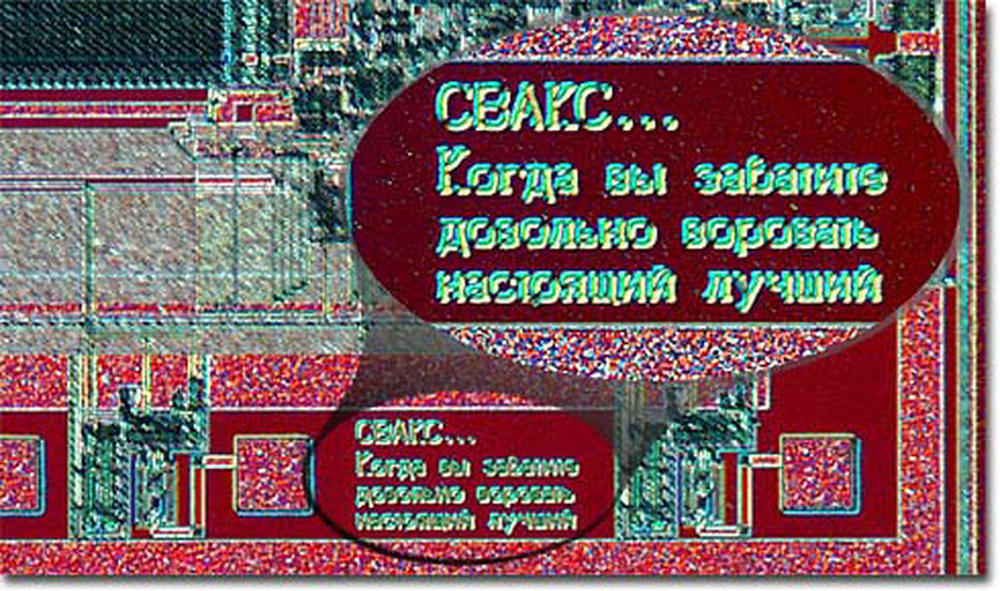

"CVAX - quando você rouba muito bem".

"CVAX - quando você rouba muito bem".A inscrição deixada pelos engenheiros americanos para colegas soviéticos na topologia do microprocessador.

A engenharia reversa de microchips é uma dor de cabeça para os fabricantes desde os primeiros anos de existência da microeletrônica. Todos os eletrônicos soviéticos em um ponto foram construídos sobre ele, e agora eles estão fazendo o mesmo no Império Celestial, e não apenas nele, em uma escala muito maior. De fato, a engenharia reversa é absolutamente legal nos EUA, na União Européia e em muitos outros lugares, com o objetivo (cito a lei americana) de "ensinar, analisar ou avaliar os conceitos ou técnicas executadas no trabalho ou circuito da máscara".

Os usos legais mais comuns para engenharia reversa são os tribunais de patentes e licenciados. A espionagem industrial também é comum, especialmente porque os circuitos elétricos (especialmente os analógicos) são frequentemente propriedade intelectual essencial e raramente patenteados - apenas para evitar a divulgação de propriedade intelectual e a participação em tribunais de patentes como acusador. Obviamente, em uma situação em que você precisa proteger sua propriedade intelectual sem patentear, desenvolvedores e fabricantes estão tentando encontrar maneiras de impedir a cópia de seus desenvolvimentos.

Outra área não menos importante (ou ainda mais) importante para proteger os microchips da engenharia reversa é garantir a segurança das informações armazenadas na memória. Essas informações podem ser tanto o firmware FPGA (que é, novamente, a propriedade intelectual do desenvolvedor), como, por exemplo, um código PIN de um cartão bancário ou uma chave de criptografia para uma unidade flash segura. Quanto mais informações valiosas confiarem no mundo à nossa volta, mais importante será proteger essas informações em todos os níveis dos sistemas de processamento, e o nível de hardware não será exceção.

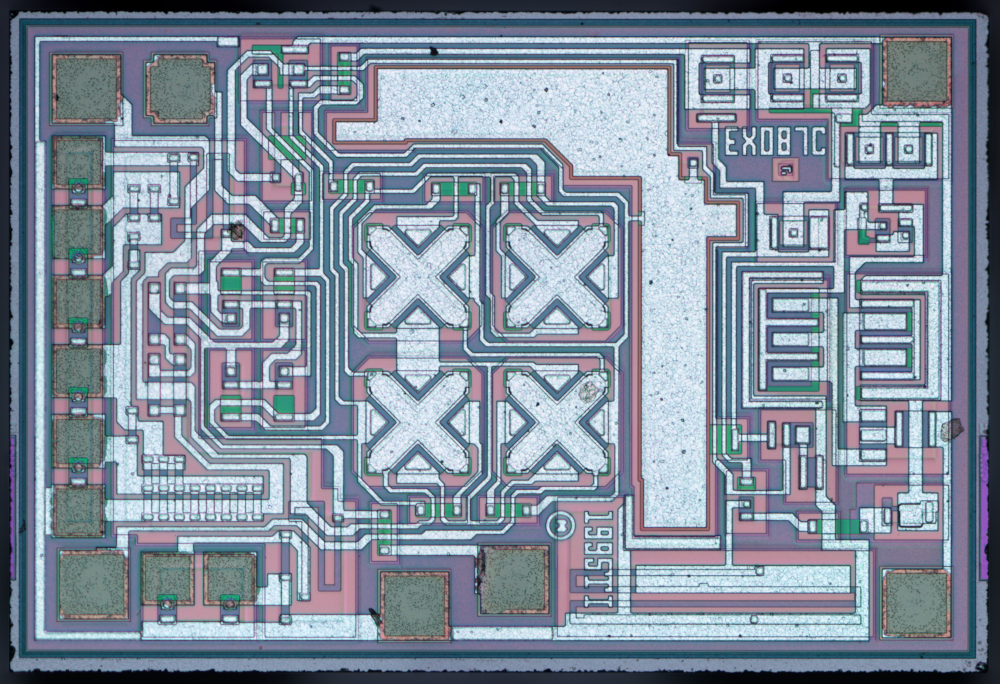

Primeiras coisas primeiro: uma coisa importante a entender. Falando sobre engenharia reversa e proteção contra cópia de dados, é necessário entender que não existem métodos absolutamente estáveis de proteção, e tudo o que é real é tornar o processo tão longo e / ou caro que se torne economicamente inconveniente.Muitos anos atrás, o trabalho de um engenheiro reverso ou de um pirata microeletrônico era muito mais fácil do que agora. Veja, por exemplo, esta foto (graças ao

BarsMonster por nossa infância feliz e boas fotos): com uma compreensão básica da tecnologia, restaurar um circuito elétrico a partir dele é uma questão de várias horas.

Figura 2. Um instantâneo da topologia do OPA134PA op-amp. Fonte - zeptobars.comAqui , a propósito, há um exemplo de engenharia reversa do chip TL431 feito por Ken Shirriff a partir de fotografias do BarsMonster. E aqui está a tradução para o russo. O blog de Ken tem muitas coisas legais se você estiver interessado no tópico de engenharia reversa amadora.E aqui (com cuidado, tráfego!) Há um relatório da engenharia reversa do chip Zilog Z80-CTC, feito em 1979, quase imediatamente após o lançamento do chip. Agora, este é um documento histórico único e, em seguida, foram informações de enorme valor comercial e obtidas (a julgar por várias referências a padrões militares), provavelmente no processo de certificação de um microcircuito para aplicações especiais.

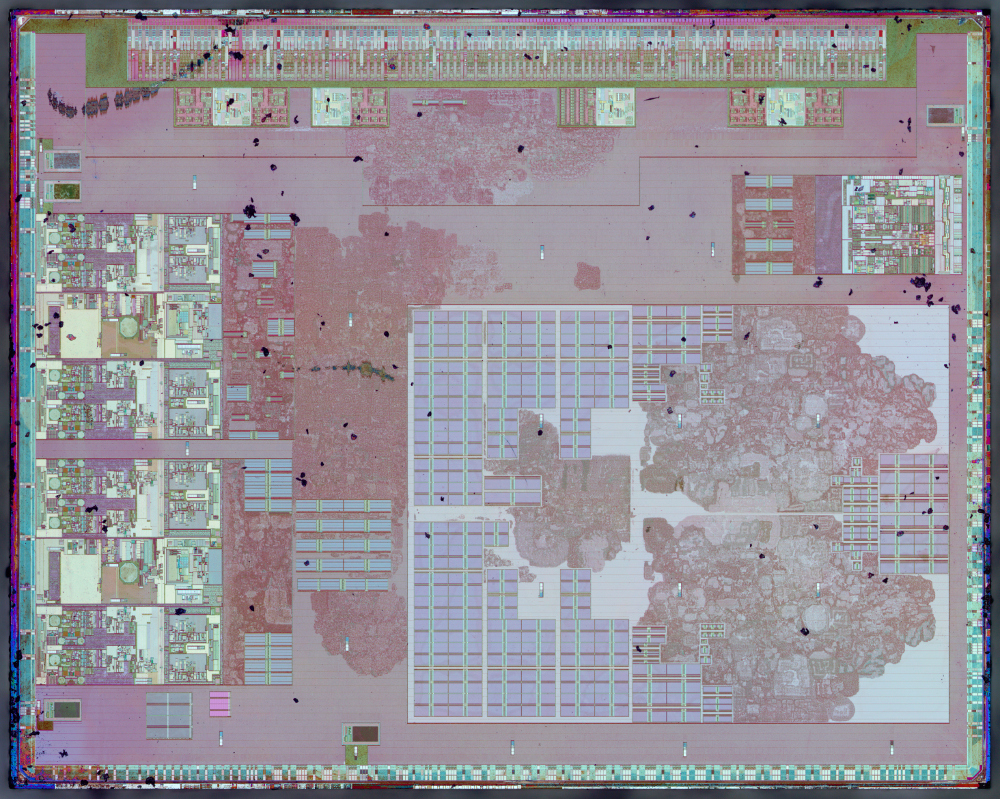

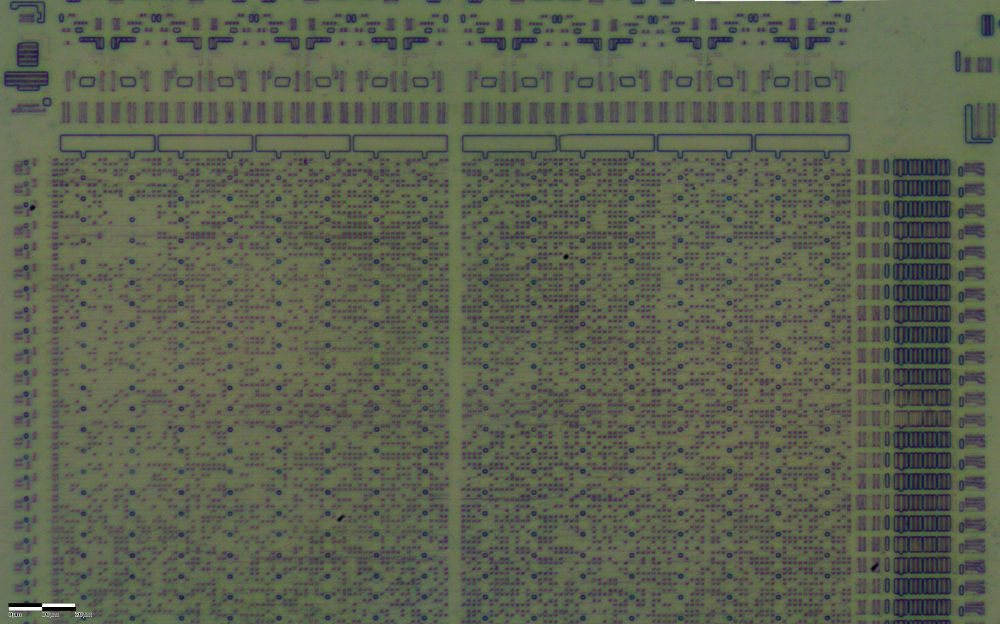

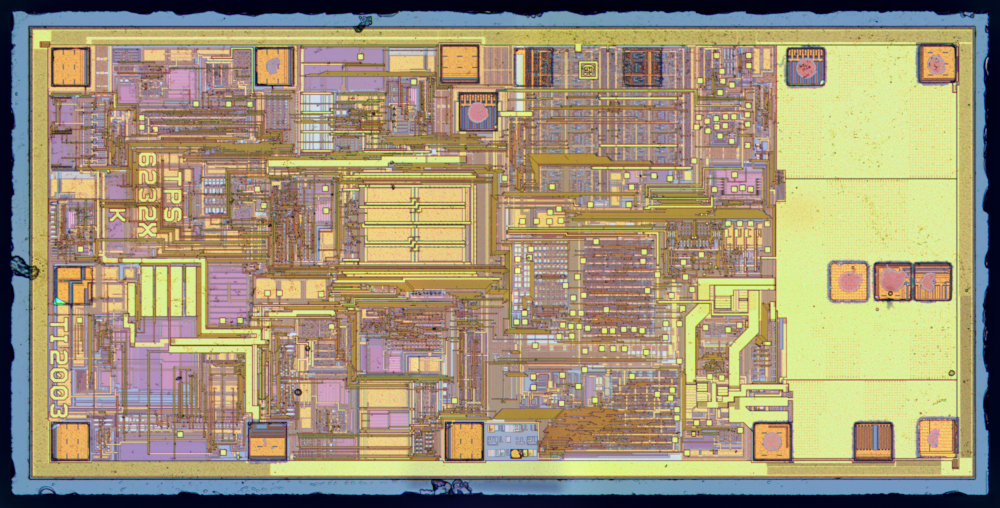

Figura 2. Um instantâneo da topologia do OPA134PA op-amp. Fonte - zeptobars.comAqui , a propósito, há um exemplo de engenharia reversa do chip TL431 feito por Ken Shirriff a partir de fotografias do BarsMonster. E aqui está a tradução para o russo. O blog de Ken tem muitas coisas legais se você estiver interessado no tópico de engenharia reversa amadora.E aqui (com cuidado, tráfego!) Há um relatório da engenharia reversa do chip Zilog Z80-CTC, feito em 1979, quase imediatamente após o lançamento do chip. Agora, este é um documento histórico único e, em seguida, foram informações de enorme valor comercial e obtidas (a julgar por várias referências a padrões militares), provavelmente no processo de certificação de um microcircuito para aplicações especiais.Mas vivemos em 2019, e não em 1979, e agora reverter o esquema completo de um microprocessador Intel novo é uma questão de muitos meses ou anos, mesmo com um bom nível de automação do processo (sem mencionar o fato de mesmo remover a topologia com os padrões de design em uma resolução aceitável 14 -10-7 nm é uma tarefa muito difícil). O que é a Intel? Compare a quantidade de trabalho em engenharia reversa ou análise do amplificador da imagem acima e do processador Baikal-T1, realizado de acordo com o processo de fabricação de 28 nm muito popular e relativamente acessível. A engenharia reversa total de produtos tão grandes é extremamente rara, geralmente é interessante observar alguns blocos específicos e relativamente pequenos. Por exemplo, para descobrir se eles violam sua patente ou comparar sua decisão com os produtos dos concorrentes e tentar entender por que é melhor ou pior. Ou, para descobrir, os próprios desenvolvedores de chips implementaram essa ou aquela funcionalidade ou pegaram emprestado seu bloco de IP.

Figura 3. Um instantâneo da topologia do processador Baikal-T1. Fonte - zeptobars.com

Figura 3. Um instantâneo da topologia do processador Baikal-T1. Fonte - zeptobars.comAqui vamos para a próxima parte importante da história da engenharia reversa. Nos tempos antigos, todo o chip era desenvolvido do começo ao fim em uma empresa, às vezes até pelas forças de uma equipe muito pequena ou por um solitário brilhante como Bob Widlar. Os microcircuitos modernos estão cheios de blocos de IP, cuja venda e compra é um mercado enorme, que também possui controle de direitos autorais, espionagem industrial e pirataria. Portanto, é possível e necessário analisar o problema da proteção contra cópias não autorizadas, não apenas do ponto de vista do desenvolvedor do produto final, mas também do ponto de vista do desenvolvedor de IP, para quem o desenvolvedor do produto também pode ser um pirata.

No caso de hackers, a estrutura interna do invasor geralmente não é interessante para o recebimento de dados e a engenharia reversa parcial é realizada (se houver) para encontrar vulnerabilidades e explorar essas vulnerabilidades, por meio de conexão direta ou usando outros métodos. A tarefa do desenvolvedor contra hackers é impedir o uso de pontos potencialmente fracos e, se necessário, destruir dados confidenciais ao tentar invadir.

PESSOAS ATUAIS

Para começar, vamos descobrir quem pode proteger o design do chip disso. As seguintes entidades estão envolvidas na cadeia, da ideia à aplicação, tendo diferentes tipos de acesso a informações sobre o conteúdo do microcircuito.

- Desenvolvedor de bloco de IP. Possui todas as informações, todos os arquivos necessários, métodos de medição, etc. etc.

- Desenvolvedor de chips. No caso do Soft IP, o Verilog / VHDL possui um código de bloco e, no caso do Hard IP, pode ter uma topologia ou uma caixa preta. Se houver peças programáveis ou de software na unidade, ela também terá acesso a elas.

- Fábrica Tem acesso aos arquivos de topologia GDSII, mas não tem acesso à parte do chip dependente de software (por exemplo, ao firmware PROM).

- Embalagem e teste de produção. Ele tem acesso ao chip, além de testar métodos e placas de firmware para memória programável única. Raramente alguém os defende intencionalmente, mas eles devem estar na lista, porque alguns dos métodos adequados para a proteção da fábrica não funcionam contra eles.

- Concorrente / cracker. Ele tem acesso apenas ao produto final e à documentação do usuário.

No caso mais simples, o projetista de chips (2) deseja se proteger da cópia por um concorrente (5) ou fabricar um chip com memória protegida contra leitura não autorizada. Em um pouco mais complicado, o desenvolvedor de IP (1) deseja garantir que esteja em conformidade com o chip (2) do contrato de licença. Também acontece que o desenvolvedor do chip (2) não confia na fábrica (3) e suspeita que possa gerar falsificações no turno da noite.

Escrevi em detalhes sobre o que é IP em circuitos integrados há algum tempo, então não repetirei este artigo. Também há um pouco sobre como os desenvolvedores de IP protegem sua propriedade intelectual. Em resumo, para proteger a topologia, a fábrica geralmente participa como um terceiro, e o comprador não recebe a topologia adequadamente, e técnicas de ofuscação semelhantes à ofuscação de qualquer outro código são usadas para proteger o código Verilog.FERRAMENTAS

Quais ferramentas de análise de microchips existem? O primeiro nível é um pouco de ácido para abrir primeiro a caixa do microcircuito e depois remover as camadas uma a uma, e um microscópio óptico regular com uma câmera. É barato, é fácil trabalhar com eles e, para a análise de circuitos simples feitos com as tecnologias mais recentes, isso é o bastante.

Para esquemas maiores, existem sistemas CAD especiais que permitem, de uma forma ou de outra, automatizar a restauração de dados da topologia - fornecendo ao engenheiro reverso uma interface mais conveniente para o trabalho do que apenas desenhar linhas em um editor gráfico. A automação também é simplificada pelo fato de que todos os circuitos digitais modernos são construídos a partir de bibliotecas, e depois dos elementos da biblioteca de engenharia reversa para montar um circuito é uma questão de tempo (ou poder de processamento disponível).

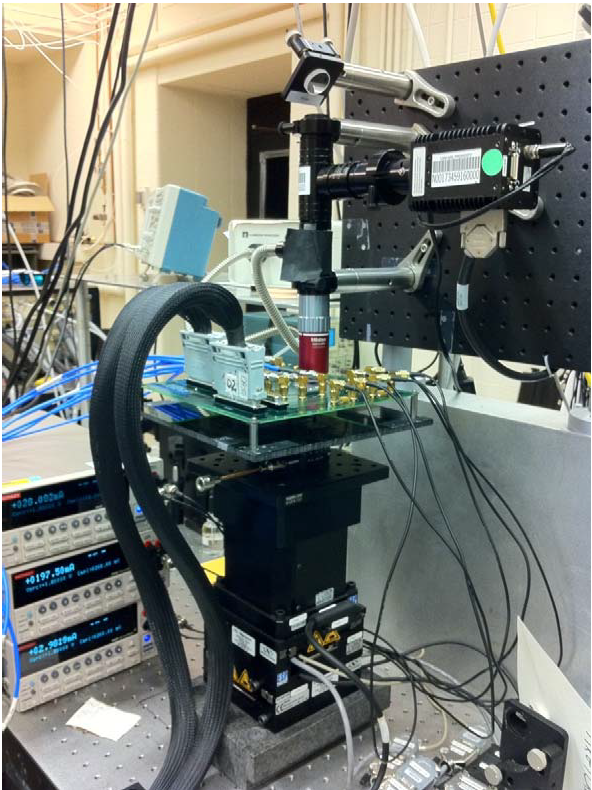

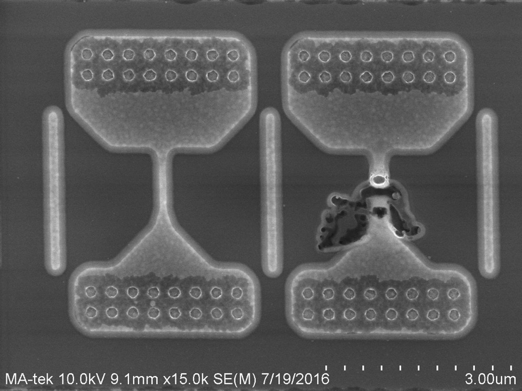

O próximo nível, inacessível para amadores, mas presente em laboratórios especializados, é um microscópio eletrônico de varredura (MEV). Ele usa um feixe de elétrons focado em vez de um feixe de luz. A resolução SEM pode ir até 1 nm e até um pouco menor, o que é suficiente para analisar qualquer circuito integrado moderno.

O FIB é um análogo do SEM, usando apenas um feixe de íons mais pesados em vez de um feixe de elétrons. Na verdade, o FIB é um feixe de íons focado. A principal diferença entre FIB e SEM é que, com sua ajuda, você pode não apenas analisar o microcircuito, mas também modificá-lo, por exemplo, fazer cortes (para ver a seção transversal do microcircuito ou remover uma peça) ou material de pulverização (para criar uma conexão lá onde não está). Os FIBs são amplamente utilizados pelos desenvolvedores e fabricantes de microcircuitos para trabalhar com amostras de teste, porque leva muito tempo para corrigir o erro ao usá-lo, mas ainda é muito mais rápido e mais barato do que reiniciar um lote experimental. Para um engenheiro reverso, essa também é uma maneira única de acessar as partes do cristal que, de acordo com a intenção do desenvolvedor, não devem estar disponíveis. E, ao projetar um chip protegido contra hackers, isso também deve ser lembrado.

Figura 4. Seção transversal de um microcircuito feito usando FIB. Fonte - SERESSA-2015 (com cuidado, muito tráfego em pdf a partir do link).

Figura 4. Seção transversal de um microcircuito feito usando FIB. Fonte - SERESSA-2015 (com cuidado, muito tráfego em pdf a partir do link). Figura 5. Feito pela modificação FIB do chip, alterando várias conexões.

Figura 5. Feito pela modificação FIB do chip, alterando várias conexões.Outra ferramenta indispensável para um engenheiro reverso é um conjunto de lasers. Os fãs podem usar lasers poderosos com os quais podem abrir microcircuitos em caixas de plástico e obter acesso ao cristal. Para lasers profissionais, dependendo do comprimento de onda, algumas partes do design do microcircuito podem ser transparentes e outras não. Isso permite que você use um laser, por exemplo, para abrir com precisão a passivação e o isolamento, para que mais tarde você possa se unir convenientemente à linha de metal sem correr o risco de causar um curto-circuito com seus vizinhos. Outros parâmetros permitem cortar metal ou queimar transistores individuais. O terceiro é induzir corrente nos transistores, alternando células de cache ou algum tipo de linha lógica. A última opção é universalmente usada como uma simulação barata dos efeitos de partículas carregadas pesadas, mas, em princípio, o mau funcionamento de um microcircuito em funcionamento também pode ser útil para comprometer as informações nele contidas. Por exemplo, pode ser interessante reescrever algum sinalizador no arquivo de registro ou corrigir um pouco a operação do gerador de números aleatórios.

Figura 6. Aparência do laser para estudar o efeito de falhas únicas em microcircuitos. Fonte - SERESSA-2015.

Figura 6. Aparência do laser para estudar o efeito de falhas únicas em microcircuitos. Fonte - SERESSA-2015. Figura 7. Um exemplo de sensibilidade de uma parte de um microcircuito a uma única falha e falha obtida usando um cartão de laser. Fonte - SERESSA-2015.

Figura 7. Um exemplo de sensibilidade de uma parte de um microcircuito a uma única falha e falha obtida usando um cartão de laser. Fonte - SERESSA-2015.Nos laboratórios avançados de engenharia reversa, você pode encontrar muitas outras ferramentas interessantes; por exemplo, um sinal digital de várias dezenas de MHz pode ser monitorado em tempo real, colocando um pequeno pedaço de niobato de lítio na linha correspondente e iluminando-o novamente com um laser.

CASO 1: FÁBRICA IRREGÁVEL

Qual poderia ser o motivo para não confiar na fábrica onde você faz seus cristais? Em um mundo ideal, é claro, você não se envolverá com uma fábrica em que não confia, mas às vezes considerações comerciais o obrigam a correr riscos. Pode ser minimizado de duas maneiras principais:

- A chamada fabricação dividida ou, de maneira simples, a produção em duas fábricas. Mas não em paralelo (como normalmente é feito para minimizar o risco de escassez em caso de atrasos imprevistos na produção), mas parte das operações em uma fábrica e parte em outra. Isso é bastante inconveniente para todos os participantes do processo (e certamente nem todas as fábricas concordam com isso), mas isso forçará a fábrica não confiável a pelo menos reverter o restante do design do chip e fazer as máscaras ausentes por conta própria. (o que, idealmente, deve fazer com que o jogo não valha a pena). A principal desvantagem dessa abordagem é que as camadas superiores do chip são metalizadas, o que torna a engenharia reversa bastante simples. A fabricação dividida, no entanto, pode ser realmente eficaz em combinação com algum conhecimento tecnológico em metais, que uma fábrica não confiável não é capaz de reproduzir. Por exemplo, se a segunda fábrica de sua escolha souber criar memória não volátil (MRAM, memristors ou algo assim) na camada superior de metalização, sem a qual todo o design perde seu significado.

- Se você não possui nenhum conhecimento tecnológico, a maneira mais simples e confiável é tornar o chip sem sentido sem mais programação. Blocos programáveis podem ser feitos de forma independente usando a memória de configuração ou na forma de um bloco baseado em um FPGA incorporado (existem esses IPs no mercado). A memória de configuração como uma forma de proteção permite que você tenha certeza de que a fábrica não pode apenas pegar e produzir seu chip ignorando você. Mas você pode ler a memória de configuração, certo? Sim, mas a presença de memória de configuração força uma fábrica não confiável, em vez de uma maneira simples de aumentar os volumes de produção, a fazer a mesma engenharia reversa que todos os outros atacantes.

Separadamente, observo que os dois métodos descritos de proteção contra uma fábrica não confiável ajudam contra cópias não autorizadas, mas não são salvos de "favoritos" populares em círculos estreitos. Além disso, um pouco mais adiante, falarei sobre como marcar a topologia por nós mesmos.

CASO 2: PROTEÇÃO DE MEMÓRIA

A presença de blocos programáveis e memória de configuração no chip é um atributo quase indispensável de qualquer projeto moderno, tanto digital quanto analógico. Com uma diminuição nos padrões de design, a propagação de parâmetros de chip para chip aumenta e o ajuste digital é a maneira mais fácil e confiável de superá-lo. E os circuitos digitais (por exemplo, microcontroladores) geralmente armazenam dados diretamente no chip e podem ter uma estrutura de memória em vários níveis, cujas partes diferentes têm níveis diferentes de acesso e proteção. Portanto, parece lógico usar primeiro a ferramenta que já temos para aumentar a segurança e a resistência a rachaduras e, em segundo lugar, a idéia de pensar cuidadosamente sobre que tipo de memória usar.

Firmware com conexões metálicas (Mask ROM). Normalmente, parece a presença ou ausência de contato entre duas linhas de metal, um pouco menos frequentemente - como a presença ou ausência de um transistor entre elas. O mais carvalho é usado em cristais de matriz base (BMC) - não apenas na indústria de defesa antiga, como você pode pensar, mas também em soluções bastante modernas, por exemplo, em chips auxiliares nos processadores Xeon. Além disso, usando essa memória, são feitas famílias de microcircuitos (principalmente microcontroladores), porque piscar a memória na fábrica trocando uma máscara é mais barato que o firmware universal de cada cristal produzido em uma placa ou em um caso. A ROM da máscara lê com muita facilidade com um microscópio e gravação precisa. Em casa, você pode lidar com isso.

Figura 8. Firmware da ROM com interconexões metálicas em um chip FTDI FT232RL falso. Fonte - zeptobars.com

Figura 8. Firmware da ROM com interconexões metálicas em um chip FTDI FT232RL falso. Fonte - zeptobars.com

Também deve ser observado aqui que é possível armazenar memória flash não apenas com uma camada de contatos entre metais, mas também com a presença e ausência de metal (fácil de ler óptico), a presença ou ausência de dopagem (fácil de ler opticamente) ou, por exemplo, a tensão limiar de um transistor controlado pelo nível de dopagem (mal) leia opticamente). Portanto, em princípio, a máscara ROM não tem tudo perdido se você realmente deseja ocultar seu conteúdo.

Memória em jumpers esgotados (Fuse ROM). Ele permite uma gravação (incluindo a gravação pelo usuário no dispositivo finalizado) e um número ilimitado de leituras; é muito simples de fabricar e programar e, portanto, popular para todos os tipos de memória de configuração e firmware.

Figura 9. Dois estados da ROM do fusível. Fonte - semiengineering.com

Figura 9. Dois estados da ROM do fusível. Fonte - semiengineering.comComo você pode ver, o estado de um jumper fusível comum (Fuse) é muito fácil de ver através de um microscópio, ou seja, é simplesmente impossível se proteger de abrir um cristal com ele. Bem, além de tudo o mais, o jumper clássico queimado é bastante grande (vários mícrons quadrados) e, portanto, não é adequado para grandes quantidades de memória.

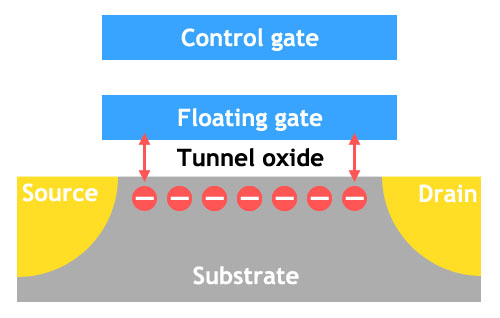

Memória flash e outras opções de EPROM e EEPROM baseadas em transistores de porta flutuante.

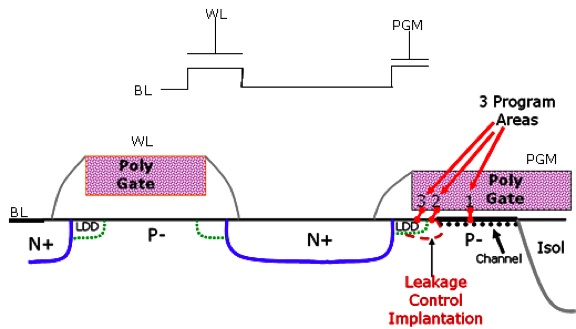

Figura 10. Esquema de gravação em flash. Fonte - techreport.com

Figura 10. Esquema de gravação em flash. Fonte - techreport.comO princípio de operação desse tipo de memória é bastante simples: um portão "flutuante" está localizado em uma espessa camada de um dielétrico. Uma carga elétrica pode ser colocada neste obturador por tunelamento, aplicando alta tensão a ele. E então, se você não aplicar alta tensão, a carga poderá ser armazenada no obturador "flutuante" por um período muito longo.

E a segurança?

A boa notícia é que o estado da EEPROM não pode ser visto com um microscópio. Mau? Existem vários deles ao mesmo tempo.A primeira má notícia é que a EEPROM é apagada não apenas pela alta tensão, mas também pela exposição à radiação ultravioleta (os veteranos provavelmente se lembram dos chips de vidro de quartzo). Ao mesmo tempo, se você examinar atentamente a topologia com um microscópio, poderá cobrir toda a memória com um material opaco, exceto os poucos bits que incluem proteção contra leitura e após a exposição, seu chip. Moral: Usando a EEPROM em seu projeto, cubra-a com metal por cima. E é desejável não apenas com um escudo sólido contra radiação, mas também com algumas linhas significativas, para que o escudo não possa ser gravado com precisão. No entanto, uma emboscada também está oculta aqui (é a segunda má notícia), porque, em princípio, um microcircuito ou suas partes individuais podem ser destacadas a partir de baixo. Isso não é fácil, porque provavelmente será necessário remover o chip do gabinete e,por exemplo, gravando o fundo do substrato, mas possível. Tais técnicas são populares para testar microcircuitos de chip único, porque a metalização é opaca aos raios UV e ao laser, e o substrato de silício é quase transparente, a questão é como focalizar o feixe de radiação corretamente, se for necessária a exposição local.Como opção alternativa, você pode configurar os bits de ativação / desativação da proteção para que o apagamento deles ative a proteção e não a desative.A terceira má notícia é que existem sensores que podem ler a carga elétrica em um portão flutuante ou seus remanescentes após uma operação de apagamento. Além disso, para ler eletricamente a memória, em geral, o chip não precisa ser alimentado, ou seja, não há risco de ativar os mecanismos internos de destruição de informações.Mram, embora relativamente raro, no entanto, também merece nossa atenção. Como o flash, não pode ser considerado opticamente. O MRAM, é claro, não pode ser apagado com luz ultravioleta, mas existem sensores de campo magnético com uma resolução alta o suficiente para separar os metais superiores e ler a memória pouco a pouco. Boas notícias? É improvável que um invasor em potencial os encontre de maneira rápida e barata. Em geral, o MRAM é uma boa alternativa ao flash do ponto de vista da segurança, mas até o momento não está amplamente disponível e apenas entrou em produção em massa em tecnologias disponíveis para empresas que não são fábricas.Hoje, a ROM antifusa é considerada a memória mais protegida da engenharia reversa.. Como o nome indica, ele representa um certo antípoda de jumpers queimados, ou seja, possui alta resistência em um estado não programado e baixa em um programado. Como isso é alcançado? Com a quebra do portão dielétrico de um transistor com alta tensão. A região de ruptura é tão pequena que não é visível nem de cima no microscópio nem na seção da FIB, mas também fornece uma mudança boa e confiável na resistência por várias ordens de grandeza, o que é suficiente para uma leitura confiável do estado da memória de maneira regular. Essa célula de memória, no entanto, pode ser lida conectando-se diretamente à porta e à fonte do transistor de memória. Uma célula ininterrupta se comporta como um capacitor, uma célula unida se comporta como um resistor. Figura 11. Seção celular de uma memória antifusa. São mostradas várias áreas de possível quebra do transistor. Isso pode complicar o esquema de leitura.Obviamente, existem outras maneiras de descobrir o conteúdo da memória, além da inspeção visual das células. A maneira mais fácil é usar o FIB para conectar-se diretamente às linhas de leitura correspondentes e enviar a eles todos os sinais de controle que precisam ser enviados para ler informações inacessíveis normalmente. Anteriormente, você pode desativar a proteção de leitura cortando fisicamente as linhas que levam aos bits correspondentes de memória. Como se proteger disso? Tendo projetado corretamente a topologia do seu chip e, possivelmente, integrado algumas funções adicionais. Aqui está um exemplo de como o Cypress faz isso:It is possible to configure the nvSRAM to provide password protected access. In this configuration, instead of performing the normal power up recall sequence on power up, the part waits for the user to enter a 5-byte password followed by an End Password Entry soft sequence. The End Password Entry soft sequence is a specific seven-address read sequence. If you enter the correct password, the part completes the boot up sequence and is ready for the normal nvSRAM operations. If you enter the incorrect password three times or you do not enter the right password within a specified period of time, the part locks up or fills the SRAM memory with random data, as the application requirement may be. The part can be configured to additionally destroy the functionality and cause physical damage to the chip.Normalmente, isso é feito: a memória é coberta de cima por uma grade de linhas de terra e energia, e todas as linhas de sinal estão localizadas estritamente abaixo delas. Nesse caso, deve-se tomar cuidado para garantir que as linhas de energia, por um lado, não se duplicem (isto é, ao cortar qualquer uma delas, parte do microcircuito para de funcionar) e, por outro lado, para que cada uma delas sirva muitos bits de memória , e a inserção de um amperímetro na linha de energia não nos permite estimar o estado da memória pelo consumo no modo de leitura (que difere para diferentes estados lógicos na maioria dos tipos de memória). Com essa organização das camadas superiores do chip, será extremamente difícil para um invasor abrir parte da metalização para se conectar a onde ele precisa.Mesmo na grade de terrenos e fontes de alimentação, linhas de proteção adicionais são organizadas de forma que uma interrupção nelas (ou seu curto-circuito na energia ou no aterramento) quando a energia é fornecida ao chip inicia o apagamento completo do conteúdo da memória protegida (ou, como vimos acima, danos físicos chip). Tais linhas de proteção, localizadas próximas às linhas terrestres e elétricas, complicam bastante o trabalho dos atacantes, porque as operações com a FIB exigem um lugar tangível pelos padrões dos processos tecnológicos atuais. Além disso, devido à forma em forma de cone do recorte criado pelo microscópio, quanto menor a camada à qual você deseja conectar, maior a área que você precisa limpar.Mas, de fato, com muita frequência, um invasor pode não precisar do valor exato do conteúdo da memória; pode ser suficiente reduzir o número de opções de classificação em várias ordens de magnitude. Por exemplo, se uma célula de memória consome ao ler uma unidade lógica X e ao ler um zero lógico de 100 * X, ao ler um byte dessa memória, obteremos um consumo diferente, dependendo do conteúdo da memória:0 - 800 * X1,2,4, ..., 64, 128 - 701 * X3, 6, 7, ..., 160, 192 - 602 * X....255 - 8 * XNo total, se não tocarmos na memória, precisamos de 256 tentativas para selecionar a senha contida nela. E se sabemos que o consumo no modo de leitura é 701 * X, existem apenas oito. Conveniente, não é? A maneira mais fácil de fazer algo com esse problema é armazenar os dados na forma de um valor e sua inversão em uma célula vizinha; o consumo de qualquer quantidade de memória no modo de leitura não dependerá das informações armazenadas. É verdade que requer o dobro de memória, mas a segurança é importante para nós, certo?

Figura 11. Seção celular de uma memória antifusa. São mostradas várias áreas de possível quebra do transistor. Isso pode complicar o esquema de leitura.Obviamente, existem outras maneiras de descobrir o conteúdo da memória, além da inspeção visual das células. A maneira mais fácil é usar o FIB para conectar-se diretamente às linhas de leitura correspondentes e enviar a eles todos os sinais de controle que precisam ser enviados para ler informações inacessíveis normalmente. Anteriormente, você pode desativar a proteção de leitura cortando fisicamente as linhas que levam aos bits correspondentes de memória. Como se proteger disso? Tendo projetado corretamente a topologia do seu chip e, possivelmente, integrado algumas funções adicionais. Aqui está um exemplo de como o Cypress faz isso:It is possible to configure the nvSRAM to provide password protected access. In this configuration, instead of performing the normal power up recall sequence on power up, the part waits for the user to enter a 5-byte password followed by an End Password Entry soft sequence. The End Password Entry soft sequence is a specific seven-address read sequence. If you enter the correct password, the part completes the boot up sequence and is ready for the normal nvSRAM operations. If you enter the incorrect password three times or you do not enter the right password within a specified period of time, the part locks up or fills the SRAM memory with random data, as the application requirement may be. The part can be configured to additionally destroy the functionality and cause physical damage to the chip.Normalmente, isso é feito: a memória é coberta de cima por uma grade de linhas de terra e energia, e todas as linhas de sinal estão localizadas estritamente abaixo delas. Nesse caso, deve-se tomar cuidado para garantir que as linhas de energia, por um lado, não se duplicem (isto é, ao cortar qualquer uma delas, parte do microcircuito para de funcionar) e, por outro lado, para que cada uma delas sirva muitos bits de memória , e a inserção de um amperímetro na linha de energia não nos permite estimar o estado da memória pelo consumo no modo de leitura (que difere para diferentes estados lógicos na maioria dos tipos de memória). Com essa organização das camadas superiores do chip, será extremamente difícil para um invasor abrir parte da metalização para se conectar a onde ele precisa.Mesmo na grade de terrenos e fontes de alimentação, linhas de proteção adicionais são organizadas de forma que uma interrupção nelas (ou seu curto-circuito na energia ou no aterramento) quando a energia é fornecida ao chip inicia o apagamento completo do conteúdo da memória protegida (ou, como vimos acima, danos físicos chip). Tais linhas de proteção, localizadas próximas às linhas terrestres e elétricas, complicam bastante o trabalho dos atacantes, porque as operações com a FIB exigem um lugar tangível pelos padrões dos processos tecnológicos atuais. Além disso, devido à forma em forma de cone do recorte criado pelo microscópio, quanto menor a camada à qual você deseja conectar, maior a área que você precisa limpar.Mas, de fato, com muita frequência, um invasor pode não precisar do valor exato do conteúdo da memória; pode ser suficiente reduzir o número de opções de classificação em várias ordens de magnitude. Por exemplo, se uma célula de memória consome ao ler uma unidade lógica X e ao ler um zero lógico de 100 * X, ao ler um byte dessa memória, obteremos um consumo diferente, dependendo do conteúdo da memória:0 - 800 * X1,2,4, ..., 64, 128 - 701 * X3, 6, 7, ..., 160, 192 - 602 * X....255 - 8 * XNo total, se não tocarmos na memória, precisamos de 256 tentativas para selecionar a senha contida nela. E se sabemos que o consumo no modo de leitura é 701 * X, existem apenas oito. Conveniente, não é? A maneira mais fácil de fazer algo com esse problema é armazenar os dados na forma de um valor e sua inversão em uma célula vizinha; o consumo de qualquer quantidade de memória no modo de leitura não dependerá das informações armazenadas. É verdade que requer o dobro de memória, mas a segurança é importante para nós, certo?CASO 3: SEM MEMÓRIA

Mas e se o seu chip não contiver memória de configuração ou apenas alguns bits, que não têm sentido ocultar. Porque Portanto, é muito mais barato (não tanto pela redução do custo das máscaras para a litografia, mas por um processo mais simples de embalagem e teste) e, para a maioria dos chips simples, o preço é uma séria vantagem competitiva.

Falando em testes. O processo de rejeição de cristais em bolachas e memória de configuração piscante geralmente é terceirizado, especialmente por pequenas empresas, porque o equipamento apropriado geralmente não é acessível para startups e a qualidade deve ser garantida. Portanto, se a produção de terceiros estiver atualizada com seus métodos de teste e tiver firmware de memória de configuração, seria melhor você confiar completamente nessas pessoas. Ou tenha métodos adicionais de proteção contra engenharia reversa que não estejam vinculados à memória de configuração.

Então, o que fazer se a memória de configuração não for uma opção de proteção ou se não for suficiente?

A principal desvantagem de um microscópio óptico e de MEV é que é muito difícil distinguir entre os tipos de dopagem de silício. Ou seja, a presença de ligas é visível, mas o tipo não é. Portanto, ao analisar a topologia e extração do circuito, o tipo de dopagem é restaurado do contexto e da lógica implícita do circuito (transistores de canal n são conectados ao terra, transistores de canal p são conectados à energia, etc., etc.). Tendo desenhado a topologia do seu microcircuito para que ele não coincida com a opção mais intuitivamente mais provável, você pode muito bem estragar o sangue de um engenheiro reverso. Especialmente se você usar vários esquemas diferentes disfarçados da mesma forma. Com alguma destreza, você pode não apenas complicar a análise do seu circuito, mas também fazer com que o dispositivo (ou pelo menos modelado, mas mais divertido se produzido) usando a topologia restaurada faça algo específico, desde o curto-circuito com energia até a emissão de palavras obscenas para todas as saídas. O comportamento determinístico de um projeto roubado incorretamente, a propósito, pode ser útil não apenas para gravar um osciloscópio para piratas, mas também para que quando os usuários frustrados de seus chips cheguem até você mais tarde, você possa demonstrar claramente a eles que eles compraram falso.

Figura 12. Seção de três estruturas indistinguíveis por um microscópio. O da esquerda é pMOSFET, o do meio é um curto-circuito, o da direita é um diodo polarizado (gap) reverso.

Figura 12. Seção de três estruturas indistinguíveis por um microscópio. O da esquerda é pMOSFET, o do meio é um curto-circuito, o da direita é um diodo polarizado (gap) reverso. Figura 13. Topologia de três células da biblioteca digital indistinguíveis por um microscópio. O da esquerda é o inversor, o do meio é a conexão direta da entrada e saída, o da direita é a unidade lógica de saída.

Figura 13. Topologia de três células da biblioteca digital indistinguíveis por um microscópio. O da esquerda é o inversor, o do meio é a conexão direta da entrada e saída, o da direita é a unidade lógica de saída.Cada uma das células da figura acima parece quase o inversor mais comum, mas na verdade pode ser um inversor, repetidor ou gerador de um zero lógico ou unidade lógica. Somente nossos contatos para difusão da entrada e saída emitem nosso "inversor". No entanto, abandonando-os, obteremos um indistinguível completamente do circuito padrão em troca da incapacidade de implementar a conexão de entrada e saída (mas podemos usar dois inversores para esse fim). No entanto, com a capacidade de inverter ou não inverter um sinal usando a mesma célula, a luta contra um invasor é muito mais interessante, porque nada complica as tentativas de lidar com problemas de um design desconhecido, como um inversor extra em algum lugar do relógio ou no circuito on / off.

Embora não, isso acontece. Uma topologia manual bem construída é geralmente bem lida. Um ótimo

exemplo está no blog já mencionado de Ken Schirriff.

Figura 14. Unidade lógica aritmética (ALU) do chip Intel 8008. Dígitos separados são mostrados.

Figura 14. Unidade lógica aritmética (ALU) do chip Intel 8008. Dígitos separados são mostrados.Na topologia da ALU Intel 8008, oito circuitos idênticos são perfeitamente visíveis - pelo número de bits. Entendendo que isso é ALU, é possível restaurar facilmente o esquema de topologia. Se alguns dos elementos forem falsos, isso complicará um pouco o seu trabalho, mas não mais. E tudo porque a topologia se encaixa bem na idéia básica das interfaces entre as partes constituintes. Para confundir tanto um invasor que ele abandona as tentativas de engenharia reversa, é necessário tornar a topologia imprevisível e não repetitiva. A maneira mais fácil não é fazer nenhum bloco manualmente, mas gerar toda a lista líquida do chip usando CAD. Os rastreadores automáticos, apesar da enorme economia de tempo para criar uma topologia (em comparação com o trabalho manual), fazem um excelente trabalho ao criar um arranjo não intuitivo de elementos e, às vezes, conexões completamente insanas. E quanto maior o design, cuja topologia foi sintetizada como um todo, mais difícil é fazer a engenharia reversa.

Mas esta é a maneira mais fácil. Existem opções mais interessantes. Por exemplo, use um conjunto de células camaleão como um conjunto de geradores de zeros lógicos e uns para as entradas do multiplexador, enquanto realiza uma função lógica arbitrária. Na verdade, é assim que os elementos do FPGA, LUT (Look-Up Table) são organizados.

Figura 15. Implementação de um LUT de três entradas. Fonte

Figura 15. Implementação de um LUT de três entradas. FonteColocando vários desses LUTs em diferentes locais do circuito e trazendo alguns sinais para as entradas das “células de memória”, resolveremos vários problemas ao mesmo tempo:

- Se nossa manobra continuar sem solução, poderemos definir exatamente como o circuito de engenharia reversa se comportará. Opções - qualquer, limitadas apenas pela sua imaginação.

- O uso de sinais arbitrários de outros blocos como "entrada" para as células que geram zero lógico e um complicará o processo de separação visual do design em blocos.

- Mesmo que o engenheiro reverso perceba que estamos usando essas LUTs protegidas, ele terá que examinar várias opções para restaurar a funcionalidade do circuito de acordo com a topologia, de modo que até um número relativamente pequeno de células protegidas possa tornar a engenharia reversa desnecessariamente demorada. Meu favorito é montar uma máquina de estado nessas LUTs que controla as transições do microcircuito de um modo operacional para outro.

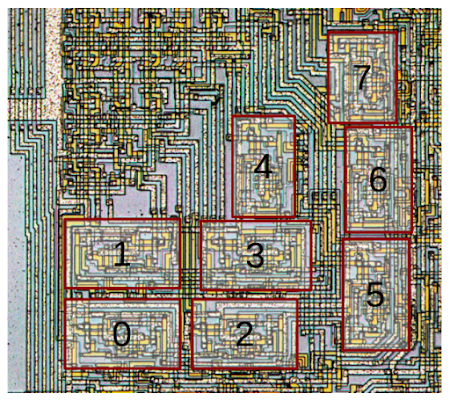

DIAGRAMAS DE ENSAIO

Bons engenheiros gostam muito de testar exaustivamente seus chips. E por “abrangente”, quero dizer - aproximadamente da mesma maneira que no conversor TI DC / DC na figura abaixo. Dezenas de pequenas almofadas de contato, às quais você pode se conectar antes de cortar a placa em cristais individuais, para verificar todos os parâmetros necessários, o status de linhas internas importantes, decidir se o chip é adequado ou não e, se necessário, descobrir a causa dos problemas.

Figura 16. Topologia da Texas Instruments TPS 62321. Source - zeptobars.com

Figura 16. Topologia da Texas Instruments TPS 62321. Source - zeptobars.comUma boa cobertura com blocos de teste para lançamentos e protótipos de teste é especialmente importante, mas para produção em série eles geralmente são desativados (pela correção de uma ou duas máscaras ou jumpers graváveis) para minimizar o efeito no comportamento do produto. Então, do que estou falando? As almofadas de contato de teste são sua grande ajuda para um invasor, porque você não apenas aponta pontos importantes no design, mas também fornece acesso conveniente a elas. O jumper queimado é facilmente restaurado no FIB, e pronto! Idealmente, a segurança requer a remoção completa dos blocos de teste do chip serial. Se essa opção for irracional (por exemplo, você também precisa testar em uma placa na produção em série), pelo menos verifique se o mecanismo para desconectar os locais de teste não é recuperável, por exemplo, está localizado diretamente sob a plataforma e foi desenhado para que a lacuna não pôde ser convenientemente conectado.

Eu nem quero começar pelo fato de que todos os projetos digitais modernos têm um JTAG embutido para teste, o que permite ver diretamente o status de qualquer gatilho em um chip. A adequação do teste é uma das principais características de qualquer projeto, e é esse fato que torna extremamente importante desativar com segurança e permanência todas as interfaces de teste antes que o chip saia das paredes do fabricante.

Ainda bons engenheiros gostam de colocar circuitos de teste na periferia do chip para as próximas revisões. Geralmente, esses são esquemas bastante importantes; caso contrário, por que perder tempo e esforço organizando seus testes? "Os circuitos importantes que compõem sua propriedade intelectual e são críticos para o funcionamento do chip?" Cuidadosamente separados de todo o design? Muito obrigado! - o engenheiro reverso lhe dirá um presente tão real. Se você não quiser que os testes ajudem um invasor a estudar e copiar seu projeto, verifique se eles não entram em cristais para produção em massa ou são destruídos após o teste em placas durante o processo de corte da placa em cristais.

UMA PRÁTICA PEQUENA

Para demonstrar mais uma vez como isso funciona, o

exemplo de abertura do microcontrolador PIC12C508A descrito na dissertação de Sergei Skorobogatov, defendida em 2004 em Cambridge. A tradução é curta e bastante gratuita:

É necessário abrir a caixa e encontrar no chip uma memória de proteção apagada pela radiação ultravioleta. Isso é feito com bastante facilidade, visualizando as linhas que vão para o pino de programação do chip. Depois, você cobre a memória principal com um material opaco para UV, e após cinco a dez minutos de exposição, você pode considerar a memória como um programador regular. Outra opção - depois de encontrar a memória de proteção contra cópia, basta cortar o caminho metálico que leva a ela, que por algum motivo está localizado longe de outras linhas - até agora, você pode cortá-lo não apenas com FIB, mas apenas com uma agulha. Figura 17. E aqui está a linha muito infeliz. Na verdade, ele está localizado no meio de um espaço vazio, não protegido de forma alguma, pode ser cortado.

Figura 17. E aqui está a linha muito infeliz. Na verdade, ele está localizado no meio de um espaço vazio, não protegido de forma alguma, pode ser cortado.CONCLUSÃO

Obviamente, é impossível apreender a imensidão, porque a tecnologia e a engenharia reversa dos microcircuitos, e a proteção contra eles, não param e são constantemente aprimoradas. O tópico segurança da informação é uma das chaves no design da Internet, por isso os desenvolvedores prestam muita atenção e os engenheiros reversos não podem esperar uma extração tão fácil quanto quinze ou vinte anos atrás. No entanto, deve-se sempre lembrar que um sistema mal protegido significa perdas potenciais, enormes perdas ou até a vida das pessoas, e a proteção contra acesso não autorizado e engenharia reversa deve fazer parte do sistema em todos os níveis de operação, sem excluir o hardware .