Embora tenham se passado 14 anos desde que o

primeiro SSD SATA foi lançado, muitos consumidores ainda se referem a unidades de estado sólido com uma quantidade razoável de ceticismo. O principal motivo da desconfiança é o recurso de trabalho limitado da memória flash, devido à degradação gradual da estrutura semicondutora dos chips, como resultado dos quais os dispositivos, mais cedo ou mais tarde, perdem a capacidade de registrar e armazenar informações. As especificações técnicas detalhadas geralmente agravam a situação: é difícil para um comprador entender se a TBW 500 TB mencionada na descrição do Western Digital Blue 3D NAND SATA 3D da AMD para dois terabytes é muito ou pouco? Quanto dura uma unidade desse tipo em condições operacionais reais e pode ser confiável com os arquivos mais valiosos? Vamos tentar entender esse problema juntos e falar sobre o quão confiável é a memória flash moderna.

A rigor, a resposta para a “principal questão da vida, o universo e tudo isso” foi recebida em dezembro de 2014, quando os

membros da publicação da rede

TechReport concluíram o teste de SSDs de consumidores, que duraram um total de um ano. Usando os produtos HyperX, Corsair, Kingston e Samsung como exemplos, eles provaram de forma convincente que a vida real dos SSDs excede 1 petabyte de dublagem. Esses volumes são quase impensáveis, não apenas para o usuário médio, mas também para criadores de conteúdo profissionais: a unidade se tornará obsoleta moralmente muito antes do esgotamento de seus recursos.

No entanto, há uma nuance significativa: há quatro anos, os chips MLC NAND estavam em uso, capazes de armazenar 2 bits de informação em cada célula e fabricados usando uma tecnologia de processo de 25 nanômetros. Naquela época, havia um bom compromisso entre o SLC altamente confiável (célula de nível único) e o TLC mais espaçoso e barato (célula de nível triplo): chips com células de dois bits forneciam uma densidade de armazenamento de dados aceitável, suportando até 5.000 ciclos de gravação / apagamento (em em média, esse número chega a 3 mil). O que não se pode dizer sobre seus irmãos mais próximos: por todas as vantagens, que incluem alta capacidade e baixo custo, os TLCs eram muito menos resistentes, tendo dificilmente atingido os 1.500 mil ciclos de programação / apagamento, apesar do fato de que a maioria dos microcircuitos planas mal consegue suportar mil.

O principal culpado nessa situação foi a transição para um processo de 15 nanômetros usado na produção de chips. Para entender por que isso aconteceu, lembre-se de como a memória NAND funciona. A codificação de bits de informação ocorre alterando a carga em um portão flutuante devido ao tunelamento quântico de elétrons através da camada dielétrica, devido à alta intensidade do campo elétrico.

Circuito de transistor de porta flutuanteDo ponto de vista da física, estamos lidando apenas com o fenômeno de um colapso reversível semelhante a uma avalanche. Acelerando em um campo elétrico, os elétrons recebem energia cinética suficiente para a ionização por impacto das moléculas dielétricas, resultando em um par de partículas elementares com carga oposta, que também são aceleradas por um campo elétrico, e o processo se repete, enquanto o número de portadores de carga aumenta exponencialmente (daí o nome ) É fácil adivinhar que esses processos causam desgaste gradual das camadas dielétricas, como resultado, aumenta a probabilidade de vazamento de carga nas células vizinhas, o que, por sua vez, leva a danos ou até a completa perda de dados. E a transição para uma nova tecnologia de processo só agrava a situação: uma diminuição na espessura do dielétrico leva ao fato de que as células falham muito antes.

No entanto, se o problema fosse apenas esse, consumidores comuns e usuários corporativos simplesmente não teriam notado a diferença entre MLC e TLC, e nas especificações técnicas do SSD veríamos números muito mais impressionantes. Na realidade, uma imagem completamente diferente aparece diante de nossos olhos, e a arquitetura dos chips flash e as especificidades de seu trabalho são a razão disso: células individuais são combinadas em páginas e páginas em blocos, enquanto a gravação de informações é possível apenas em páginas em branco e sua remoção é bloco por bloco.

O que isso significa na prática? Suponha que tenhamos um bloco parcialmente preenchido e desejemos gravar novos dados nele. Se o volume for menor que o espaço livre restante, a gravação ocorrerá instantaneamente, sem nenhuma manipulação adicional. Se não houver espaço suficiente, algoritmos complexos de vários estágios entram em jogo. Considere a situação no diagrama abaixo.

É assim que os dados são gravados na memória flashOs novos dados que queremos gravar ocupam duas páginas em um bloco, mas apenas uma é realmente gratuita: embora a página antiga (destacada em amarelo) tenha sido excluída pelo usuário anteriormente, na verdade, as informações gravadas não desapareceram. Para liberar espaço para novos dados, o controlador inicia um procedimento conhecido como coleta de lixo, excluindo dados desnecessários e redistribuindo os existentes. Para fazer isso, todas as páginas, exceto as desnecessárias, são copiadas para o segundo bloco livre, enquanto a primeira é completamente apagada. Em seguida, as páginas reais são transferidas de volta para o primeiro bloco, excluídas do segundo e somente depois disso os novos dados tomam seu devido lugar.

No exemplo acima, para gravar duas páginas, tivemos que reescrever completamente 2 blocos duas vezes, seis páginas cada. De fato, o processo de “Coleta de Lixo” parecerá muito mais complicado e, como resultado, o número de ciclos de reescrita será muito maior. A imagem real pode ser estimada apenas conhecendo o coeficiente de amplificação de gravação, que mostra quantas vezes a carga real na memória flash excede a calculada. Esse indicador pode ser igual à unidade somente ao gravar informações em um disco formatado e absolutamente limpo, em todos os outros casos, seu valor varia de 2 a 25. Além disso, mesmo à primeira vista, unidades idênticas podem diferir significativamente, portanto dependendo do modelo do controlador usado e dos recursos do firmware. Assim, a tolerância a falhas do SSD é determinada não apenas pelo tipo de memória flash, mas também pelo quanto os desenvolvedores foram capazes de otimizar o desempenho da camada FTL (camada de tradução em flash).

Por que o aumento dramático na densidade de armazenamento não afetou a confiabilidade da memória 3D NAND?

Portanto, agora sabemos como a memória flash funciona e quais fatores determinam a confiabilidade de uma unidade SSD. É hora de descobrir quais são as vantagens oferecidas pela transição dos chips "planos" para os tridimensionais. Primeiro, o 3D NAND difere de seus antecessores devido ao uso da “armadilha de carga” (Charge Trap Flash) em vez das persianas flutuantes familiares. Se neste último caso, o polissilício com dopantes é usado para armazenar cargas, então no CTF é uma região isolada de material não condutor, na maioria das vezes SiN - nitreto de silício. Essa abordagem tornou possível minimizar a probabilidade de vazamento de carga e, como resultado, aumentar a estabilidade da célula.

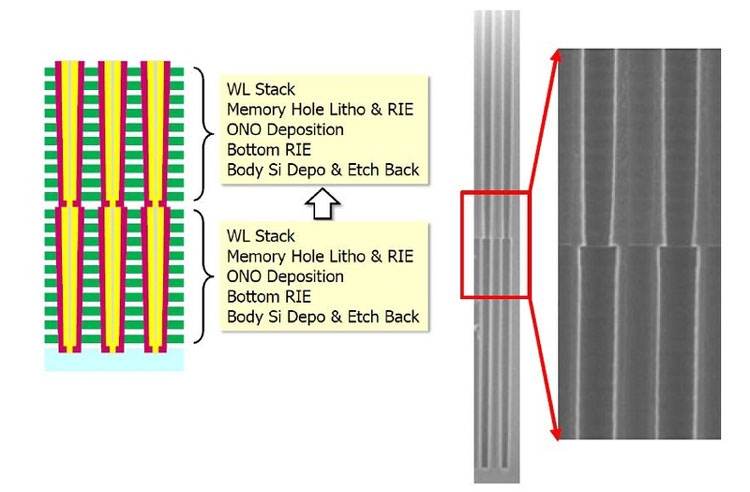

A arquitetura dos chips de memória tridimensionais também passou por mudanças significativas em relação ao seu antecessor, já que agora cada célula possui uma estrutura cilíndrica: a camada externa é uma porta de controle e a interna é um isolador. Como as células agora estão localizadas uma acima da outra, elas formam uma pilha, dentro da qual passa um canal feito de silício policristalino. É fácil entender que o número de camadas em um chip determina o número de células na pilha.

Dispositivo de célula de chip NAND 3DEssa estrutura tornou possível reduzir a interferência entre as células e, assim, simplificar o algoritmo de gravação: como não havia necessidade de verificar o estado da carga, a gravação na célula começou em uma única etapa. Outra nuance importante: para a produção de 3D NAND, são utilizados processos de amaciamento, apesar de a densidade de empacotamento das células poder aumentar significativamente. Assim, por exemplo, até chips de 48 camadas (a terceira geração de memória flash tridimensional) foram produzidos usando uma tecnologia de processo de 40 nanômetros. Isso tornou possível não apenas aumentar sua confiabilidade, mas também reduzir o custo de produção, uma vez que as linhas de produção existentes precisavam apenas de modernização mínima e a necessidade de litografia em ultravioleta profundo desapareceu completamente.

Falando especificamente sobre os produtos Western Digital, então nos modernos

SSDs WD Black SN750 NVMe , cujo início de vendas começou em 18 de janeiro de 2019, é utilizado o TLC 3D NAND BiCS de 64 camadas (Bit Cost Scalable) de 64 camadas, fabricado com a tecnologia de processo de 28 nanômetros. Além de aumentar a densidade de empacotamento em outras 1,4 vezes (o modelo superior agora tem uma capacidade de 2 TB, que é o dobro do tamanho da capitânia da geração anterior), uma característica importante desse tipo de chip é o uso de cordas em forma de U.

Arquitetura 3D NAND BiCSComo agora o transistor de comutação e a linha de fonte estão localizados na parte superior do chip, eles praticamente não são expostos a influências de alta temperatura, o que pode levar a erros durante as operações de leitura / gravação, o que melhora ainda mais a confiabilidade das unidades de estado sólido.

Como os algoritmos de gravação afetam a vida de um SSD?

Já escrevemos acima que, por mais robusta e segura que seja a memória flash, seu recurso será desperdiçado se os desenvolvedores do SSD não se importarem em criar algoritmos de gravação eficazes. Para otimizar esse procedimento, duas técnicas muito eficazes são usadas: armazenamento em cache do SLC e nivelamento de desgaste.

A essência da primeira é que parte da matriz de memória disponível, cujo tamanho depende do volume total da unidade (por exemplo, ao desenvolver o

WD Blue 3D NAND SSD, procedemos ao cálculo de 4 GB de cache para cada 250 GB de capacidade) é transferida para o modo de operação SLC, ou seja, , apenas um bit de informação é registrado em cada célula, o que permite aumentar significativamente seu desempenho e reduzir a taxa de desgaste. O SLC está envolvido na gravação e consolidação dos dados armazenados no SSD, o que permite não apenas aumentar a velocidade das operações, mas também reduzir a taxa de desgaste das células. Nas versões atuais dos SSDs da Western Digital, é usada a tecnologia nCache 3.0, a última versão que adquiriu a função direta para TLC, que possibilitou encontrar um equilíbrio entre o cache e a velocidade: os dados são gravados ignorando o cache quando ele está cheio ou ao usar o SLC- o buffer não é prático. Por um lado, isso ajudou a descarregar o cache e, ao mesmo tempo, a evitar uma queda drástica no desempenho ao preenchê-lo.

Dinâmica da velocidade de gravação no SSD ao preencher o buffer SLCQuanto à tecnologia de nivelar o desgaste, ajuda a garantir que todos os blocos de páginas disponíveis sejam usados da maneira mais uniforme possível. Como você sabe, qualquer sistema operacional usa um mecanismo lógico para endereçar os blocos de dados (LBA), enquanto o próprio controlador opera com endereços físicos (PBA), correlacionando-os com os lógicos. Como resultado disso, não importa onde os fragmentos dos arquivos estão realmente localizados, devido aos quais é possível escrever um microprograma que garantirá que a carga entre as células seja distribuída uniformemente.

O nivelamento de desgaste garante uma carga uniforme nas célulasNo caso geral, seu algoritmo é o seguinte. Você comprou um SSD novo e, embora haja espaço livre nele, as informações serão gravadas em blocos livres. À medida que você opera, você começa a excluir arquivos desnecessários e o mecanismo de coleta de lixo os limpa em segundo plano; no entanto, eles serão usados para gravação somente depois que não houver um único bloco no disco pelo menos uma vez na qual os dados foram gravados. Certamente, na realidade, tudo é muito mais complicado, mas o significado não muda.

E aqui mais uma observação importante deve ser feita com relação aos produtos da Western Digital. Quando decidimos desenvolver o mercado de SSD, podíamos seguir de duas maneiras: comprar memória e controladores de fabricantes terceirizados, focando apenas no desenvolvimento e otimização do firmware ou configurar uma produção de ciclo completo. A execução de um projeto desse tipo seria impraticável, e mesmo a

compra da SanDisk nos custou um centavo. Mas os fundos investidos superaram totalmente: controlando a produção de chips, tivemos a oportunidade de adaptar os microprogramas às características dos microcircuitos.

Deve-se entender que gravar bits de informação nas células da memória flash é um processo muito mais complicado do que parece à primeira vista: leva em consideração centenas de parâmetros diferentes, dos quais os mais importantes são a tensão necessária para a transferência de carga e o tempo de gravação. À medida que os chips se desgastam, suas características físicas também mudam: para o registro bem-sucedido dos dados, é necessária menos tensão e, ao mesmo tempo, o tempo necessário de sua influência na célula é reduzido. Na maioria dos SSDs, esses parâmetros são constantes, mas nos SSDs da Western Digital, pelo contrário, eles mudam dinamicamente à medida que as células se desgastam, o que permite maximizar a vida de cada um deles, minimizando o impacto negativo nas estruturas de semicondutores.

QLC 3D NAND - memória flash de última geração

Se você acompanhar as notícias do mundo das altas tecnologias, provavelmente está ciente de que a Western Digital está dominando ativamente a produção de memória tridimensional de próxima geração - QLC 3D NAND (o primeiro anúncio ocorreu em junho de 2018). O acrônimo QLC significa célula de nível quádruplo. Em outras palavras, 16 níveis de carga podem ser armazenados em uma célula, codificando não apenas três, mas quatro bits de informação. Comparado ao TLC 3D NAND, a densidade de gravação no QLC aumentou 33%: assim, a capacidade de um chip de 64 camadas aumentou para 768 Gbps. Mas esse não é o limite: em agosto de 2018, iniciamos o lançamento de microcircuitos de 96 camadas. Ao aumentar o número de camadas, conseguimos obter um aumento de 50% na capacidade e superar a barreira de 1 Tbit: novos chips, chamados 3D NAND BiCS4, podem acomodar 1,33 Tbit de informação, ou seja, 166 GB. Foi possível alcançar uma densidade de armazenamento de dados tão alta combinando dois cristais de 48 camadas (hoje essa é a abordagem economicamente mais viável).

A capacidade aumentada é potencialmente capaz de reduzir o desempenho dos SSDs, mas você não deve se preocupar com isso: a nova memória flash 3D NAND BiCS4 usa quatro em vez de duas matrizes físicas, o que possibilita otimizar a leitura e gravação de dados por operações paralelas, e isso, por sua vez, Isso ajudará a usar o cache de forma mais eficiente e a controlar o nível de desgaste das células, mantendo a vida útil dos chips QLC em um nível comparável às soluções modernas de TLC. No entanto, uma descrição das tecnologias subjacentes ao QLC está além do escopo deste material e certamente merece um artigo separado.