Continuamos a considerar o UDB com base na documentação proprietária do Cypress, ou seja, curiosidades úteis relacionadas ao Datapath.

O conteúdo geral do ciclo “UDB. O que é isso? "

Parte 1. Introdução. Pld.Parte 2. Datapath.Parte 3. Datapath FIFO.Parte 4. Datapath ALU.Parte 5. Caminho de Dados. Pequenas coisas úteis. (Artigo atual)

Parte 6. Módulo de gerenciamento e status.Parte 7. Módulo de controle de tempo e redefiniçãoParte 8. Endereçando UDB21.3.2.6 Suporte CRC / PRS

O Datapath suporta a geração das verificações cíclicas de redundância (CRC) e pseudo-aleatórias (Pseudo Random Sequence, PRS). Sinais encadeados são rastreados entre os blocos do Datapath para suportar CRC / PRS com mais de 8 bits.

O número de bit mais significativo (MSB) do bloco CRC / PRS mais alto é selecionado e rastreado (e acorrentado a outros blocos) aos blocos inferiores. Depois disso, a operação XOR com dados de entrada (dados SI) é aplicada ao MSB, fornecendo um sinal de feedback (feedback, FB). Depois disso, o sinal de feedback é rastreado (e conectado em uma cadeia com outros blocos) aos blocos inferiores. Esse valor de feedback é usado em todos os blocos para executar a operação

XOR do polinômio (do registro Data0 ou Data1) com o valor atual da bateria.

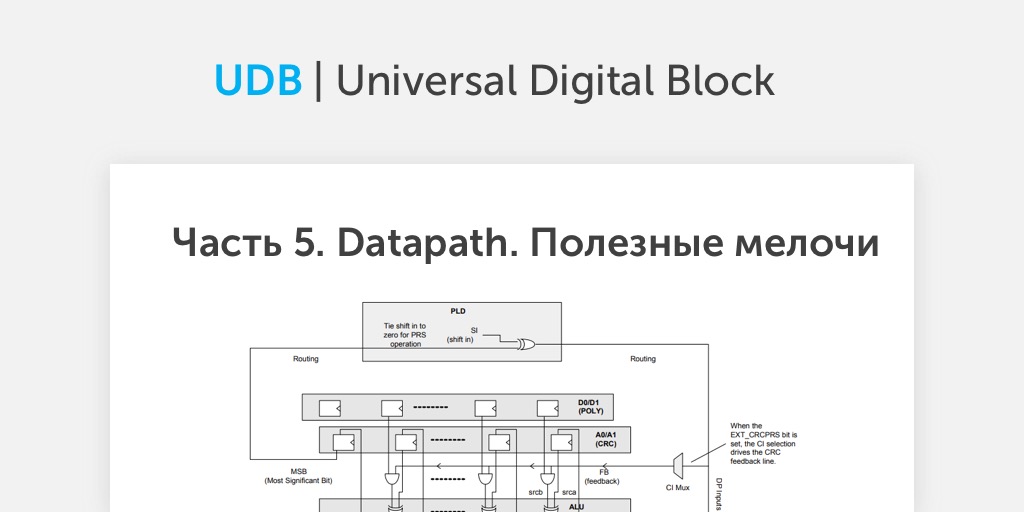

A Figura 21-18 mostra a configuração estrutural da operação CRC. A configuração do PRS é idêntica, mas a entrada de deslocamento (SI) é puxada para 0. No modo PRS, D0 ou D1 contém o valor polinomial e A0 ou A1 contém o valor inicial (semente) e o valor CRC obtido após o cálculo.

Nota do tradutor.Aparentemente, há um erro de digitação na documentação proprietária nesta frase, pois um número aleatório deve ser obtido no modo PRS. E as informações sobre a CRC estão localizadas logo abaixo. Figura 21-18. Estrutura funcional do CRC.

Figura 21-18. Estrutura funcional do CRC.Para ativar o suporte a CRC, você deve definir o bit

CFB_EN na RAM de configuração dinâmica como 1. Isso ativa a operação

AND em relação à entrada SRCB ALU e ao sinal de feedback CRC. Se esse bit estiver definido como zero, o sinal de feedback será atribuído a um, o que permite que operações aritméticas normais sejam executadas. O controle dinâmico desse bit em cada ciclo permite alternar as operações CRC / PRS com outras operações aritméticas.

Encadeamento CRC / PRS

A Figura 21-19 mostra um exemplo de ligação de CRC / PRS em cadeias entre três UDBs. Este cenário suporta a operação em modos com uma resolução de 17 a 24 bits. Os bits de ligação de controle nas cadeias são definidos de acordo com a posição do Datapath na cadeia (veja a figura).

Figura 21-19. Ligação em cadeia de CRC / PRS.

Figura 21-19. Ligação em cadeia de CRC / PRS.Como o sinal de feedback CRC / PRS (cfbo, cfbi) é conectado em uma cadeia:

- Se o bloco selecionado for o mais novo, o sinal de feedback nesse bloco é gerado a partir da lógica interna, que leva a entrada de turno para a direita (senhor) e executa uma operação XOR neles com o bit mais significativo. (No caso do PRS, o sinal "senhor" é definido como "0").

- Se o bloco selecionado não for um bloco de ordem baixa, o bit de configuração CHAIN FB deve ser engatilhado e o feedback é transmitido em uma cadeia do bloco anterior.

Como a cadeia de sinal CRC / PRS MSB (cmsbo, cmsbi):

- Se o bloco selecionado estiver alto, o bit de configuração MSB (de acordo com o polinômio selecionado) é configurado usando os bits de configuração MSB_SEL .

- Se o bloco selecionado não estiver alto, o bit de configuração CHAIN MSB deve ser armado e o sinal MSB será enviado ao longo da cadeia a partir do próximo bloco.

Especificação polinomial CRC / PRS

Como um exemplo da configuração do polinômio para gravar no registro correspondente D0 / D1, considere o polinômio

CCITT CRC-16 , que tem a forma x

16 + x

12 + x

5 + 1. O método de extração do formato de dados do polinômio é mostrado na Figura 21-20. O termo X0, por definição, é sempre 1, portanto, não precisa ser escrito. Para todos os outros membros do polinômio, a unidade é definida nas posições necessárias, conforme mostrado na figura.

Figura 21-20. O formato do polinômio CCITT CRC16.

Figura 21-20. O formato do polinômio CCITT CRC16.Observe que o formato do polinômio é um pouco diferente do formato especificado no formato hexadecimal clássico. Por exemplo, o polinômio

CCITT CRC16 é comumente referido como

1021H . Para convertê-lo no formato necessário para o Datapath, é necessário executar um deslocamento à direita em uma posição e adicionar 1 ao bit MSB. Nesse caso, o valor polinomial correto a ser escrito em D0 ou em D1 é

8810H .

Exemplo de configuração do CRC / PRS

A seguir, é apresentada uma breve descrição dos requisitos de configuração do CRC / PRS, desde que D0 seja um polinômio e o CRC / PRS seja calculado em A0:

- Escolha um polinômio adequado (exemplo acima) e escreva-o para D0.

- Selecione a semente apropriada (por exemplo, todos os zeros para CRC ou todos os PRS) e grave-a em A0.

- Se necessário, configure o encadeamento conforme descrito acima.

- Selecione um item MSB como descrito acima.

- Configure campos de RAM dinâmica RAM:

a. Selecione D0 como ALU “SRCB” (fonte de dados ALU B)

b. Selecione A0 como ALU “SRCA” (fonte de dados ALU A)

c. Selecione

XOR para operação da ALU

d. Selecione

SHIFT ESQUERDO para operação SHIFT

e Selecione

CFB_EN para ativar o

suporte ao CRC / PRS.

f. Selecione ALU como origem de registro A0

Ao escolher o CRC, é necessário configurar a

mudança no campo

direito para os dados de entrada e enviar dados sobre essa entrada a cada etapa. Ao escolher o PRS, você deve definir o

deslocamento à direita como 0.

Essa configuração do UDB gera o CRC necessário ou produz o bit mais significativo, que pode ser encaminhado para o exterior, removendo dele uma sequência pseudo-aleatória.

Modo externo CRC / PRS

Para habilitar a computação externa de CRC ou PRS, você pode especificar um bit de configuração estática (

EXT CRCPRS ). Conforme mostrado na Figura 21-21, o cálculo do feedback CRC é realizado no bloco PLD. Quando o bit é engatilhado, o sinal de feedback CRC é transmitido diretamente do multiplexador de entrada CI (Carry In), ignorando os cálculos internos. A figura mostra uma configuração simples que suporta CRC ou PRS até 8 bits. Geralmente, são usados circuitos eletrônicos internos, mas esse parâmetro permite implementar configurações mais complexas, por exemplo, funções CRC / PRS de 16 bits em um UDB, usando a multiplexação por divisão do tempo.

Figura 21-21. Modo externo CRC / PRS.

Figura 21-21. Modo externo CRC / PRS.Nesse modo, o bit

CFB_EN da RAM de configuração dinâmica também controla se a operação

AND é usada no sinal de feedback CRC na entrada CRCB ALU ou não. Assim, como no caso do modo interno CRC / PRS, esta função pode, se necessário, alternar com outras funções.

21.3.2.7 Saídas do caminho de dados e multiplexação

As condições são geradas a partir dos valores de disparo da bateria, saídas da ALU e status FIFO. Essas condições podem ser transmitidas por meio de canais de rastreamento digital para outros UDBs para formar solicitações de interrupção no DMA ou nas "pernas do chip". 16 condições possíveis são mostradas na tabela abaixo.

Tabela 21-16. Geração de condição do datapath.

Existem seis saídas do Datapath. Conforme mostrado na Figura 21-22, cada saída possui um multiplexador 16 em 1 que permite rotear qualquer um dos 16 sinais para qualquer saída do Datapath.

Figura 21-22. Conexões com o multiplexador de saída.

Figura 21-22. Conexões com o multiplexador de saída.Comparações

Existem duas comparações, uma das quais com fontes fixas (

Compare 0 ) e a outra selecionada dinamicamente (

Compare 1 ). Cada comparação possui um registro de máscara estático de 8 bits, permitindo comparações no campo de bit especificado. Por padrão, o mascaramento é desativado (todos os bits são comparados) e deve ser ativado manualmente.

As entradas Compare 1 são configuradas dinamicamente. Como mostrado na tabela abaixo, existem quatro parâmetros Compare 1 que se aplicam às condições iguais e inferiores. Os

bits de configuração

CMP SELA e

CMP SELB determinam as possíveis configurações de comparação. Os bits de RAM da configuração dinâmica especificam uma das configurações (A ou B) em cada ciclo.

Tabela 21-17. Configuração de comparação.

A comparação 0 e a

comparação 1 estão associadas às condições geradas no Datapath anterior de forma independente (na ordem do tratamento). Se encadear comparações ou não é estaticamente especificado nos registros de configuração do UDB. A Figura 21-23 mostra a ligação “igual” à cadeia de comparação, o que reduz a aplicação da operação

AND à comparação “igual” deste bloco e à entrada do bloco anterior.

Figura 21-23. Vincular à cadeia de comparação é "igual".

Figura 21-23. Vincular à cadeia de comparação é "igual".A Figura 21-24 mostra a ligação à menor cadeia de comparação. Nesse caso, o resultado da saída (cl0) para um determinado bloco é gerado pelo circuito de comparação “menor que” e é incondicional. Este sinal é combinado

OU com o resultado recebido da cadeia se a condição for igual ao bloco atual e o modo de ligação estiver ativado.

Figura 21-24. Link menor que

Figura 21-24. Link menor queDetecção de todos os zeros e todos os

Cada bateria possui um detector de todos os zeros e um detector de todas as unidades. Essas condições podem ser encadeadas estaticamente, conforme indicado nos registros de configuração do UDB. O modo de ligação é definido nos registros de configuração do UDB. A ligação na cadeia de detecção de zeros ocorre de acordo com o mesmo conceito que a comparação "igual". Se o encadeamento estiver ativado, a operação

AND será aplicada aos dados vinculados com êxito.

Estouro

Um estouro é definido como uma operação de transferência

XOR em um MSB e uma transferência de um MSB. Os cálculos são realizados com o MSB atual, conforme indicado nos bits

MSB_SEL . Essa condição não pode ser encadeada, no entanto, o cálculo estará correto se a função de capacidade total for executada no Datapath mais antigo até que a transferência entre os blocos seja conectada.

21.3.2.8 Caminho de dados de entradas e saídas paralelas

Conforme mostrado na Figura 21-25, os sinais

Parallel In (PI) e

Parallel Out (PO) fornecem uma capacidade limitada de fornecer dados e rastrear recursos para o Datapath e enviar dados a partir dele. Os sinais PO estão sempre disponíveis para rastreamento como uma opção de ALU asrc entre A0 e A1.

Nota do tradutor.Este é um mecanismo extremamente importante que permite ao UDB trabalhar não apenas com serial, mas também com dados paralelos. Por alguma razão, este documento não enfatiza isso, mas você pode ler sobre isso de passagem em uma das Notas da aplicação. Figura 21-25. Sinais de entrada / saída de dados paralelos.

Figura 21-25. Sinais de entrada / saída de dados paralelos.Para inserir dados na ALU, você deve selecionar Entrada

paralela . Existem dois modos: estático e dinâmico. No modo estático, o bit

PI SEL converte o valor asrc ALU em PI. O bit

PI DYN é usado para fornecer o modo dinâmico PI. Quando está armado e também desde que o

PI SEL seja 0, o multiplexador PI pode controlar o bit de controle dinâmico

CFB_EN . A principal função do bit

CFB_EN é fornecer a funcionalidade PRS / CRC.

21.3.2.9 Encadeando o caminho de dados

Cada bloco do Datapath possui uma ALU de 8 bits, projetada para encadear hífens, turnos, gatilhos de captura e sinais condicionais ao Datapath vizinho mais próximo para criar funções aritméticas e registrar registros com profundidades de bits mais altas. Esses sinais, conectados em cadeias, são isolados e permitem implementar efetivamente funções de 16 a 24 e 32 bits em um único ciclo, sem corridas e outros problemas decorrentes de atrasos nos canais de rastreamento. Além disso, as alças de encadeamento suportam a leitura atômica de baterias em blocos interligados. Como mostra a Figura 21-21, todos os sinais condicionais e de captura gerados são conectados em uma cadeia que se move do bloco mais jovem para o mais antigo. Um deslocamento para a esquerda também é realizado de júnior para sênior. Um deslocamento para a direita é realizado do mais antigo para o mais novo. O sinal de encadeamento CRC / PRS para feedback é roteado de alto para baixo, e a saída MSB é enviada de alto para baixo.

Figura 21-26. Cadeia de segmentação do Datapath.

Figura 21-26. Cadeia de segmentação do Datapath.21.3.2.10 configuração dinâmica de RAM

Cada caminho de dados contém uma RAM de configuração dinâmica com 8 palavras de 16 bits cada (consulte a Figura 21-27). O objetivo dessa RAM é controlar os bits da configuração do Datapath em cada ciclo, com base no relógio selecionado para esse Datapath. A RAM possui portas de leitura e gravação síncronas para baixar configurações através do barramento do sistema.

Para enviar rapidamente essas palavras de 16 bits para o Datapath, uma porta de leitura assíncrona adicional é fornecida como bits de controle. As entradas de endereço assíncronas são selecionadas pelos multiplexadores das entradas do Datapath, que podem ser obtidas de qualquer sinal possível, incluindo pernas de microcircuito, saídas PLD, saídas da unidade de controle ou quaisquer saídas do Datapath.

O objetivo principal de uma porta de leitura assíncrona é fornecer decodificação rápida de bits de controle do Datapath em um único ciclo.

Figura 21-27. Configuração de E / S de RAM.

Figura 21-27. Configuração de E / S de RAM.Os campos da palavra RAM da configuração dinâmica são mostrados nas tabelas a seguir, juntamente com uma descrição do uso de cada campo.

Tabela 21-18. Referência de configuração dinâmica.

(a. - Para os campos CI, SI e CMP, os campos RAM permitem selecionar uma das duas opções predefinidas. Consulte a configuração do registro estático).

Para continuar ...