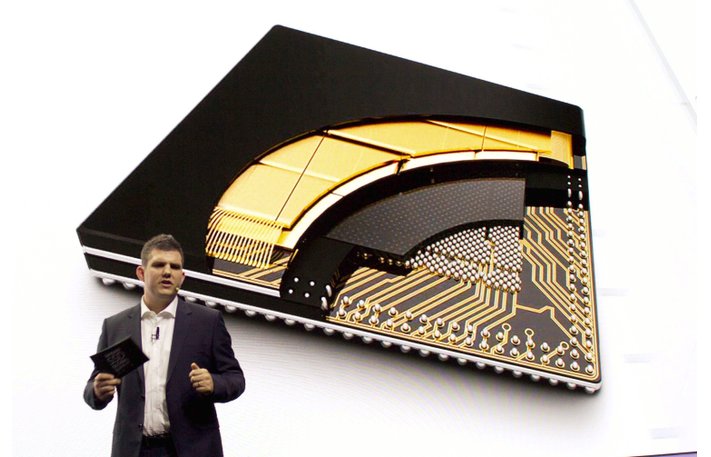

Intel Foveros 3D

Intel Foveros 3DComo a Lei de Moore não se aplica mais, os projetistas de chips precisam procurar outras maneiras de melhorar o desempenho. Uma tecnologia adequada para isso é chamada empilhamento de chips 3D. Essa é uma arquitetura de chips tridimensional em pilha, cujo desenvolvimento é a Intel líder. Dois meses atrás, a Intel introduziu a arquitetura

3D do

Foveros : uma estrutura tridimensional que inclui uma CPU de 10 nm, um chip de E / S e conexões elétricas verticais TSV (Through Silicon Via) no centro do chip e um chip de memória em cima de todo o chip.

Na conferência de computação de alto desempenho da Rice Oil and Gas HPC, a AMD

garantiu que estava trabalhando em sua própria versão da arquitetura de chips 3D.

Forrest Norrod, vice-presidente sênior e gerente geral, disse que a empresa está desenvolvendo várias tecnologias para aumentar os retornos e contornar os problemas associados ao término da Lei de Moore e as consequências de interromper o crescimento da densidade do transistor e da freqüência do relógio. Essas são conseqüências inevitáveis dos fabricantes que se aproximam do limite em que o tamanho do transistor é de apenas alguns átomos (o tamanho de um átomo de silício é de 0,2 nanômetros). O crescimento da energia do computador nos últimos anos veio não tanto de um aumento na velocidade da computação, mas de um aumento no paralelismo.

Como outras empresas, a AMD enfrentou uma limitação na área de chips de cerca de 700 mm² e é forçada a desenvolver uma arquitetura 3D. A empresa já está adotando essa abordagem, colocando a memória HBM2 ao lado do substrato da GPU, ou seja, é o mesmo caso do processador. Mas, no futuro, a empresa planeja avançar para o empilhamento 3D mais avançado.

Norrod disse que a AMD está trabalhando para colocar SRAM e DRAM diretamente sobre os componentes de computação (como processadores e GPUs) para fornecer ainda mais largura de banda e desempenho.

Samsung Polaris

Samsung PolarisEssa abordagem difere das implementações usuais de pacote em pacote (PoP), que simplesmente colocam dois casos acabados um sobre o outro, como Norrod mostrou usando o chip Samsung Polaris como exemplo. Neste exemplo, o gabinete DRAM é conectado através de duas linhas adicionais de conectores BGA que cercam o chip base. Esses conectores BGA transferem dados entre dois chips. Como em qualquer projeto padrão, a lógica está na parte inferior da pilha devido à necessidade de mais conectores, mas os dois cristais não estão diretamente conectados. Portanto, a abordagem PoP fornece densidade máxima, mas essa não é a opção mais rápida.

No empilhamento 3D verdadeiro, dois chips (neste caso, memória e processador) estão localizados um acima do outro e conectados por conexões TSV verticais que os interagem diretamente. Essas conexões TSV transferem dados entre os cristais na velocidade mais alta possível e geralmente estão localizadas no centro do chip, como vimos no Intel Foveros 3D. Esse emparelhamento direto melhora o desempenho e reduz o consumo de energia (toda movimentação de dados requer energia, mas as conexões diretas otimizam o processo). O empilhamento 3D também aumenta a densidade.

Norrod não entrou em detalhes dos projetos em desenvolvimento, mas isso pode se transformar em uma mudança fundamental no design do processador AMD.

A nova tecnologia Intel Foveros 3D pode vir a ser um momento decisivo para o setor, por isso não é surpreendente ouvir que a AMD está se movendo nessa direção,

escreve Tom's Hardware .

Até o momento, não há detalhes técnicos sobre a tecnologia de empilhamento 3D da AMD, além do que Forrest Norrod disse em uma apresentação intitulada Trabalhando Além da Lei de Moore, veja o vídeo abaixo.

Que outras alternativas existem para voltar à curva de crescimento exponencial prevista por Gordon Moore? Não existe uma resposta única para esta pergunta. A indústria de semicondutores está experimentando materiais que podem ser usados em vez de silício. Alguns materiais semicondutores III-V podem operar

em tensões mais baixas e em frequências mais altas que o silício , mas não tornam os átomos menores ou mais lentos. Restrições físicas ainda se aplicam.

A questão permanece como os futuros chips 3D esfriarão. Como resfriar efetivamente esse chip quando a energia é distribuída por ele? O microcircuito não poderá transferir energia para todos os circuitos simultaneamente sem superaquecer. Ela provavelmente terá que manter algumas partes desconectadas a maior parte do tempo e fornecer energia a cada parte apenas durante o uso.