No outro dia, a

estação automática japonesa Hayabusa-2 jogou uma bomba no asteróide Ryugu . A sonda é controlada por um sistema estável à radiação, baseado em um chip HR5000 (JAXA2010 / 101) com um núcleo de processador MIPS 5Kf de 64 bits. O computador de bordo executa o sistema operacional em tempo real uITRON, uma da família RTOS padrão TRON, que apareceu no Japão na década de 1980

e merece uma publicação separada .

Nesta nota, descreverei brevemente o que está incluído no HR5000 SoC e seu núcleo do processador, mostrarei fotos de dois dos principais desenvolvedores das linhas MIPS 4K e 5K e também mostrarei como você pode jogar em casa no FPGA com o "descendente de um irmão mais novo" deste computador - O kernel MIPS microAptiv UP de 32 bits, cujo código na linguagem de descrição de hardware Verilog foi baseado no MIPS 4KEc.

A agência aeroespacial japonesa JAXA licenciou o núcleo do processador MIPS 5Kf da MIPS Technologies, uma empresa americana. Isso aconteceu nos anos 2000. O grupo que desenvolveu esse núcleo existe em várias configurações há 40 anos:

- Primeiro, em 1978-1984, o MIPS foi um projeto em Stanford, liderado por John Hennessey. Com o sucesso desse projeto, Hennessey se tornou o autor do livro mais famoso sobre arquitetura de computadores e, em algum momento - o presidente de Stanford.

- Então, em 1984, o MIPS se tornou uma empresa comercial - MIPS Computer Systems. No mesmo ano, a ARM também foi comercializada. Em 1991, o MIPS lançou o primeiro microprocessador de 64 bits do mundo - MIPS R4000.

- Depois disso, o MIPS foi absorvido pela Silicon Graphics e, na década de 1990, foi usado dentro de estações gráficas, onde os primeiros filmes com gráficos realistas foram feitos em Hollywood (Jurassic Park).

- Nos anos 2000, o grupo se separou da MIPS Technologies e, em particular, projetou um processador para JAXA. O MIPS estava sediado na Califórnia; alguns dos desenvolvedores do MIPS 5Kf estavam localizados no MIPS Europe, em Copenhague.

- Em 2012, o MIPS Technologies foi comprado pela empresa britânica Imagination Technologies, que ficou famosa como desenvolvedor de GPU no início do iPhone da Apple.

- Em 2017, a Apple lançou o Imagination e, após alguns distúrbios, a tecnologia e parte do grupo MIPS integradas ao Wave Computing, uma startup que desenvolve um chip para acelerar redes neurais.

- O chip Wave Computing é uma combinação de um cluster de processadores MIPS I6500 de 64 bits, um multiplicador de matriz baseado em uma matriz sistólica no Google TPU e um processador de processador de dados baseado em um dispositivo com uma arquitetura reconfigurável de granulação grossa - CGRA ) Os processadores clássicos no cluster I6500 carregam o multiplicador de matriz e o processador de fluxo de dados, o multiplicador de matriz fornece densidade computacional e o processador de dados de tarefas está localizado no meio entre os processadores clássicos e o multiplicador de matriz - é mais flexível que o multiplicador e mais produtivo que a CPU clássica.

Então tirei uma foto com um dos dois principais desenvolvedores da linha MIPS 4K e 5K - Larry Hudepohl, Larry Huedepol (à direita em uma camisa vermelha). Larry começou sua carreira na Digital Equipment Corporation (DEC) como designer de processadores para o MicroVAX. Então Larry trabalhou para uma pequena empresa Cyrix, que no final dos anos 80 desafiou a Intel e fabricou um coprocessador FPU compatível com Intel 80387 e 50% mais rápido. Então Larry projetou chips MIPS na Silicon Graphics. Quando a MIPS Technologies se separou da Silicon Graphics, Larry e Ryan Quinter lançaram juntos o primeiro produto MIPS independente, o MIPS 4K, que se tornou a espinha dorsal da linha que dominava os eletrônicos domésticos dos anos 2000 (DVD players, câmeras, TVs digitais). Então o MIPS 5K voou para o espaço - foi usado pela agência espacial japonesa JAXA. Larry, como vice-presidente de engenharia de hardware, liderou o desenvolvimento das seguintes linhas e agora está trabalhando nas novas arquiteturas de aceleradores Wave:

Agora, de volta ao processador no Hayabusa-2 (no Hayabusa-1 é diferente). Aqui está uma

folha de dados para o núcleo do processador MIPS64 5Kf e uma

página com dados do sistema em um chip HR5000 . Observe alguns pontos interessantes.

Primeiro, o MIPS 5Kf é um processador em pipeline. Se você não está familiarizado com isso, a maneira mais fácil de se conhecer é estudar o sétimo capítulo do livro “Circuitos Digitais e Arquitetura de Computadores”, de David M. Harris e Sarah L. Harris, cuja versão mais recente pode ser baixada em russo

aqui ou

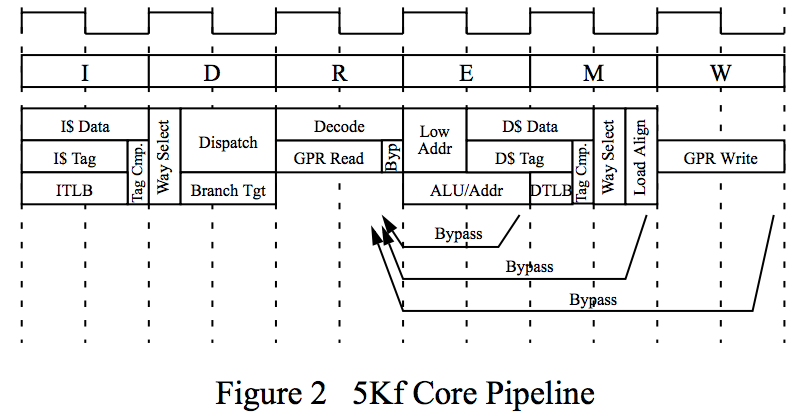

aqui ) . O transportador no MIPS 5Kf é diferente do transportador MIPS clássico da Harris & Harris. Quem leu X&X pode olhar para as diferenças e adivinhar por que:

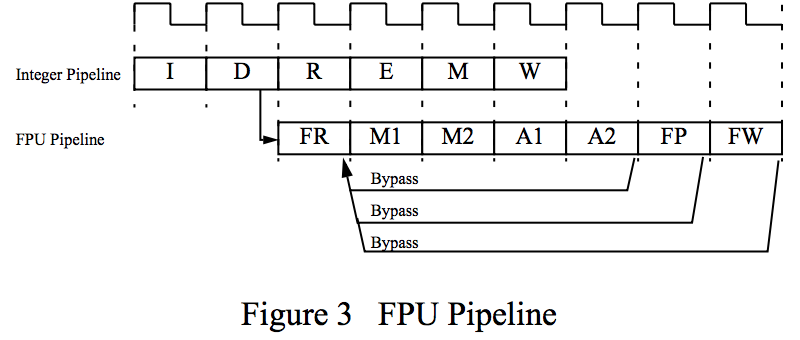

Obviamente, o MIPS 5Kf não possui cinco estágios de pipeline, mas seis, com um estágio de Despacho adicional. Essa etapa é necessária para tornar o MIPS 5Kf superescalar. Ele pode executar não apenas operações uma após a outra no pipeline, mas também pode executar uma operação de ponto flutuante simultaneamente com uma operação inteira ou com uma operação de memória (carregando ou salvando). O Stage Dispatch lança um coprocessador de ponto flutuante que possui seu próprio pipeline de sete estágios:

E aqui à direita na foto está Darren Jones, Darren Jones, desenvolvedor de FPU do MIPS 5Kf. A letra "f" em "5Kf" significa exatamente que possui um ponto flutuante:

Aqui nesta placa, você pode ver quantos ciclos requerem operações diferentes na FPU e com que frequência (taxa de repetição) eles podem ser executados no pipeline. Por exemplo, a multiplicação de precisão única requer quatro ciclos, mas você pode iniciar uma nova multiplicação no pipeline a cada ciclo. Assim, a FPU pode processar simultaneamente quatro multiplicações de precisão única em cada estágio de processamento. Mas a multiplicação de precisão dupla requer cinco ciclos, e você pode iniciá-la apenas com uma pausa no ciclo. A operação complexa de obter a raiz quadrada de precisão dupla requer até 32 ciclos, e você pode iniciar uma nova obtenção da raiz quadrada somente após 29 ciclos. É assim que o cálculo das coordenadas da nave e suas fórmulas de movimento no espaço sideral é otimizado:

O Hayabusa-2 usa a configuração do MIPS 5Kf com caches de instruções e dados de 32 kilobytes separados. Ao mesmo tempo, não está claro, a partir da

breve descrição do HR5000, se ele usa um cache de quatro canais de 8 kilobytes - ou um cache de dois canais de 16 kilobytes. Você pode ler como esses caches funcionam tanto no X&X quanto na

minha antiga apresentação sobre caches , bem como no livro útil

See MIPS Run Linux 2nd Edition por Dominic Sweetman:

O Hayabusa-2 também possui uma Unidade de Gerenciamento de Memória (MMU), com um buffer de tradução (TLS). O TLB é uma ferramenta universal para converter rapidamente endereços de virtual para físico. TLB permite que você:

Oculte a memória do sistema operacional do código não privilegiado.

Proteger os programas do usuário um do outro.

Forneça acesso ao programa à quantidade de memória virtual que excede a quantidade de RAM física.

Endereço maior memória física do que endereços virtuais estão disponíveis.

Coloque o programa em qualquer parte da memória física.

Permite que várias regiões da memória pareçam uma peça seqüencial.

Permite carregar partes do programa de um dispositivo externo, conforme necessário.

O TLB também associa vários atributos ao endereço: leitura, gravação e execução, além de atributos de cache e coerência.

O atributo de cache é necessário para mostrar ao processador onde o espaço de endereço está para o próximo nível de cache e onde os Resistores de E / S que não podem ser armazenados em cache.

Os atributos de coerência são necessários para que vários núcleos do processador trabalhem juntos, cada um com seu próprio cache de primeiro nível, e juntos eles usam um cache de segundo nível comum.

O TLB pode armazenar um indicador de que uma página com um determinado endereço foi gravada. Isso ajuda ao trocar, carregar e descarregar páginas de memória em sistemas com menos memória física do que o aplicativo precisa para endereçar todas as partes de seu código e dados com endereços virtuais.

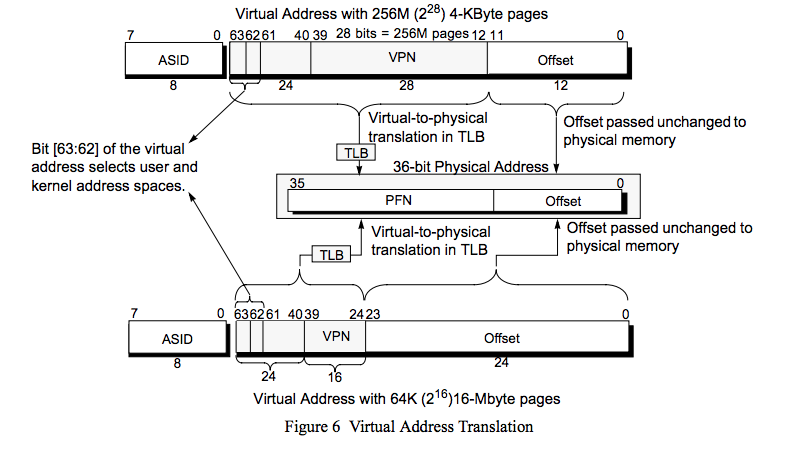

É assim que se parece a conversão de um endereço virtual de 64 bits em um endereço físico de 36 bits no MIPS 5Kf. Por que no Hayabusa-2 um processador de 64 bits com endereços físicos de 36 bits? Suspeito que o Hayabusa-2 tire fotografias e precise processar imagens, o que requer muita memória. Talvez para alguns algoritmos, as trocas aritméticas de 64 bits e de cache de 64 bits (ou trocas de memória não armazenáveis em cache de 64 bits) melhorem algo e sejam úteis no espaço. Mas não sei ao certo, provavelmente preciso perguntar a

Zelenyikot e

amartology , que sabem mais sobre espaço do que eu.

Você pode ler sobre o TLB em X&X e See MIPS Run, mas há uma nuance: os dois livros descrevem a aparência do TLB do ponto de vista de um programador. Mas, do ponto de vista do desenvolvedor de hardware, os projetistas de processadores estão enganando o programador, mostrando-lhe o TLB como uma tabela de tradução associativa, apesar do fato de haver realmente três tabelas dentro do TL: existem três instruções micro-TLB, dados micro-TLB e um comum (Joint TLB). Primeiro, o dispositivo de gerenciamento de memória pesquisa ITLB e DTLB e, somente se não o encontrar, o remove do JTLB. Isso custa ao processador mais 2 ciclos. Veja também

minha apresentação antiga no TLB :

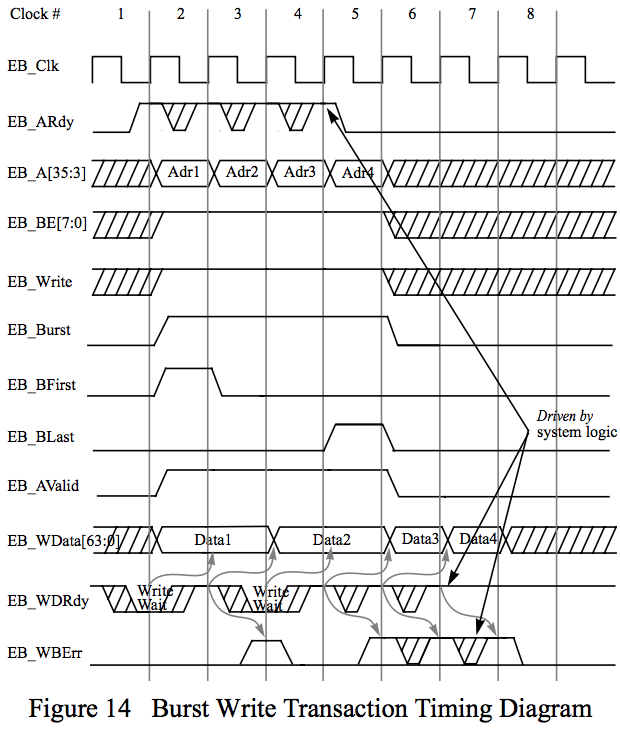

A interface entre os caches de primeiro nível e o controlador de memória no MIPS 5Kf no Hayabusa-2 é chamada EB (pronuncia-se IB). Isso é curto para barramento externo. É semelhante ao AHB e ao AXI e permite estourar, despejar do cache ou preencher o cache da memória por uma linha inteira, usando transferências em loops seqüenciais.

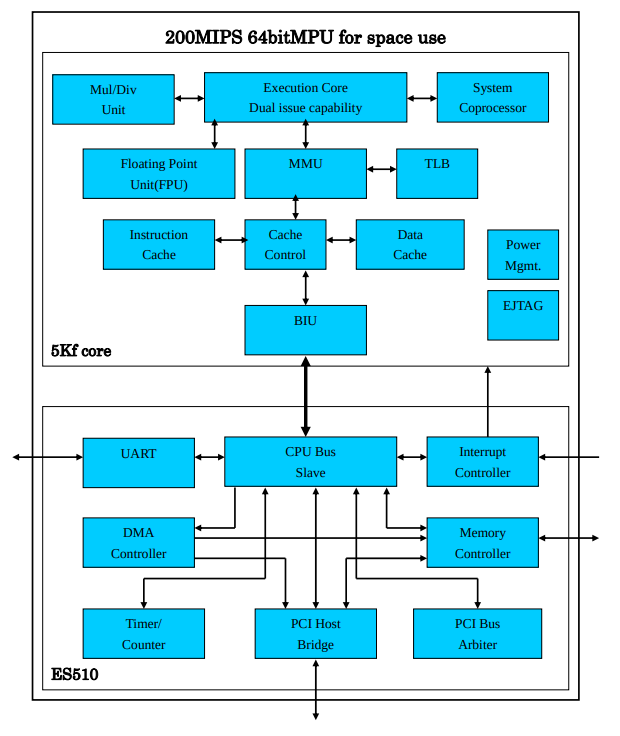

Fora do núcleo do processador, o HR5000 possui um controlador de interrupção, um módulo UART, um controlador de acesso direto à memória, temporizadores e um controlador PCI:

Para trabalhar no espaço, o chip deve ser protegido da radiação. Não sou especialista em proteção contra radiação, pois há uma

tecnologia em Habré, mas sei que essa proteção pode ser feita tanto no nível da tecnologia de produção física, como no nível de várias verificações do ECC, e até no nível da arquitetura, com o triplo, etc. Os criadores do sistema de cristal HR5000 decidiram usar a rota RTL2GDSII usual adotada em aplicações comerciais, síntese de um gráfico a partir de elementos lógicos a partir do código na linguagem de descrição de hardware da Verilog. No entanto, depois de receber esse gráfico (netlist), eles o modificam usando uma biblioteca especial de dureza por design (HBD) primitiva (nunca usou isso, portanto, qualquer esclarecimento nos comentários é bem-vindo):

Como o MIPS 5Kf está escrito em Verilog, ele pode ser transformado não apenas em uma netlist, mas também em uma máscara para fabricar um chip em uma fábrica, mas também em uma configuração FPGA. Infelizmente, as fontes do MIPS 5Kf não estão no domínio público, mas no domínio público são o código-fonte de um descendente de seu "irmão mais novo", um processador MIPS 4K de 32 bits. Esse "descendente" é chamado MIPS microAptiv UP e sua configuração básica está incluída no pacote MIPSfpga. O código MIPS 4K / 4KEc / microAptiv UP / M5150 (todas essas são versões progressivas da linha) também foi escrito por Larry, Ryan e Darren.

Você pode jogar com o pipeline, caches, dispositivo de gerenciamento de memória e interrupções do kernel do MIPS microAptiv UP, executá-lo em um simulador ou placa com FPGA / FPGA. Para fazer isso, basta baixar o

Pacote de introdução do

MIPS Open ™ FPGA , juntamente com o

MIPS Open ™ FPGA Labs , e (isso é importante!) Complemente com o

MIPSfpga + . Neste último, existem

laboratórios sobre o pipeline, o cache e o dispositivo de gerenciamento de memória .

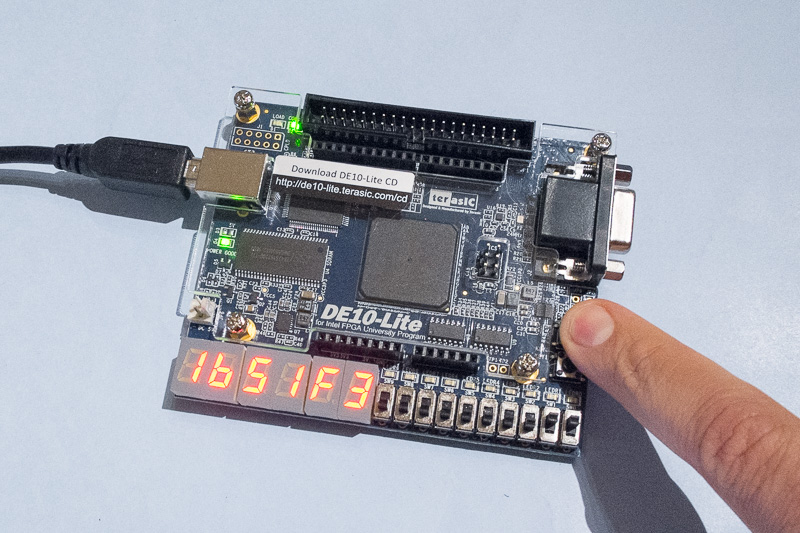

Você pode sintetizar e executar o processador MIPS microAptiv UP em uma placa barata por US $ 85 (preço acadêmico US $ 55):

Para trabalhar com o pacote MIPSfpga / MIPSfpga +, você precisa conhecer a linguagem de descrição de hardware Verilog, os princípios de design no nível de transferência de registro e a capacidade de escrever no MIPS assembler.

O assembler do MIPS é o mais fácil de aprender. Para fazer isso, você pode

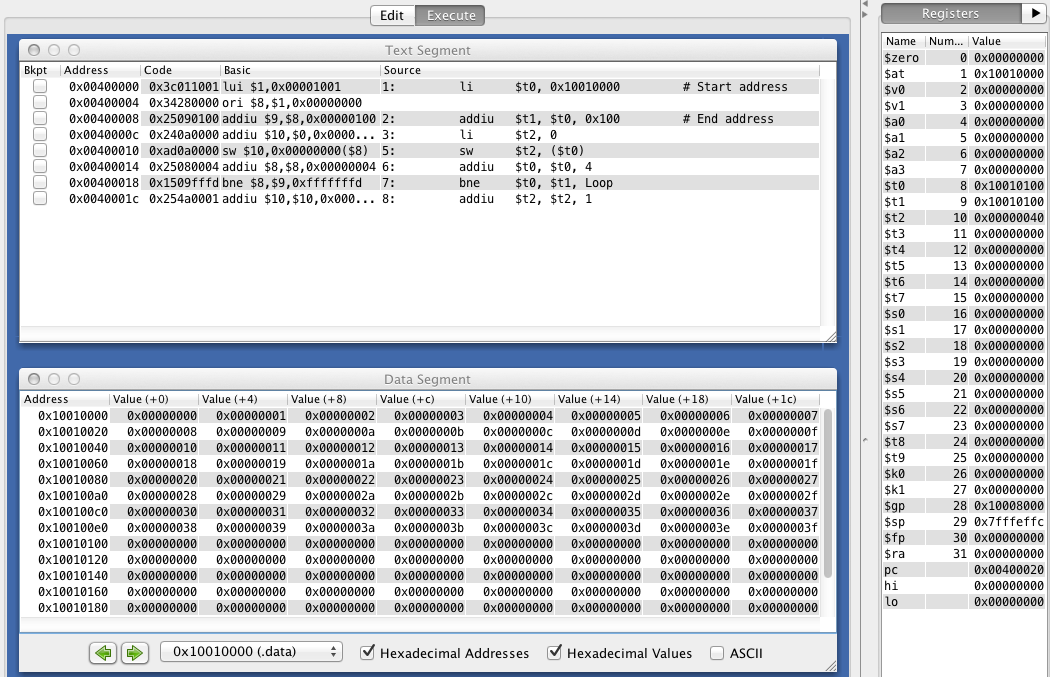

baixar o simulador MARS (MIPS Assembler e Runtime Simulator) . Você pode aprender a usá-lo em 5 minutos; na verdade, existem três botões: montar, executar, executar passo a passo:

Depois, você pode passar o dia praticando escrevendo em linguagem assembly para os livros

Harris & Harris e

See MIPS Run Linux .

Se você não sabe nada sobre o desenvolvimento de circuitos digitais em geral e no idioma para descrever equipamentos em particular, pode começar com o curso on-line de Rosnanov para crianças em idade escolar, em três partes:

"Do transistor ao microcircuito" ,

"O lado lógico do circuito digital" ,

"O lado físico circuitos digitais " ). Então você pode estudar o Verilog no X&X e entender que existe um processador no processador simplificado do

schoolMIPS .

Se você está interessado neste tópico e deseja participar do trabalho sobre o

MIPS Open (dentro da estrutura da qual o kernel do MIPS microAptiv UP foi aberto), escreva nos comentários. Rosnanovtsy também realiza um

seminário para crianças em idade escolar sobre design digital nos dias 17 e

19 de abril , que incluirá, entre outras coisas, esse processador espacial. O Hayabusa-2 bombardeou Ryuga por um motivo - essa também é uma ocasião para alunos e alunos russos descobrirem o que há dentro dela.