O próximo capítulo da documentação oficial do Cypress sobre gerenciamento de tempo e redefinição. Como já mencionado no primeiro artigo desta série, este módulo fornece seleção e resolução de tempo, além de redefinir a seleção no UDB. Mais detalhes - sob o corte.

O conteúdo geral do ciclo “UDB. O que é isso? "

Parte 1. Introdução. Pld.Parte 2. Datapath.Parte 3. Datapath FIFO.Parte 4. Datapath ALU.Parte 5. Caminho de Dados. Pequenas coisas úteis.Parte 6. Módulo de gerenciamento e status.Parte 7. Módulo de controle de tempo e redefinição. (Artigo atual)

Parte 8. Endereçando UDB21.3.4 Módulo de controle de reinicialização e relógio

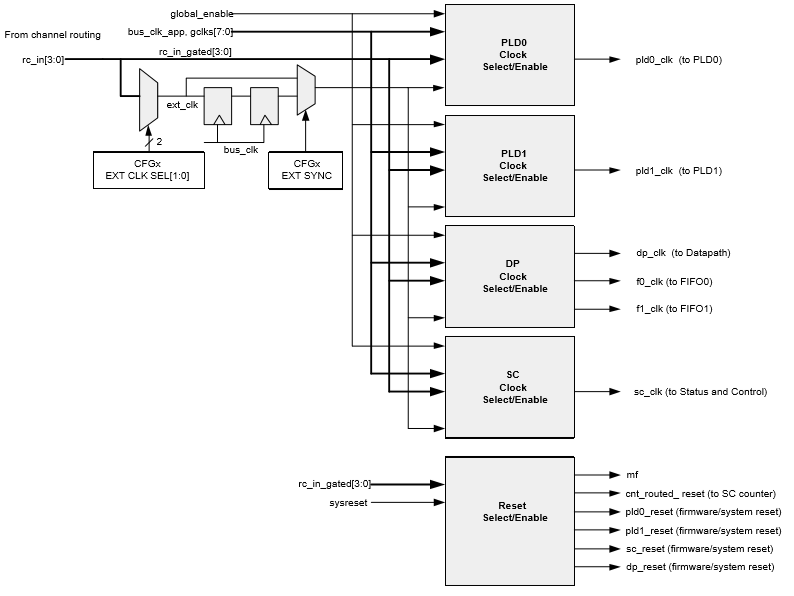

A principal função deste módulo é selecionar relógios dos relógios globais disponíveis ou relógio de barramento para cada PLD, Datapath e módulo de controle e status. O módulo também suporta redefinições de bloco UDB dinâmicas e de software. Como mostra a Figura 21-38, existem quatro unidades de controle de relógio e uma unidade de controle de redefinição. Quatro entradas (RC_IN [3: 0]) estão disponíveis para encaminhamento a partir da matriz de rastreamento global. Cada unidade de controle do relógio pode selecionar uma fonte para a entrada de ativação do relógio dessas entradas de rastreamento, e também há um multiplexador que permite selecionar uma das entradas de rastreamento para uso como fonte de relógio externa. Como você pode ver na figura, a escolha de uma fonte de relógio externa pode ser sincronizada. Para cada componente UDB, há 10 relógios para escolher: 8 relógios digitais globais, um relógio de barramento e um relógio externo selecionado (ext clk). Qualquer um dos sinais de entrada rastreados (rc_in) pode ser usado como um ativador sensível ao nível ou como um ativador sensível à borda. A função de redefinição deste bloco fornece uma redefinição rastreada dos blocos PLD e do contador SC, bem como a capacidade de redefinir programaticamente cada bloco para suportar a reconfiguração.

O relógio do barramento aplicado ao módulo de controle de relógio e redefinição é diferente do relógio do barramento do sistema. Este sinal é chamado "bus_clk_app" e está bloqueado da mesma maneira que outros sinais de relógio digital. O relógio do barramento do sistema é usado apenas para operações de entrada e saída e é desbloqueado automaticamente para cada acesso. O Datapath Clock Generator gera três relógios: um para o Datapath e um sinal para cada FIFO.

Figura 21-38. Relógio e redefinir o módulo de controle.

21.3.4.1 Controle do relógio

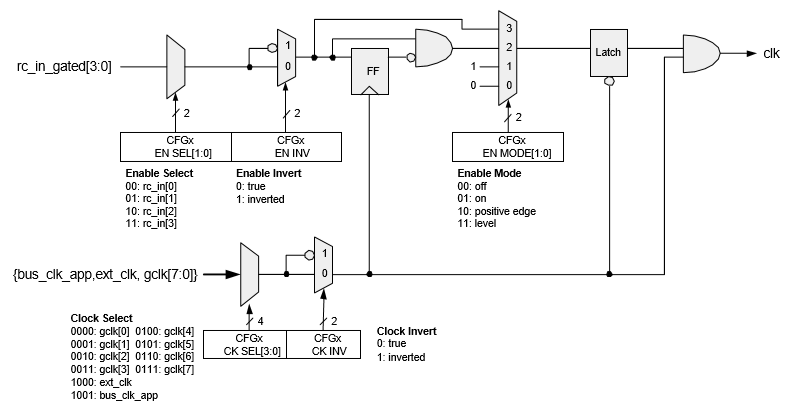

A Figura 21-39 mostra um exemplo de um esquema de seleção e resolução de temporização. Cada UDB possui quatro esquemas: um para cada bloco PLD, um para Datapath e um para o bloco de controle e status. Os principais componentes deste circuito são o multiplexador de seleção de relógio global, o inversor de relógio, o multiplexador de sinal de ativação do relógio, o inversor de sinal de ativação do relógio e a lógica de detecção diferencial.

Figura 21-39. Gerenciar seleção / ativação do tempo.

Seleção de relógioExistem oito relógios digitais globais encaminhados para todos os UDBs. Qualquer um deles pode ser selecionado. Relógios digitais globais são saídas de divisores de frequência selecionados pelo usuário. Consulte “Sistema de temporização” na página 109 do original. Outra opção é o relógio do barramento, que tem a maior frequência do sistema. Esse sinal é chamado "bus_clk_app" e é rastreado separadamente do relógio do barramento do sistema. Além disso, para suportar funções com um sinal de relógio direto (por exemplo, SPI), uma linha externa de rastreamento pode ser selecionada como um sinal de relógio de entrada. Como as funções de aplicativo estão vinculadas a limites arbitrários no UDB, a escolha de um sinal de relógio individual para cada subcomponente do UDB contribui para uma granularidade precisa na programação.

Inversão do relógioO sinal do relógio selecionado pode ser invertido. Isso limitará a frequência máxima de trabalho devido à existência de seções com um ciclo de meio ciclo. Gravação simultânea de barramento e gravações internas (por exemplo, programa gravando um novo valor de contador durante sua operação) não são suportadas quando o relógio interno é invertido e tem a mesma frequência que o relógio do barramento. Essa limitação afeta A0, A1, D0, D1, bem como o registro de controle no modo contador.

Seleção de ativação do relógioO sinal de habilitação do relógio pode ser encaminhado para qualquer sinal síncrono e selecionado em qualquer uma das quatro entradas da matriz de rastreamento disponíveis para este bloco.

Inversão de ativação do relógioO sinal de habilitação do relógio pode ser invertido. Devido a isso, esse sinal pode ser gerado em qualquer polaridade.

Modo de ativação do relógioPor padrão, o modo de resolução do relógio está desativado. Após definir a operação da unidade de destino, o software pode definir um dos modos operacionais descritos abaixo usando o registro CFGxEN MODE [1: 0], mostrado na Figura 21-39.

Tabela 21-23. Modos de resolução de tempo.

Usando permissão de relógioExistem dois casos de uso comuns para permissões de tempo.

Ativação de Software (Ativação de Firmware) : Supõe-se que a maioria das funções requer o relógio do software para iniciar e interromper a função. Como o limite de uma função vinculada a uma matriz UDB é condicional, uma função pode abranger vários UDBs e / ou partes de um UDB. Portanto, é necessária uma maneira de incluir cada função atomicamente. Isso geralmente é implementado usando um bit no registro de controle encaminhado para uma ou mais entradas de ativação do relógio. Esse cenário também suporta o caso em que os aplicativos precisam executar vários blocos não relacionados ao mesmo tempo.

Geração de relógio local emulada : esse recurso permite que os UDBs gerem relógios locais e os distribuam para outros UDBs na matriz usando o modelo de implementação de ativação do relógio de sincronização, em vez de fazer o clock de cada UDB diretamente separadamente. O uso da função Borda positiva para ativar a resolução remove as restrições no ciclo de trabalho do sinal de resolução.

Tempo Especial FIFOOs blocos FIFO Datapath possuem recursos de tempo. Por padrão, o relógio FIFO tem a mesma configuração que o relógio do Datapath. No entanto, os blocos FIFO possuem bits de controle especiais que alteram a configuração do relógio:

- cada relógio FIFO pode ser invertido em relação à polaridade do relógio Datapath selecionado;

- quando o modo FIFO FAST é selecionado, o relógio do barramento substitui a escolha do relógio do Datapath que normalmente usa o FIFO.

21.3.4.2 Redefinir o gerenciamento

Existem dois modos de gerenciamento de redefinição: herdados e padrão. O modo é definido usando o bit

ALT RES em cada registro de configuração do UDB CFG31. Por padrão, o valor do bit é 0 (modo legado); É recomendável atribuir a ele um valor 1 (modo padrão). O modo padrão tem um maior grau de granularidade - blocos individuais dentro do UDB podem usar descargas rastreadas. Para obter informações sobre o modo legado, entre em contato com o Cypress.

Controle de redefinição do PLDA Figura 21-40 mostra o sistema de redefinição do PLD.

Figura 21-40. Redefinir estrutura PLD.Controle de redefinição de caminho de dados

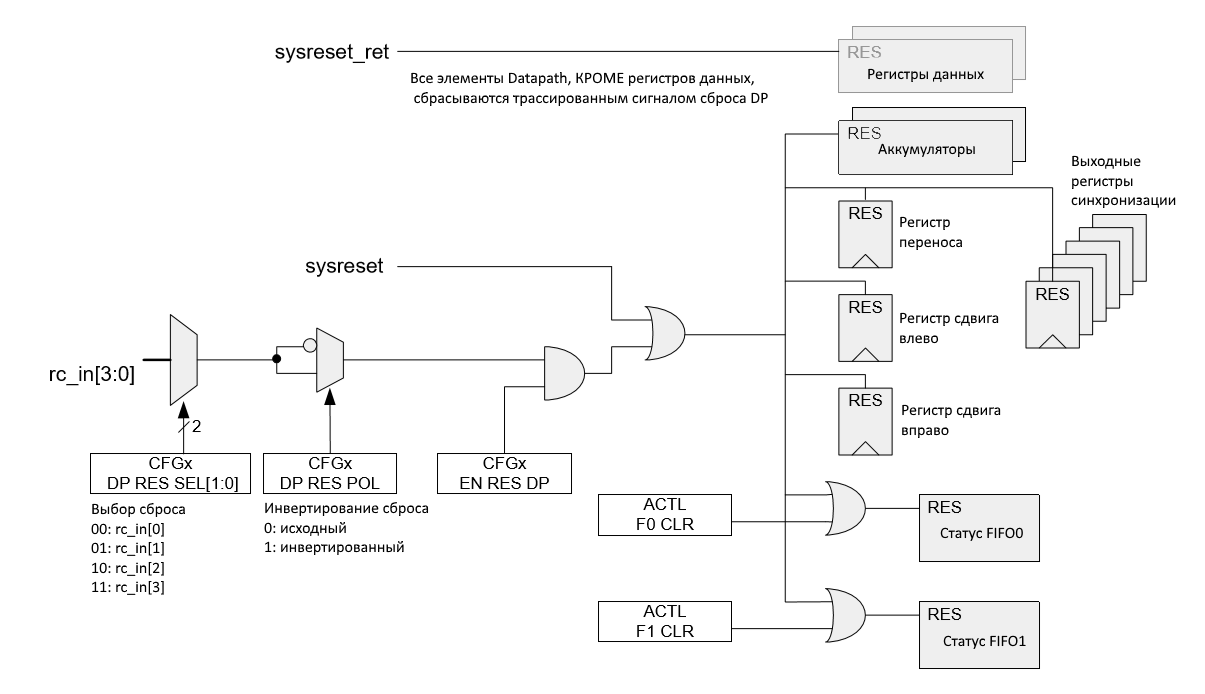

Figura 21-40. Redefinir estrutura PLD.Controle de redefinição de caminho de dadosA Figura 21-41 mostra o sistema de redefinição do Datapath. A liberação rastreada se aplica a todos os registros e estados do Datapath, exceto os registros de dados D0 e D1. Registradores de dados são persistentes. O conteúdo do FIFO não é definido após a redefinição, pois está localizado na RAM.

Figura 21-41. Estrutura de redefinição de caminho de dados.Controle de redefinição de status e controle

Figura 21-41. Estrutura de redefinição de caminho de dados.Controle de redefinição de status e controleA Figura 21-42 mostra o sistema de controle e redefinição de status. Os registros de controle / contador e status têm uma redefinição de rastreio comum, porém são ativados separadamente. Os registros de sobreposição de máscara / período e os controles auxiliares são salvos.

Figura 21-42. Redefinir gerenciamento e gerenciamento de status.

Figura 21-42. Redefinir gerenciamento e gerenciamento de status.21.3.4.3 Inicialização do Power On UDB (POR)

Registro e Inicialização do EstadoTabela 21-24. Inicialização dos estados UDB quando ativado

Inicialização de rastreamentoQuando ativado, o status das entradas e saídas de rastreio possui os seguintes recursos:

- todas as saídas UDB que direcionam dados para a matriz de rastreamento são mantidas em '0';

- todos os drivers que saem do rastreio e entram nas entradas UDB são zerados inicialmente.

Essa inicialização evita estados conflitantes durante o rastreamento, e a configuração inicial ocorre em uma sequência na qual a ordem não importa.

O final segue. Estamos preparando a tradução

mais recente da seção restante da documentação proprietária do Cypress sobre o UDB, ou seja, o Endereçamento UDB.