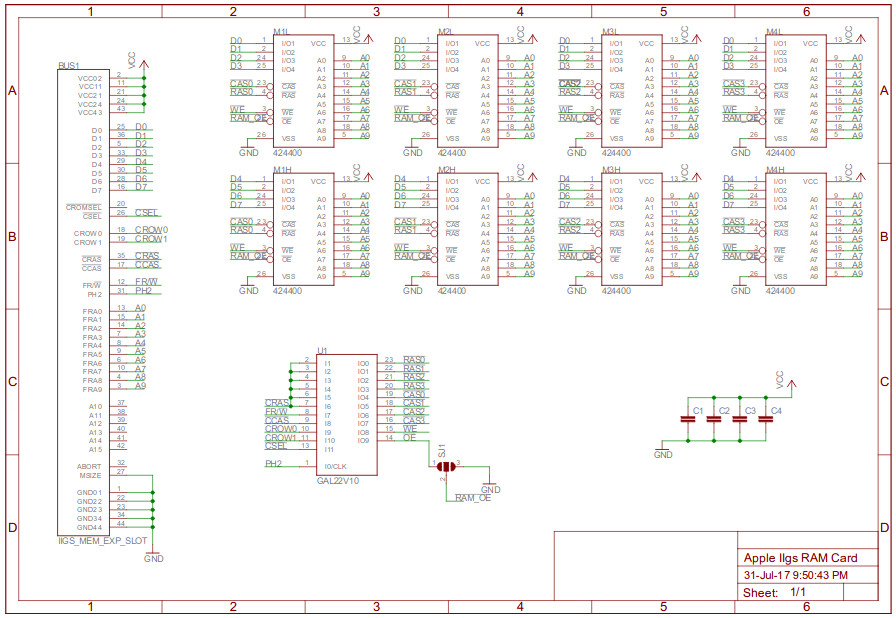

A placa de expansão de RAM proposta para o computador Apple IIgs é baseada nos chips NEC uPD424400-70 de vários módulos SIMM de 1 megabyte. Cada um desses microchips armazena petiscos de 1 M e está alojado em uma caixa do tipo SOJ de 26 pinos.

O computador Apple IIgs é alimentado por um processador 65C816 - 16 bits, mas com um barramento de dados de 8 bits. O cartão de expansão contém 4 MB de RAM. A memória é dividida em quatro linhas, 1 MB cada. A linha consiste em dois chips de mordidelas de 1 M, portanto, foram necessários oito chips.

O computador já possui um slot para a placa de expansão de RAM. Ele exibe todos os sinais necessários, o computador também cuida da regeneração da RAM dinâmica. Portanto, o cartão de expansão é bastante simples. O autor decidiu fazer a placa de tamanho pequeno, já que o custo de sua fabricação depende disso, além de colocar toda a lógica no FPGA GAL22V10.

Os seguintes sinais estão presentes no slot de expansão de RAM:

FRA0-FRA9 - endereço de célula multiplexada de 10 bits, servido diretamente às entradas de endereço de chips de RAM dinâmicos

CORO0, 1 - dois bits para selecionar uma das quatro linhas

/ CRAS - linha de endereço do sinal estroboscópico da RAM dinâmica

/ CCAS - endereço da coluna de sinalização da RAM dinâmica

FR / W - permissão de gravação na RAM, este sinal requer processamento adicional, veja abaixo

D0-D7 - barramento de dados, conectado diretamente às linhas de entrada / saída dos chips de RAM

/ CSEL - uma unidade lógica aparece nesta linha ao ler da RAM, deve ser invertida e alimentada às entradas / OE dos chips de RAM

MSIZE - informa ao computador o volume da linha: um - 256 kB, zero - 1 MB, aqui esta linha está conectada a um fio comum

14M, PH2CLK, A10-A15 - não participam do quadro proposto

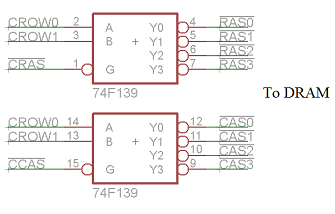

Os sinais / CRAS e / CCAS devem ser desmultiplexados para obter sinais separados / RAS e / CAS para cada linha. Para isso, o chip 74F139 é adequado (daqui em diante, entende-se que não haverá chips separados na placa, em vez deles, haverá um FPGA comum).

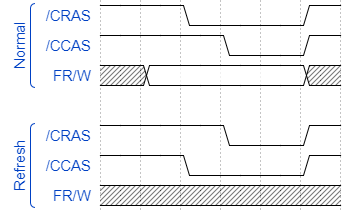

O sinal FR / W não pode ser alimentado diretamente na entrada / WE dos chips de RAM dinâmicos, e é por isso. Em uma operação normal de leitura e gravação, a linha / RAS primeiro se torna ativa (o que corresponde a um zero lógico) e depois a linha / CAS. Durante um ciclo dinâmico de regeneração de RAM, pelo contrário, a linha / CAS se torna ativa primeiro e, em seguida, / RAS se torna ativo. Mas os chips usados exigem que uma unidade apareça na linha / WE antes que a linha / RAS se torne ativa. E o sinal FR / W proveniente da Apple IIgs não atende a esse requisito. O estado de FR / W durante o ciclo de regeneração é indefinido. Portanto, é necessário um circuito que detecte um ciclo de regeneração e alimente uma unidade para / WE.

O primeiro passo é identificar o ciclo de regeneração. Abaixo está o gráfico de tempo:

A ideia do autor é usar uma trava "transparente". O sinal / CRAS é o sinal de entrada, / CCAS é o sinal de trava. Quando a unidade está ligada / CCAS, o dispositivo passa o sinal de entrada por si próprio: o estado da saída muda após o estado da entrada. Quando / CCAS passa de um para zero, a trava lembra o sinal na entrada e agora não muda na saída. Em uma operação normal de leitura / gravação em / CRAS, zero está presente no momento de alternar / CCAS de um para zero. E durante o ciclo de regeneração em / CRAS, também existe um no momento de alternar / CCAS para zero. Então, quando / CCAS voltar para um, a trava se tornará transparente novamente. Lembra uma flor fantástica de "Segredos do Terceiro Planeta", que pode ser tanto um "espelho" quanto uma "câmera".

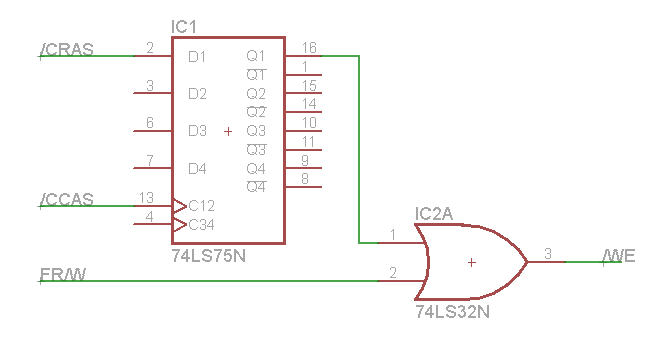

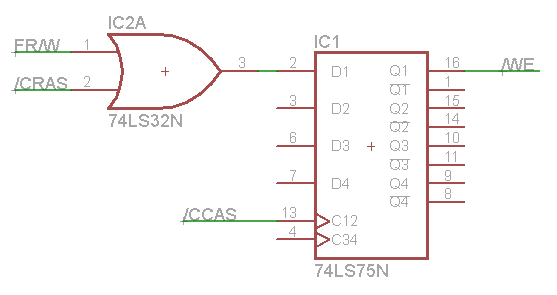

A princípio, o autor elaborou o seguinte esquema:

Porém, para sua transferência para o FPGA GAL22V10, são necessários dois pinos de saída. Portanto, o esquema teve que ser simplificado. Durante a operação normal, o sinal FR / W leva o valor desejado até clicar, então isso também é possível.

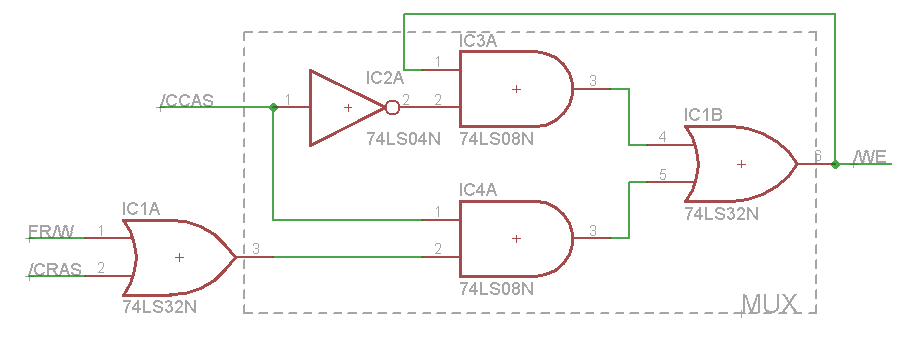

Uma trava "transparente" pode ser feita a partir de um multiplexador e, por sua vez, a partir de elementos lógicos. O esquema passa a ser o seguinte:

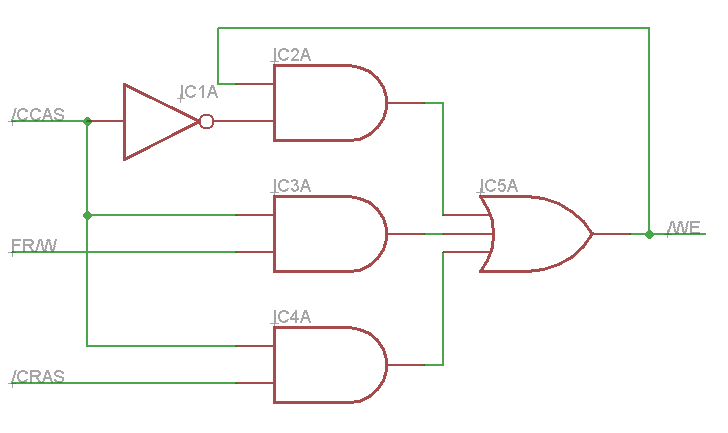

E após a simplificação - assim:

Esta opção é transferida para o FPGA. Para a compilação, o autor usou o WinCUPL. Este programa está no site da Atmel. É cru e constantemente voa, mas lidou perfeitamente com a tarefa. Programador - Genius G540.

O jumper SJ1 no quadro funciona assim. Se os pinos 1 e 2 estiverem conectados, o sinal / OE passa pelo FPGA. Se os pinos 2 e 3 estiverem conectados, ele será conectado a um fio comum. O autor não tinha certeza de que o esquema para identificar o ciclo de regeneração funcionaria. Portanto, ele adicionou esse jumper no caso de a configuração do FPGA precisar ser refeita.

Como tudo funcionou, não é necessário soldar os pinos, basta conectar os terminais 1 e 2 com uma gota de solda.

Para reduzir o tamanho da placa, o autor aplicou um capacitor de energia a cada quatro chips de RAM e colocou os chips nos dois lados da placa.

Os microchips nos casos de SOJ são difíceis de soldar, e especialmente de soldar, com um ferro de soldar. O autor recomenda o uso de um secador de cabelo.

Expanda os chips corretamente. Na linha inferior, eles são invertidos. O pino 1 olha para baixo.

Alguns orifícios de passagem estão muito próximos das almofadas. Não provoque um curto-circuito com solda.

E as plataformas 1 e 2 para o jumper, pelo contrário, fecham.

Os capacitores C1 - C3 têm uma capacitância de 0,1 μF, C4 - 10 μF.

O autor encomendou os conselhos no OSH Park. O revestimento ENIG é aplicado - dourado, mas muito fino. Para cartuchos de jogos não é adequado - ele será apagado rapidamente. E aqui a placa foi colocada no slot uma vez e mais não é removida de lá.

O autor agradece ao

GGLabs pelo circuito de uma placa similar, ajudou muito, obrigado!

O circuito final ficou assim:

Arquivos:

Firmware FPGA GAL22V10 , versão do programa WinCUPL 5.30.4 aplicada

Board , Eagle versão 7.1 software aplicado

Esboço em PDFGanhou!