Tradução da primeira parte da apresentação do Tesla Autonomy Investor Day sobre o desenvolvimento do computador completo para o piloto automático da Tesla. Preenchemos a lacuna entre as revisões da tese da apresentação e seu conteúdo.O texto da apresentação é traduzido próximo ao original. Perguntas ao orador - seletivamente com abreviações.Anfitrião: Olá pessoal. Desculpe pelo atraso. Bem-vindo ao nosso primeiro dia de direção autônoma. Espero que possamos fazer isso com mais regularidade para mantê-lo atualizado sobre nossos desenvolvimentos.

Há cerca de três meses, estávamos nos preparando para o relatório de ganhos do quarto trimestre com Ilon e outros executivos. Eu disse então que a maior lacuna nas conversas com investidores, entre o que vejo dentro da empresa e qual é sua percepção externa, é o nosso progresso na direção autônoma. E isso é compreensível, nos últimos dois anos falamos sobre o aumento da produção do Modelo 3, em torno do qual houve muita controvérsia. De fato, muita coisa aconteceu em segundo plano.

Trabalhamos em um novo chip para piloto automático, redesenhamos completamente a rede neural de visão de máquina e finalmente começamos a lançar o FSDC (Full Self-Driving Computer). Pensamos que era uma boa idéia abrir o véu, convidar a todos e contar tudo o que fizemos nos últimos dois anos.

Cerca de três anos atrás, queríamos usar, queríamos encontrar o melhor chip para a condução autônoma. Descobrimos que não há chip que foi projetado desde o início para redes neurais. Portanto, convidamos meu colega Pete Bannon, vice-presidente de design de circuitos integrados, a desenvolver esse chip para nós. Ele tem cerca de 35 anos de experiência em desenvolvimento de chips. Incluindo 12 anos no PASemi, que mais tarde foi adquirido pela Apple. Ele trabalhou em dezenas de diferentes arquiteturas e implementações e foi o designer-chefe do Apple iPhone 5, pouco antes de ingressar na Tesla. Também se junta a nós em Elon Musk. Obrigada

Ilon: Na verdade, eu iria apresentar Pete, mas como eles já fizeram isso, acrescentarei que ele é simplesmente o melhor arquiteto de sistemas e circuitos integrados do mundo que conheço. É uma honra que você e sua equipe na Tesla. Por favor, conte-nos sobre o trabalho incrível que você fez.

Pete: Obrigado Ilon. Tenho o prazer de estar aqui esta manhã e é muito bom contar sobre todo o trabalho que meus colegas e eu fizemos aqui em Tesla nos últimos três anos. Vou falar um pouco sobre como tudo começou, e depois apresentarei o computador FSDC e um pouco sobre como ele funciona. Vamos nos aprofundar no próprio chip e considerar alguns detalhes. Descreverei como funciona o acelerador especializado de rede neural que projetamos e, em seguida, mostra alguns resultados, e espero que a essa altura você ainda não adormeça.

Fui contratado em fevereiro de 2016. Perguntei ao Ilon se ele estava pronto para gastar o necessário para criar esse sistema especializado, ele perguntou: "Vamos vencer?", Respondi: "Bem, sim, é claro", então ele disse "Estou no negócio" e tudo começou . Contratamos várias pessoas e começamos a pensar em como seria um chip projetado especificamente para uma condução totalmente autônoma. Passamos dezoito meses desenvolvendo a primeira versão e, em agosto de 2017, a lançamos para produção. Conseguimos o chip em dezembro, funcionou e realmente funcionou muito bem na primeira tentativa. Em abril de 2018, fizemos várias alterações e lançamos a versão B zero Rev. Em julho de 2018, o chip foi certificado e iniciamos a produção em larga escala. Em dezembro de 2018, a pilha de direção autônoma foi lançada em novos equipamentos e pudemos prosseguir com a conversão de carros da empresa e testes no mundo real. Março 2019 começamos a instalar um novo computador nos modelos S e X e, em abril - no modelo 3.

Portanto, todo o programa, desde a contratação dos primeiros funcionários até o lançamento completo nos três modelos de nossos carros, levou pouco mais de três anos. Este talvez seja o programa de desenvolvimento de sistemas mais rápido em que já participei. E realmente fala dos benefícios da alta integração vertical, permitindo que você faça design paralelo e acelere a implantação.

Em termos de objetivos, estávamos completamente focados apenas nos requisitos da Tesla, e isso simplifica muito a vida. Se você tem um único cliente, não precisa se preocupar com os outros. Um dos objetivos era manter a potência abaixo de 100 watts para podermos converter as máquinas existentes. Também queríamos reduzir custos para fornecer redundância para maior segurança.

No momento em que cutucamos o céu, argumentei que dirigir um carro exigiria um desempenho de rede neural de pelo menos 50 trilhões de operações por segundo. Portanto, queríamos obter pelo menos o máximo e melhor. Os tamanhos de lote determinam o número de itens com os quais você trabalha ao mesmo tempo. Por exemplo, as TPUs do Google têm um tamanho de pacote de 256 e você precisa aguardar até que você tenha 256 itens para processar antes de começar. Não queríamos esperar e desenvolvemos nosso mecanismo com o tamanho de um pacote. Assim que a imagem aparece, nós a processamos imediatamente para minimizar o atraso e aumentar a segurança.

Precisávamos de um processador gráfico para fazer algum pós-processamento. No início, ele ocupava bastante, mas assumimos que, com o tempo, se tornaria menor, pois as redes neurais estão ficando cada vez melhores. E isso realmente aconteceu. Assumimos riscos ao colocar um processador gráfico bastante modesto no design, e isso acabou sendo uma boa ideia.

A segurança é muito importante, se você não possui um carro protegido, não pode ter um carro seguro. Portanto, muita atenção é dada à segurança e, é claro, à segurança.

Em termos de arquitetura de chips, como Ilon mencionou anteriormente, em 2016 não havia acelerador criado originalmente para redes neurais. Todos simplesmente adicionaram instruções à CPU, GPU ou DSP. Ninguém fez desenvolvimento com 0. Portanto, decidimos fazer nós mesmos. Para outros componentes, adquirimos CPUs e GPUs industriais IP padrão, o que nos permitiu reduzir o tempo e os riscos de desenvolvimento.

Outra coisa que foi um pouco inesperada para mim foi a capacidade de usar comandos existentes no Tesla. A Tesla tinha excelentes equipes de desenvolvedores de fontes de alimentação, análise de integridade de sinal, design de caixa, firmware, software de sistema, desenvolvimento de placas de circuito e um programa de validação de sistema realmente bom. Conseguimos usar tudo isso para acelerar o programa.

É assim que parece. À direita, você vê os conectores de vídeo provenientes das câmeras do carro. Dois computadores autônomos no centro da placa, à esquerda - os conectores da fonte de alimentação e controle. Adoro quando uma solução se resume aos seus elementos básicos. Você tem um vídeo, um computador e energia, simples e claro. Aqui está a solução anterior do Hardware 2.5, que incluía o computador e que instalamos nos últimos dois anos. Aqui está um novo design para um computador FSD. Eles são muito parecidos. Obviamente, isso se deve às limitações do programa de modernização de carros. Gostaria de salientar que este é realmente um computador pequeno. É colocado atrás do porta-luvas e não ocupa metade do tronco.

Como eu disse anteriormente, existem dois computadores completamente independentes na placa. Eles são destacados em azul e verde. Nas laterais de cada SoC, você pode ver os chips DRAM. No canto inferior esquerdo, você vê os chips FLASH que representam o sistema de arquivos. Existem dois computadores independentes que inicializam e executam sob seu próprio sistema operacional.

Ilon: O princípio geral é que, se alguma peça falhar, a máquina poderá continuar se movendo. A câmera, o circuito de energia, um dos chips de computador da Tesla falha - a máquina continua em movimento. A probabilidade de falha deste computador é significativamente menor que a probabilidade de o motorista perder a consciência. Este é um indicador chave, pelo menos uma ordem de magnitude.

Pete: Sim, uma das coisas que fazemos para manter o computador funcionando são fontes de alimentação redundantes. O primeiro chip funciona em uma fonte de energia e o segundo em outra. O mesmo vale para as câmeras, metade das câmeras na fonte de alimentação estão marcadas em azul e a outra metade em verde. Ambos os chips recebem todo o vídeo e o processam de forma independente.

Do ponto de vista da direção, a sequência é coletar muitas informações do mundo ao seu redor, temos não apenas câmeras, mas também radares, GPS, mapas, estabilizador de giroscópio (IMU), sensores ultrassônicos ao redor do carro. Temos um ângulo de direção, sabemos como deve ser a aceleração de um carro. Tudo isso se reúne para formar um plano. Quando o plano estiver pronto, os dois computadores trocam suas versões do plano para garantir que eles correspondam.

Supondo que o plano seja o mesmo, emitimos sinais de controle e acionamos. Agora que você está se movendo com os novos controles, certamente deseja testá-lo. Verificamos que os sinais de controle transmitidos coincidem com o que pretendemos transmitir aos atuadores no carro. Sensores são usados para verificar se o controle está realmente ocorrendo. Se você pedir que o carro acelere, diminua a velocidade ou vire à direita ou à esquerda, você pode olhar para os acelerômetros e garantir que isso esteja realmente acontecendo. Há redundância e duplicação significativas de nossos dados e de nossos recursos de monitoramento de dados.

Vamos falar sobre o chip. É empacotado em um BGA de 37,5 mm com 1600 pinos, a maioria dos quais são de potência e terra. Se você remover a tampa, poderá ver o substrato e o cristal no centro. Se você separar o cristal e virá-lo, verá 13.000 saliências C4 espalhadas pela superfície. Abaixo estão as doze camadas de metal do circuito integrado. Este é um processo FinFET CMOS de 14 nanômetros, medindo 260 mm.sq., um pequeno circuito. Para comparação, um chip de telefone celular convencional é de cerca de 100 mm2. Um processador gráfico de alto desempenho terá cerca de 600-800 mm.kv. Então, nós estamos no meio. Eu chamaria isso de média dourada, esse é um tamanho conveniente para montagem. Existem 250 milhões de elementos lógicos e 6 bilhões de transistores que, apesar de eu estar trabalhando nisso o tempo todo, me surpreendem. O chip é fabricado e testado de acordo com o padrão automotivo AEC Q100.

Eu iria ao redor do chip e explicaria todas as suas partes. Vou na mesma ordem que o pixel que sai da câmera. No canto superior esquerdo, você pode ver a interface da câmera. Podemos pegar 2,5 bilhões de pixels por segundo, o que é mais do que suficiente para todos os sensores disponíveis. Uma rede que distribui dados de um sistema de memória para controladores de memória nas bordas direita e esquerda do chip. Usamos LPDDR4 padrão operando a uma velocidade de 4266 gigabits por segundo. Isso nos fornece uma taxa de transferência máxima de 68 gigabytes por segundo. Essa é uma largura de banda muito boa, mas não excessiva, estamos tentando permanecer no meio termo. O processador de processamento de imagem possui um pipeline interno de 24 bits, o que nos permite usar totalmente os sensores HDR que estão no carro. Ele realiza o mapeamento avançado de tons, o que ajuda a realçar melhor os detalhes e as sombras, e também realiza a redução avançada de ruído, o que simplesmente melhora a qualidade geral das imagens que usamos em uma rede neural.

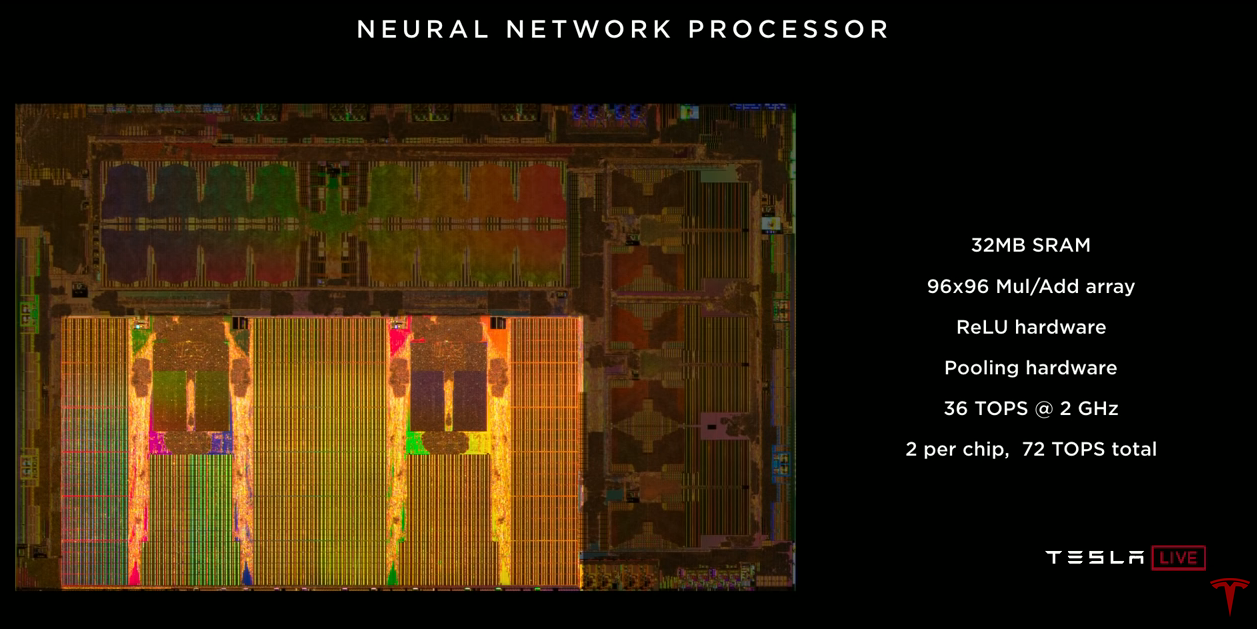

O próprio acelerador de rede neural. Existem dois no chip. Cada um deles possui 32 megabytes de SRAM para armazenar resultados temporários. Isso minimiza a quantidade de dados que precisamos transferir para o chip e vice-versa, o que ajuda a reduzir o consumo de energia. Cada um contém uma matriz de multiplicadores 96x96 com acumulação, o que nos permite realizar quase 10.000 operações MUL / ADD por ciclo. Existe um acelerador ReLU dedicado, um acelerador de pool. Cada um deles fornece 36 trilhões de operações por segundo, operando a uma frequência de 2 GHz. Dois aceleradores em um chip fornecem 72 trilhões de operações por segundo, o que é notavelmente mais alto que o objetivo de 50 trilhões.

O codificador de vídeo, o vídeo do qual usamos no carro para muitas tarefas, incluindo a saída de imagens da câmera de visão traseira, a gravação de vídeo e a gravação de dados na nuvem, Stuart e Andrew falarão sobre isso mais tarde. Um processador gráfico bastante modesto está localizado no chip. Ele suporta números de ponto flutuante de 32 e 16 bits. Também 12 processadores A72 de uso geral de 64 bits. Eles operam com uma frequência de 2,2 GHz, aproximadamente 2,5 vezes maior que o desempenho da solução anterior. O sistema de segurança contém dois processadores que operam no modo de passo de bloqueio. Este sistema toma a decisão final se é seguro transmitir sinais de controle para os acionamentos do veículo. É aqui que os dois aviões se reúnem e decidimos se é seguro avançar. E, finalmente, um sistema de segurança cuja tarefa é garantir que apenas o software Tesla assinado com criptografia seja usado neste chip.

Eu disse a você muitos indicadores de desempenho diferentes e acho que seria útil olhar para o futuro. Consideraremos uma rede neural de nossa câmera (estreita). São necessários 35 bilhões de operações. Se usarmos todas as 12 CPUs para processar esta rede, podemos fazer 1,5 quadros por segundo, é muito lento. Absolutamente não o suficiente para dirigir um carro. Se usássemos GPUs com 600 GFLOPs para a mesma rede, obteríamos 17 quadros por segundo, o que ainda não é suficiente para dirigir um carro com 8 câmeras. Nosso acelerador de rede neural pode produzir 2100 quadros por segundo. Você pode ver que a quantidade de computação na CPU e na GPU é insignificante em comparação com o acelerador de rede neural.

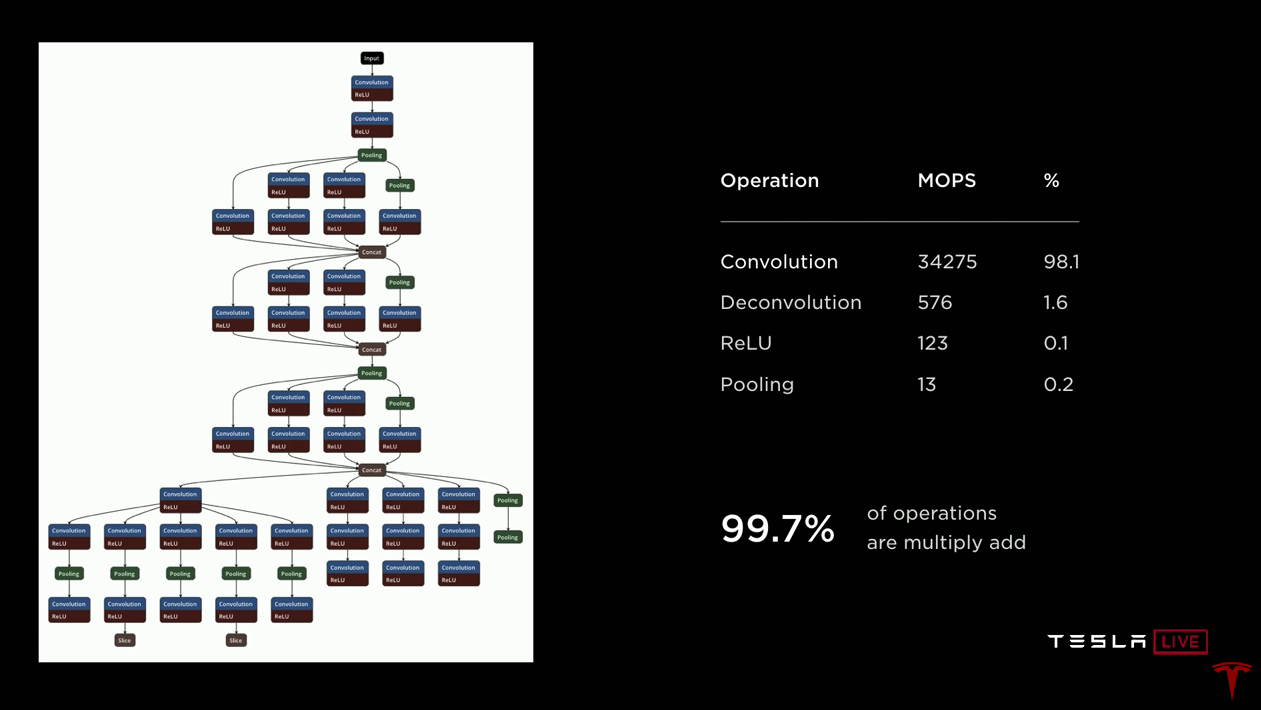

Vamos falar sobre um acelerador de rede neural. Vou beber apenas água. À esquerda, aqui está um desenho de uma rede neural para lhe dar uma idéia do que está acontecendo. Os dados chegam ao topo e passam por cada um dos blocos. Os dados são transmitidos ao longo das setas para vários blocos, que geralmente são convoluções ou inversas com funções de ativação (ReLUs). Blocos verdes combinam camadas. É importante que os dados recebidos por um bloco sejam usados pelo próximo bloco e você não precise mais deles - você pode jogá-los fora. Portanto, todos esses dados temporários são criados e destruídos ao passar pela rede. Não há necessidade de armazená-los fora do chip na DRAM. Portanto, nós os armazenamos apenas na SRAM, e em alguns minutos explicarei por que isso é muito importante.

Se você olhar para o lado direito, verá que nesta rede de 35 bilhões de operações, quase todas são convoluções, essencialmente produtos escalares, o restante é deconvolução (convoluções reversas), também baseada no produto escalar, e então ReLU e pooling são relativamente simples operações. Portanto, se você estiver desenvolvendo um acelerador, concentre-se na implementação de produtos escalares com base na adição com acumulação e os otimize. Mas imagine que você acelere essa operação em 10.000 vezes e 100% se transforme em 0,1%. De repente, a ReLU e as operações de pooling se tornam muito significativas. Portanto, nossa implementação inclui aceleradores dedicados para processamento e pool de ReLU.

O chip opera com um orçamento de calor limitado. Precisávamos ter muito cuidado com a forma como queimamos energia. Queremos maximizar a quantidade de aritmética que podemos fazer. Portanto, escolhemos adição inteira de 32 bits, que consome 9 vezes menos energia que a adição de ponto flutuante. E escolhemos a multiplicação inteira de 8 bits, que também consome significativamente menos energia que outras operações de multiplicação e provavelmente possui precisão suficiente para obter bons resultados. Quanto à memória. O acesso à DRAM externa é cerca de cem vezes mais caro em termos de consumo de energia do que o uso da SRAM local. É claro que queremos aproveitar ao máximo a SRAM local.

Do ponto de vista do gerenciamento, eis os dados publicados em um artigo de Mark Horowitz, onde ele examinou criticamente quanta energia é necessária para executar uma única instrução em um processador inteiro comum. E você vê que a operação de adição consome apenas 0,15% da energia total. Todo o resto está sobrecarregado para gerenciamento e muito mais. Portanto, em nosso projeto, nos esforçamos para nos livrar de tudo isso o máximo possível. O que realmente nos interessa é aritmética.

Então, aqui está o design que terminamos. Você pode ver que nele o local principal é ocupado por 32 megabytes de SRAM, eles são deixados, à direita, no centro e na parte inferior. Todos os cálculos são realizados na parte central superior. A cada ciclo, lemos 256 bytes de dados de ativação da matriz SRAM, 128 bytes de pesos da matriz SRAM e os combinamos em uma matriz 96x96, que executa 9000 adições com acumulação por ciclo a 2 GHz. Isso é apenas 36,8 trilhões. operações. Agora que terminamos o produto escalar, carregamos os dados, os transmitimos pela ReLU dedicada, opcionalmente por meio de pull, e finalmente os colocamos no buffer de gravação, onde todos os resultados são agregados. E então escrevemos 128 bytes por relógio de volta à SRAM. E tudo isso acontece continuamente. Trabalhamos com produtos escalares, enquanto descarregamos resultados anteriores, executamos puxamentos e escrevemos os resultados de volta à memória.

Se você empilhar tudo em 2 GHz, precisará de 1 terabyte por segundo de largura de banda SRAM para dar suporte à operação. E o ferro fornece isso. Um terabyte por segundo de largura de banda por acelerador, dois aceleradores por chip - dois terabytes por segundo.O acelerador tem um conjunto relativamente pequeno de comandos. Há uma operação de leitura de DMA para carregar dados da memória, uma operação de gravação de DMA para fazer upload de resultados de volta à memória. Três instruções de convolução (convolução, deconvolução, produto interno). Duas operações relativamente simples são a operação por turnos e por elementos (eltwise). E, claro, a operação de parada quando os cálculos terminarem.Tivemos que desenvolver um compilador de rede neural. Adotamos uma rede neural treinada por nossa equipe de desenvolvimento, na forma em que era usada no hardware antigo. Quando você o compila para uso em um novo acelerador, o compilador realiza a fusão de camadas, o que nos permite aumentar o número de cálculos para cada chamada à SRAM. Também realiza a suavização dos acessos à memória. Realizamos preenchimento de canal para reduzir conflitos entre bancos de memória. A alocação de memória também leva em consideração os bancos SRAM. É o caso em que o processamento de conflitos pode ser implementado no hardware. Porém, com a implementação de software, economizamos em hardware devido a alguma complexidade de software. Também inserimos automaticamente operações de DMA para que os dados cheguem para os cálculos no prazo, sem interromper o processamento. No final, geramos o código,pesa dados, compacta e adiciona uma soma de verificação CRC para confiabilidade. A rede neural é carregada na SRAM na inicialização e existe o tempo todo.Assim, para iniciar a rede, você especifica o endereço do buffer de entrada, que contém uma nova imagem que acabou de chegar da câmera; defina o endereço do buffer de saída; defina o ponteiro para o peso da rede; vamos lá O acelerador "entra em si" e passa sequencialmente por toda a rede neural, geralmente por um ou dois milhões de ciclos de clock. Após a conclusão, você recebe uma interrupção e pode pós-processar os resultados.Voltando aos resultados. Nosso objetivo era atingir 100 watts. Medições em carros que dirigem com uma pilha cheia de piloto automático mostraram que dissipamos 72 watts. Isso é um pouco maior do que no projeto anterior, mas uma melhoria significativa no desempenho é uma boa desculpa. Desses 72 watts, cerca de 15 watts são consumidos em redes neurais. O custo desta solução é de cerca de 80% do que pagamos anteriormente. Em termos de desempenho, pegamos a rede neural (estreita) da câmera, que eu já mencionei, com 35 bilhões de operações, a lançamos em equipamentos antigos e recebemos 110 quadros por segundo. Pegamos os mesmos dados e a mesma rede, compilamos para o novo computador FSD e, usando todos os quatro aceleradores, podemos processar 2300 quadros por segundo.Ilon:Acho que esse talvez sejao slide mais significativo de Pete: nunca trabalhei em um projeto em que a melhoria da produtividade fosse superior a 3. Foi divertido. Comparado com a solução nvidia Drive Xavier, o chip fornece 21 trilhões. operações, enquanto o nosso FSDC com dois chips - 144 trilhões. operações.Concluindo, acho que criamos uma solução que oferece um desempenho extraordinário de 144 trilhões. operações para processar uma rede neural. Possui excelentes características de potência. Conseguimos espremer toda essa produtividade no orçamento de calor que tínhamos. Isso permite implementar uma solução de duplicação. O computador tem um custo moderado e, o que é realmente importante, o FSDC fornecerá um novo nível de segurança e autonomia nos carros da Tesla, sem afetar seu custo e quilometragem. Estamos todos ansiosos por isso.Ilon: Se você tiver dúvidas sobre equipamentos, faça-as agora.A razão pela qual pedi a Pete que fizesse uma pesquisa detalhada, muito mais detalhada do que talvez a maioria das pessoas teria apreciado mergulhar em um computador Tesla FSD é a seguinte. À primeira vista, parece incrível como poderia acontecer que a Tesla, que nunca havia projetado esses chips antes, criou o melhor chip do mundo. Mas foi exatamente isso que aconteceu. E não apenas o melhor por uma pequena margem, mas o melhor por uma margem enorme. Todos os Tesla fabricados agora têm este computador. Mudamos da solução Nvidia para S e X há cerca de um mês e o Modelo 3 há cerca de dez dias. Todos os carros produzidos possuem todo o hardware necessário e tudo o que é necessário para uma direção totalmente autônoma. Vou dizer novamente: todos os carros Tesla produzidos agora,tenha tudo o que você precisa para uma direção totalmente autônoma. Tudo que você precisa fazer é melhorar o software. Ainda hoje, você pode dirigir carros com uma versão para desenvolvedores de software de direção autônoma aprimorado. Você verá por si mesmo. Perguntas.P: você tem a capacidade de usar outras funções de ativação além da ReLU?Pete: sim, temos um sigmóide, por exemplo.P: talvez valha a pena mudar para um processo de fabricação mais compacto, talvez 10 nm ou 7 nm?Pete: no momento em que começamos a projetar, nem todos os IPs que queríamos obter estavam disponíveis em 10 nmIlon: vale a pena notar que concluímos esse design há cerca de um ano e meio e iniciamos a próxima geração. Hoje não estamos falando da próxima geração, mas já estamos no meio do caminho. Tudo isso é óbvio para o chip da próxima geração, nós fazemos.P: O computador foi projetado para funcionar com câmeras. Posso usá-lo com o lidar?Ilon:Lidar é uma decisão desastrosa e qualquer pessoa que confie no lidar está condenada. Condenado. Caro Caros sensores que não são necessários. É como ter um monte de aplicativos desnecessários caros. Um pequeno não é nada, mas um monte já é um pesadelo. Isso é estúpido, você verá.P: Você pode avaliar o impacto do consumo de energia na quilometragem?Pete: Para o Modelo 3, o consumo-alvo é de 250 watts por milha.Ilon:Depende da natureza da direção. Na cidade, o efeito será muito maior do que na rodovia. Você dirige na cidade por uma hora e tem uma solução hipotética que consome 1 kW. Você perderá 6 km no modelo 3. Se a velocidade média for de 25 km / h, você perderá 25%. O consumo do sistema tem um enorme impacto na quilometragem em uma cidade onde achamos que haverá uma grande parte do mercado de robotax, portanto a energia é extremamente importante.P: Qual é a confiabilidade da sua tecnologia em termos de IP, você não fornecerá IP de graça?Pete: Registramos uma dúzia de patentes para essa tecnologia. Isso é álgebra essencialmente linear, que eu acho que você não pode patentear. (Ilon ri)P:seu microcircuito pode fazer alguma coisa, talvez criptografar todos os pesos para que sua propriedade intelectual permaneça lá dentro e ninguém possa roubá-laIlon: Ah, eu gostaria de conhecer alguém que possa fazer isso. Eu o contrataria em um instante. Este é um problema muito difícil. Mesmo se você puder extrair os dados, precisará de uma quantidade enorme de recursos para usá-los de alguma forma.A grande vantagem sustentável para nós é a frota. Ninguém tem uma frota. Os pesos são atualizados e aprimorados constantemente com base em bilhões de milhas percorridas. A Tesla tem cem vezes mais carros com o hardware necessário para o treinamento do que todos os outros combinados. Até o final deste trimestre, teremos 500.000 veículos com 8 câmeras e 12 sensores ultrassônicos. Em um ano, teremos mais de um milhão de carros com o FSDC. Esta é apenas uma enorme vantagem de dados. Isso é semelhante ao modo como o mecanismo de pesquisa do Google tem uma enorme vantagem, porque as pessoas o usam e treinam o Google com suas consultas.Anfitrião:Uma coisa a lembrar sobre o nosso FSD é que ele pode trabalhar com redes neurais muito mais complexas para um reconhecimento de imagem muito mais preciso. É hora de falar sobre como realmente obtemos essas imagens e como as analisamos. Aqui temos um diretor sênior da AI - Andrey Karpaty, que explicará tudo isso para você. Andrei é PhD pela Universidade de Stanford, onde estudou ciência da computação com ênfase em reconhecimento e aprendizado profundo.Ilon: Andrey, por que você não começa, vamos lá. Muitos médicos vieram de Stanford, isso não importa. Andrey está dando um curso de visão computacional em Stanford, que é muito mais importante. Por favor, fale sobre você.

(A tradução acabou não sendo uma questão rápida, não sei se tenho o suficiente para a segunda parte sobre o sistema de treinamento em redes neurais, embora me pareça o mais interessante.)