Uma pequena introdução:

A idéia de escrever seu próprio núcleo surgiu após a aprovação de um seminário escolar sobre circuitos digitais na cidade de Tomsk . Nesse evento, foi feita uma introdução às linguagens atuais de descrição de hardware (Verilog HDL e VHDL), bem como ao pequeno núcleo do processador schoolMIPS . Para entender a estrutura dos núcleos, decidiu-se inventar sua própria bicicleta, seguindo o caminho de desenvolvimento do schoolMIPS, mas usando outro sistema de comando como base. Devido à crescente popularidade do RISC-V e à abertura do seu sistema de comando (o MIPS não tinha um sistema de comando aberto no momento em que o kernel foi gravado), um conjunto de instruções do RISC-V, ou seja, RV32I, foi escolhido para o desenvolvimento do futuro kernel. O RV32I possui um pequeno conjunto de instruções básicas (37 excluindo as especiais) e pode ser expandido, se desejado, por exemplo, adicionando instruções de multiplicação e divisão inteiras (RV32M) ou suporte para instruções reduzidas (RV32C). Além disso, este projeto foi concebido como educacional, por isso foi decidido maximizar a visibilidade do kernel para demonstrar efetivamente seu trabalho.

Por analogia com o schoolMIPS, as seguintes versões do kernel foram implementadas:

- Versão de ciclo único (00_simple_risc_v_cpu).

- Uma versão de ciclo único com suporte para instruções lw / sw (carregar palavra / armazenar palavra) (01_simple_risc_v_cpu_lwsw).

- Versão do pipeline (transportador de 5 estágios) (02_pipe_risc_v_cpu).

Atualmente, a próxima versão do kernel é descrita (03_pipe_risc_v_cpu_fc) com um conjunto completo de comandos RV32I (sem levar em consideração alguns especiais).

No decorrer da descrição do kernel, foram pensadas maneiras de melhorar a visibilidade do trabalho, depuração e verificação. Atualmente implementados os seguintes métodos:

Adicionando um módulo VGA de texto de depuração (para duas ramificações de kernel de ciclo único). A inclusão deste módulo permite rastrear simultaneamente o valor de 32 registros na tela do monitor, o que não é possível ao usar a saída de informações em indicadores de sete segmentos. Nas figuras apresentadas abaixo, o kernel calcula os números de Leonardo e exibe informações no módulo de depuração correspondente;

hex_display e DebugScreenCoreSaída de informações em indicadores de sete segmentos:

Saída de informações no visor VGA:

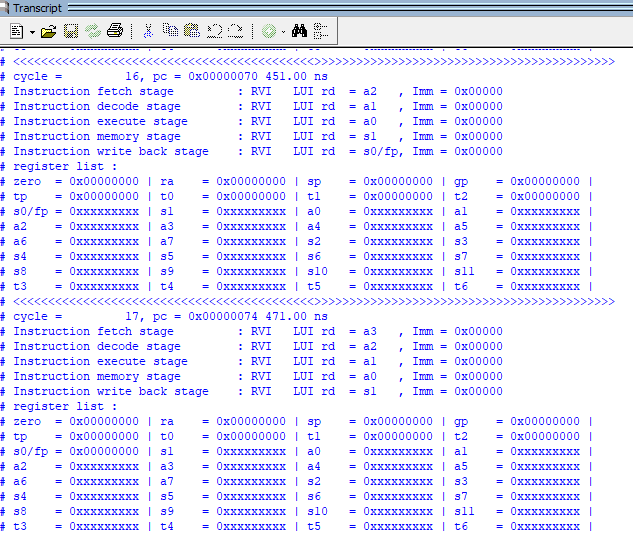

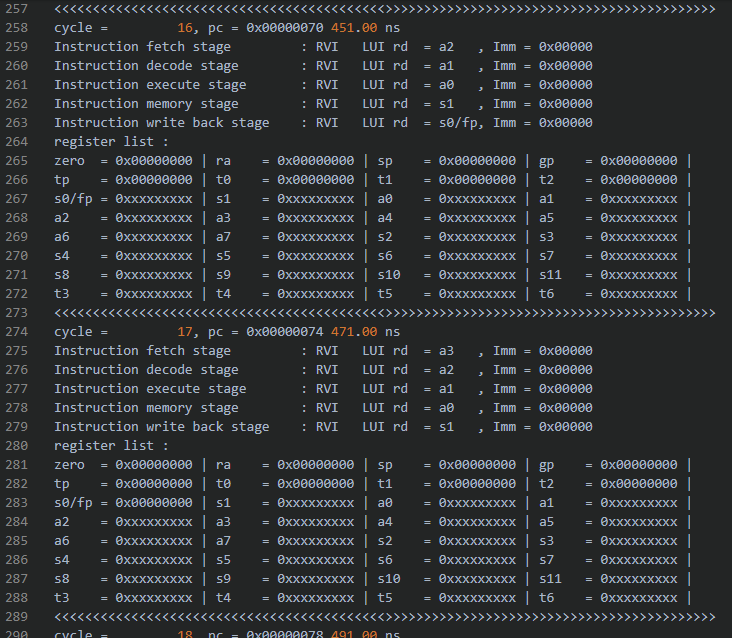

Adicionando mensagens ao terminal do simulador sobre o status do arquivo de registro e executando atualmente as instruções. Este método permite analisar melhor a operação do kernel nos estágios iniciais de desenvolvimento, mas nem sempre é conveniente;

TerminalInicialização do arquivo de registro:

Alterar valor de sp:

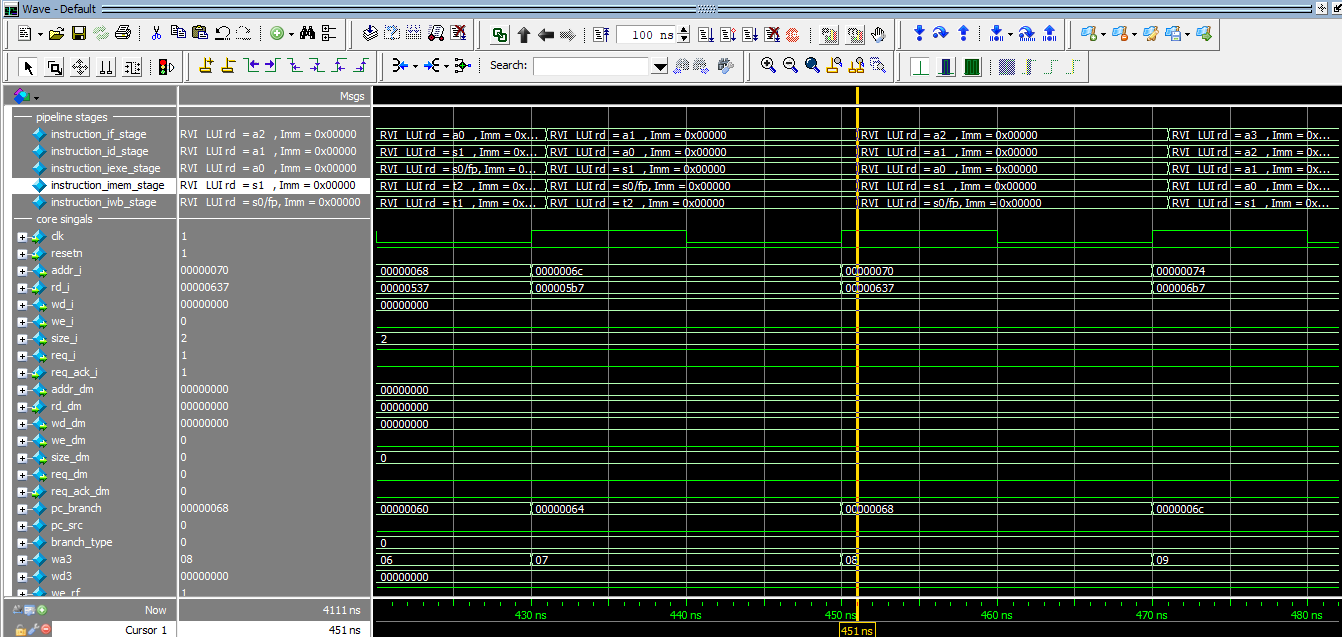

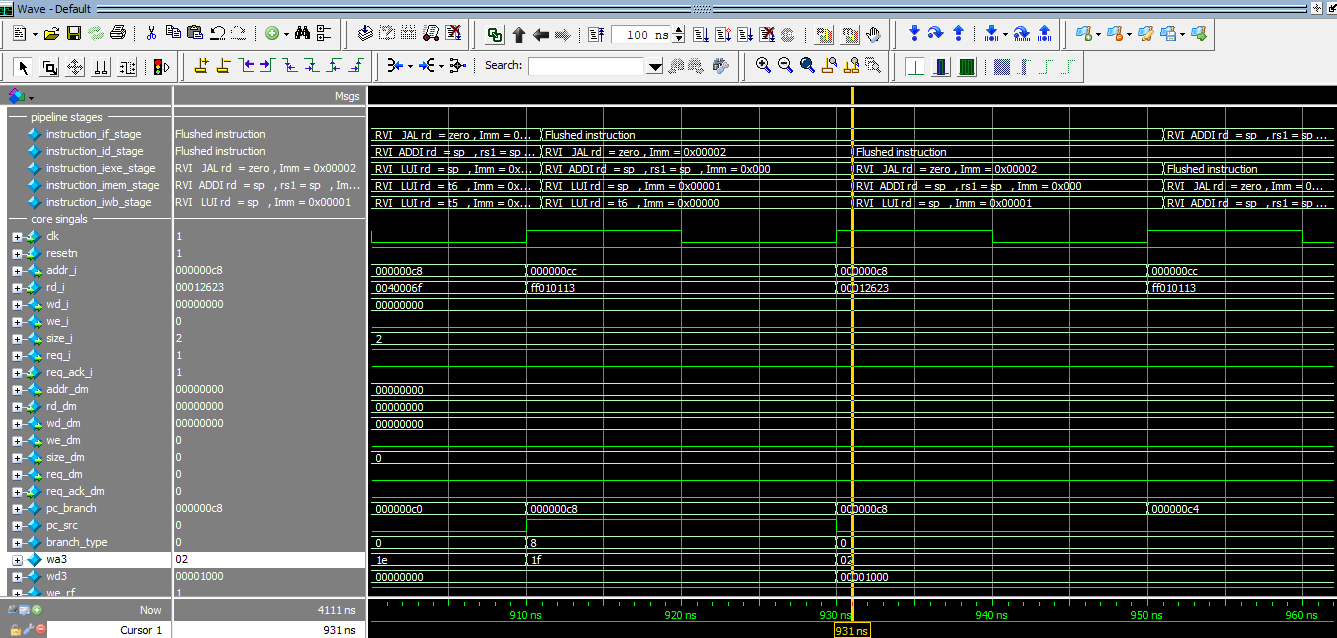

Adicionando variáveis de string à forma de onda com a exibição de instruções executáveis. Usando essas variáveis de cadeia, o desenvolvedor pode rastrear a configuração correta dos sinais de controle em todos os estágios do pipeline;

Forma de ondaInicialização do arquivo de registro:

Alterar valor de sp:

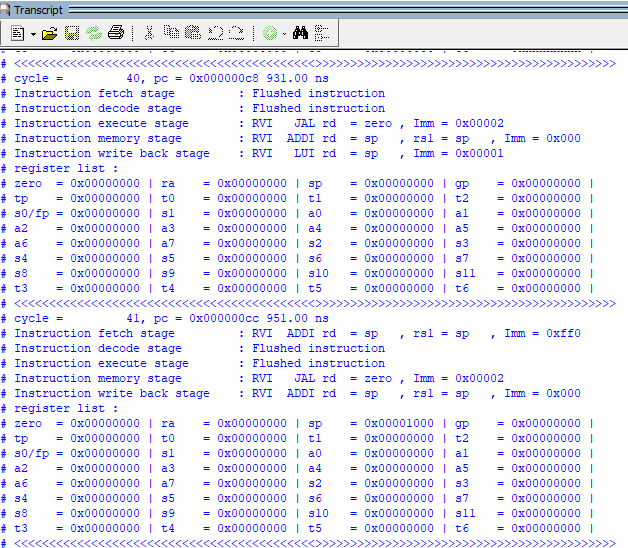

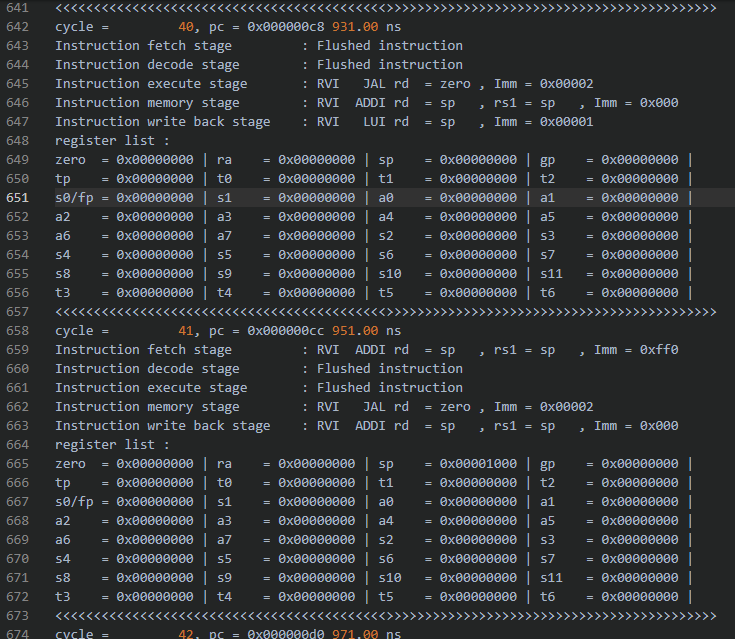

Adicionando a capacidade de gravar informações de depuração sobre o estado do kernel em um arquivo de texto. O status do arquivo de registro é apresentado em forma de tabela e as instruções / instruções atualmente executadas pelo kernel também são indicadas. É um análogo de 2 pontos, mas permite mais manipulações com as informações recebidas;

Arquivo de textoInicialização do arquivo de registro:

Alterar valor de sp:

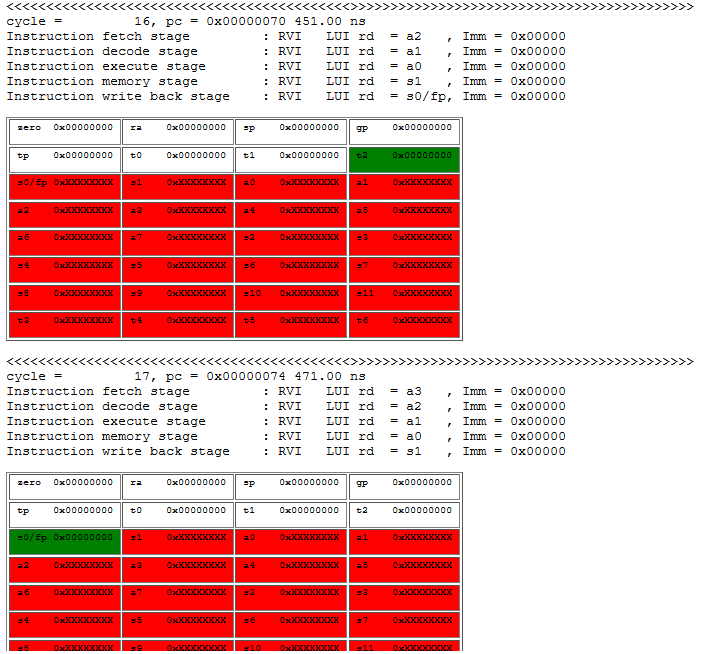

Adicionando a capacidade de gravar informações de depuração sobre o estado do kernel em um arquivo HTML. O status do arquivo de registro é apresentado em forma de tabela com notas sobre a alteração dos valores das células, bem como as instruções atualmente sendo executadas pelo kernel. É um análogo dos parágrafos 2 e 4, mas, além deles, permite indicar convenientemente uma alteração nos dados. Como pode ser visto nas figuras abaixo, se o valor do registro não foi definido, os registros são destacados em vermelho (registros s0 / fp - t6). No ciclo 17, o valor do registro s0 / fp muda e a célula é destacada em verde.

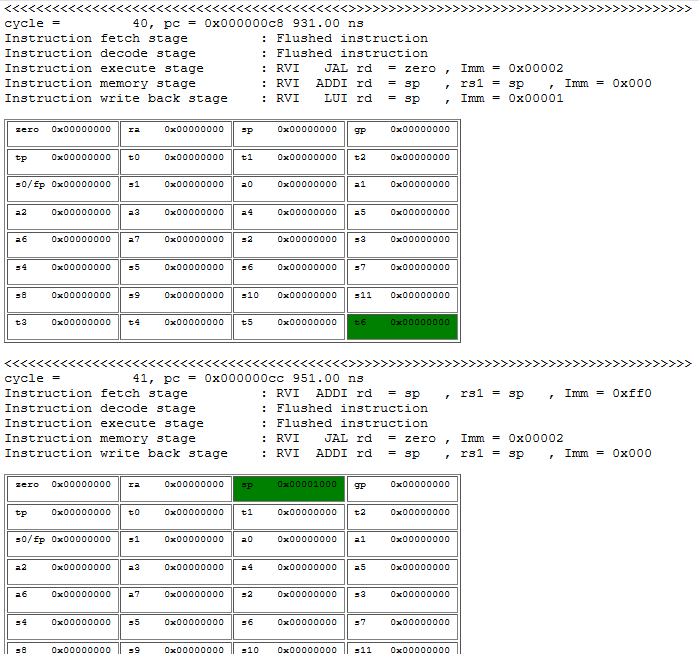

No ciclo 41, o valor 0x00010000 é carregado no registro sp.

Arquivo HTMLInicialização do arquivo de registro:

Alterar valor de sp:

Comparação de ramificações do kernel:Instruções de kernel atualmente suportadas para diferentes ramificações:

Periféricos suportados:

Idiomas suportados para escrever programas:

Recursos FPGA necessários para o kernel (nf_cpu):

EP4CE22F17C6 (de0_nano):

10M50DAF484C7G (de10_lite):

Desenvolvimento de projetos.

O que está planejado para ser feito no futuro:

- adicione todas as instruções do RV32I (no estágio de descrição);

- implementar depuração;

- adicione um controlador DMA (DMA);

- adicione suporte para outros pneus AXI, Avalon, Wishbone;

- adicionar memória cache (cache);

- integrar vários periféricos (SPI, TWI (I2C), Ethernet (10 base-t));

- adicionar controlador de interrupção;

- portar versões diferentes para outras placas de depuração;

- adicione outros métodos para aumentar a visibilidade do kernel;

- executando o RTOS, por exemplo, zephyr .

Recomendações e sugestões para o desenvolvimento do núcleo também são aceitas.

Link para o repositório: nanoFOX .