Em quase todos os segundos tópicos em Habré relacionados à astronáutica ou eletrônica, o tópico resistência à radiação aparece. O tópico da substituição de importações de uma base de elemento resistente a radiantes é veiculado nas notícias sobre exploração espacial doméstica, mas, ao mesmo tempo, Elon Musk usa chips convencionais baratos e se orgulha disso. E os israelenses em Bereshit usavam um processador radiante e também se orgulham disso. E, em princípio, a indústria microeletrônica na Rússia vive em grande parte devido a uma ordem estatal com os requisitos relevantes. Observar disputas regulares sobre como criar satélites adequadamente mostra que o treinamento dos participantes geralmente é baixo e sua argumentação é sobrecarregada com estereótipos, fatos ouvidos acidentalmente e conhecimentos retirados do contexto, ultrapassados há muitos anos. Eu pensei que ler isso não é mais possível, portanto, queridos analistas, se sintam confortáveis em seus sofás, e começarei uma pequena (realmente grande) história sobre os equívocos mais populares sobre a resistência à radiação dos circuitos integrados.

Figura 1. Uma imagem bonita indispensável sobre a radiação cósmica e a frágil Terra.

Figura 1. Uma imagem bonita indispensável sobre a radiação cósmica e a frágil Terra.As teses mais populares sobre resistência à radiação usadas em disputas no espaço próximo são mais ou menos assim:

- Chips radiantes não são necessários. Os Kubsats voam perfeitamente nos comuns, na ISS são os laptops comuns da Lenovo, no Dragon existem microcircuitos comuns e até a NASA em Orion entregava microcircuitos comuns!

- É bem possível colocar microcircuitos muito antigos nos satélites, até o "desmoronamento solto", não sendo necessário nenhum desempenho sério lá. Mas sem alegria, em lugar nenhum, e, portanto, voar no lixo.

- A tese que complementa a anterior: microcircuitos radicalmente estáveis, em princípio, não pode ser feita com baixos padrões de projeto; portanto, o uso de componentes testados pelo tempo não é apenas justificado, mas também necessário.

- Para que o microcircuito seja resistente à radiação, é necessário e suficiente fazê-lo usando a tecnologia “silício em um isolador” ou “silício em safira”.

- Todos os microcircuitos “militares” são resistentes a rádio e todos os microcircuitos resistentes a rádio são “militares”.

Como você pode ver, algumas dessas teses se contradizem diretamente - o que é regularmente objeto de controvérsia ou motivo de conclusões incorretas de longo alcance.

Você precisa iniciar a conversa com um aviso importante: a resistência à radiação não é o centro do mundo e a única qualidade que deve ser adequada para uso no espaço ou em outros chips de ambientes agressivos. A resistência à radiação é apenas um requisito de uma série longa, que inclui confiabilidade, uma faixa de temperatura estendida, resistência a descargas eletrostáticas, resistência a vibrações - e confirmação confiável de todos os parâmetros acima, ou seja, certificação longa e cara. É importante tudo o que pode não permitir que o chip funcione por toda a vida útil necessária, e a maioria das aplicações de chips resistentes a radiantes implica a impossibilidade de reparo ou substituição. Por outro lado, se algo estiver errado com um dos parâmetros, o projetista do produto final poderá encontrar uma maneira de contornar a limitação - colocar o chip mais sensível à dose de radiação da parede espessa, monitorar o consumo atual do chip vulnerável ao efeito do tiristor e, se necessário, reiniciar sua energia. , ou termostato um chip com uma faixa de temperatura estreita. Ou talvez não seja encontrado, e a única maneira de resolver a tarefa será solicitar um novo resistente ao radar ASIC.

Também é útil lembrar que os desenvolvedores de sistemas para fins especiais são as mesmas pessoas que qualquer outro desenvolvedor. Muitos deles também gostam de escrever código para muletas cheias de crosta até o prazo de ontem e usar um hardware mais poderoso para que ele definitivamente funcione; alguns teriam usado o Arduino se tivesse sido devidamente certificado. E, é claro, as pessoas que definem tarefas para desenvolvedores de sistemas para fins especiais e desenvolvedores de microcircuitos raramente se sentem tímidas nos requisitos de confiabilidade, desempenho e resistência à alegria. Portanto, ainda são necessários padrões de design moderno em satélites - quero grandes quantidades de DRAM, processadores com vários núcleos e os FPGAs mais recentes. Eu já mencionei acima que as consequências de baixa resistência à radiação e outros problemas em potencial podem ser pelo menos parcialmente contornadas, portanto a falta de dados sobre o que exatamente precisa ser contornado que o status comercial dos chips é, em grande parte, impedida de usar toda essa magnificência dos desenvolvedores.

Efeitos de radiação

Os conceitos de "resistência à radiação" e "microcircuito resistente à radiação" são grandes simplificações. De fato, existem muitas fontes diferentes de radiação ionizante e elas podem afetar o funcionamento dos dispositivos eletrônicos de diferentes maneiras. Consequentemente, para diferentes aplicações, é necessária resistência a diferentes conjuntos de fatores de influência e diferentes níveis de exposição; portanto, um microcircuito "estável" projetado para operar em baixa órbita terrestre não é absolutamente necessário para funcionar normalmente ao analisar bloqueios em Chernobyl.

A radiação ionizante é denominada ionizante, porque a liberação de energia no volume de uma substância durante a frenagem das partículas que chegam ioniza a substância. Cada material possui sua própria energia necessária para a ionização e criação de um par de elétrons e buracos. Para o silício, isto é 3,6 eV, para o seu óxido - 17 eV, para o arseneto de gálio - 4,8 eV. Além disso, uma partícula recebida pode não ionizar um átomo, mas "movê-la" do lugar certo na estrutura cristalina (em silício, isso requer que 21 eV sejam transferidos para o átomo). Os pares elétron-buraco criados em uma substância podem ter efeitos diferentes nas propriedades elétricas e físicas e no comportamento do circuito elétrico. Os efeitos da radiação podem ser divididos em quatro grandes grupos: efeitos da dose total absorvida, efeitos da taxa de dose, efeitos causados pela entrada de partículas únicas e efeitos do deslocamento. Essa separação é um tanto arbitrária: por exemplo, a irradiação com uma corrente de íons pesados que causam efeitos únicos também leva a um conjunto de dose total absorvida.

Efeitos de doseA dose total absorvida de radiação é medida em rad, indicando a substância que absorve a radiação. 1 rad = 0,01 J / kg, ou seja, a quantidade de energia liberada em uma unidade de massa de uma substância. Menos comumente usada é uma unidade de medida de cinza igual a 100 rad (ou 1 J / kg). É importante entender que a dose absorvida em diferentes substâncias varia para o mesmo número de partículas ionizantes liberadas pela fonte de radiação (esta é a dose de exposição). No caso de microcircuitos de silício, o material desejado é o óxido de silício, porque o efeito sobre ele, e não sobre o silício, afeta principalmente as características elétricas do circuito, uma vez que a mobilidade dos orifícios no SiO2 à temperatura normal é tão pequena que eles se acumulam no óxido, criando carga positiva embutida. Os níveis típicos de resistência à dose de microcircuitos comerciais estão na faixa de 5 a 100 crad (Si), os níveis de resistência à radiação exigidos pelos clientes começam em 30 crad (Si) e terminam em torno de 1 grau (Si), dependendo da finalidade do microcircuito. A dose letal para humanos é de cerca de 6 cinza.

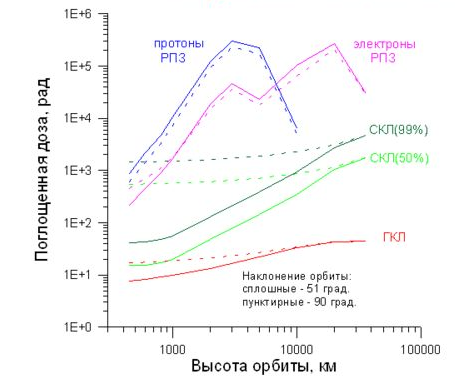

Figura 2. Exemplos de cálculos do conjunto da dose total absorvida ao longo de 10 anos em várias órbitas circulares para proteção de 1 g / cm ^ 2. Fonte - N.V. Kuznetsov, “Risco de radiação em órbitas próximas à Terra e trajetórias interplanetárias de naves espaciais”.

Figura 2. Exemplos de cálculos do conjunto da dose total absorvida ao longo de 10 anos em várias órbitas circulares para proteção de 1 g / cm ^ 2. Fonte - N.V. Kuznetsov, “Risco de radiação em órbitas próximas à Terra e trajetórias interplanetárias de naves espaciais”.Os efeitos da dose completa estão associados ao acúmulo dessa carga positiva em dielétricos e são manifestados nos esquemas CMOS de várias maneiras principais:

- A mudança na tensão limiar dos transistores decorrente do acúmulo de uma carga positiva no dielétrico da porta e a mudança no campo elétrico no canal do transistor. Para transistores de canal n, o limiar geralmente diminui (mas a dependência pode ser não monotônica) e para transistores de canal p aumenta, e o valor do deslocamento se correlaciona com a espessura do óxido de porta, ou seja, com os padrões de projeto. Os limiares dos transistores em circuitos com padrões de projeto aproximados podem mudar de modo a causar uma falha funcional (transistores de canal n param de fechar, transistores de canal p abertos); nas tecnologias submicrônicas, esse efeito é menos importante, mas em circuitos analógicos pode causar muita dor de cabeça.

- Ocorre corrente de fuga não controlada. Pode fluir da fonte do transistor para seu próprio dreno ou para um transistor adjacente. A causa dos vazamentos é o acúmulo de uma carga positiva, mas não no isolador do portão, mas no material isolante espesso. De fato, um transistor parasitário é formado paralelamente ao transistor principal, cuja tensão de porta é controlada por uma dose de radiação. A manifestação desse efeito é determinada pelas características da geometria da transição de um isolador de portão para um isolante, ou seja, depende muito mais de uma tecnologia específica do que dos padrões de projeto.

- Uma diminuição na mobilidade das transportadoras de carga devido ao acúmulo de defeitos nos quais as transportadoras de carga estão espalhadas. O efeito desse fator nos circuitos digitais submicrônicos no silício é pequeno, mas é mais importante para os transistores de potência, incluindo semicondutores complexos (nitreto de gálio e carboneto de silício).

- Aumento de 1 / f no ruído causado por transistores de borda espúrios. É importante para circuitos analógicos e de radiofrequência. O valor desse efeito aumenta com a diminuição dos padrões de design, quando o efeito dos demais efeitos da dose diminui.

Nos esquemas bipolares, o principal efeito da dose é uma queda no ganho causado por um aumento na corrente de base devido ao vazamento do emissor para a base na interface do silício e do óxido passivante. Outro efeito específico da dose para os transistores bipolares é que eles podem (não necessariamente) responder não apenas ao nível da dose acumulada, mas também à taxa de sua coleta - quanto mais lenta a dose é acumulada, pior a resistência. Esse efeito é chamado ELDRS (Sensibilidade aprimorada da taxa de dose baixa) e complica e aumenta muito o custo dos testes, geralmente não apenas nos circuitos bipolares, mas também nos circuitos CMOS - porque eles às vezes também têm transistores bipolares e porque é mais fácil fazer com que todos testem uniformemente do que descobrir onde o ELDRS pode estar e onde não.

Taxa de doseOutra parte dos efeitos relacionados à taxa de dose é um conjunto de doses ultra-rápido, no qual são gerados tantos pares de elétrons-orifícios no microcircuito que eles não têm tempo para recombinar, e uma enorme carga elétrica é introduzida no chip, que se dissolve através do solo e das linhas de energia durante tempo significativo - durante o qual o circuito para de funcionar. Esse tempo é chamado de “perda de tempo de trabalho” e é a principal característica da resistência de um microcircuito ou dispositivo a esses efeitos. Além disso, uma grande quantidade de carga introduzida no microcircuito altera seriamente os potenciais das áreas conectadas ao solo e à fonte de alimentação - o que pode levar ao aparecimento de um efeito de tiristor.

São os efeitos de uma alta taxa de dose - em prol da resistência à qual a tecnologia "silício na safira" e "silício no isolador" foi originalmente desenvolvida, porque a única maneira de reduzir a carga introduzida no circuito é separar a região ativa do microcircuito do volume do substrato, não dando a carga do substrato para participar do processo. Por que esses efeitos são importantes? Uma alta taxa de dose em pouco tempo é uma consequência típica de uma explosão nuclear.

Efeitos únicosOs efeitos únicos estão associados não a uma exposição prolongada à radiação, mas a um efeito mensurável de uma única partícula ionizante. Eles podem ser divididos em dois grandes grupos:

- Não destrutivo. Isso inclui falhas em vários tipos de elementos de armazenamento (memória cache, arquivos de registro, memória de configuração FPGA, etc.), transitórios na lógica combinacional e em circuitos analógicos. A principal característica desse tipo de efeito - eles não levam à destruição física do chip e podem ser software ou hardware fixo. Além disso, os transitórios são corrigidos por eles mesmos após algum tempo (a questão é qual o tamanho). Falhas nas matrizes de memória são de interesse prático principal, simplesmente porque elas representam a maior parte de todas as falhas devido à grande quantidade de memória nos modernos sistemas microeletrônicos.

- Destrutivo. Estes incluem o efeito tiristor e vários, mas, felizmente, efeitos raros, como perfurar o portão ou a queima de avalanches do transistor. Sua característica distintiva é que eles destroem irreversivelmente o elemento do chip. No caso do efeito tiristor, o chip pode geralmente (mas nem sempre!) Ser salvo se a energia for reiniciada rapidamente. Os efeitos destrutivos representam um sério risco para alguns tipos de memória flash e para dispositivos com altas tensões e densidades de corrente, sendo os mais importantes os interruptores de energia.

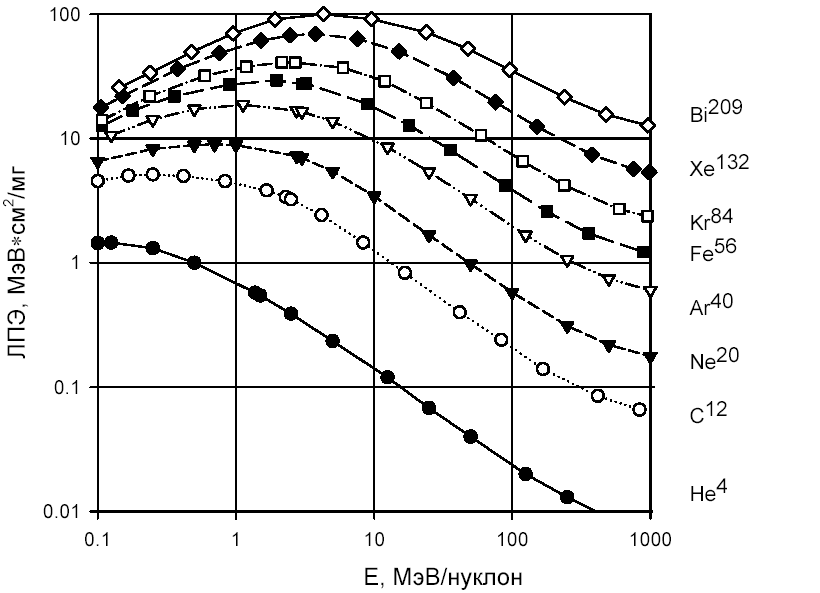

O rendimento energético específico de uma partícula ionizante é chamado de "transferência linear de energia" (LET) e é medido em MeV, transferido por unidade de comprimento da extensão de uma partícula em um material, por unidade de densidade de um material, ou seja, em (MeV * cm ^ 3) / (mg * cm) ou (MeV * cm ^ 2) / mg. LET não linear e não monotonicamente depende da energia das partículas e está interconectado com o caminho livre médio, que para partículas e materiais relevantes em microeletrônica pode variar de centenas de nanômetros a centenas de milímetros.

O número de partículas encontradas no espaço diminui com o crescimento de LET (veja a Figura 4). Os valores importantes são 30 (corresponde a íons de ferro) e 60 ou 80 (após o qual a probabilidade do evento é considerada insignificante). Além disso, uma figura importante é 15 MeV * cm ^ 2 / (mg) - esse é o LET máximo que os produtos de uma reação nuclear podem ter quando um próton ou nêutron entra no silício. Os prótons são um dos principais tipos de radiação solar e, embora sua LET seja pequena (décimos de unidade), eles têm um efeito significativo devido a reações nucleares e ionização secundária. A ionização secundária pode ocorrer diretamente na região ativa, ou pode ser devido ao próton que entra no átomo de algum material com um grande número atômico - por exemplo, tungstênio ou tântalo. Elementos pesados são usados ativamente na moderna tecnologia microeletrônica, por exemplo, para criar contatos do silício até a primeira camada de metalização. A ionização secundária também é a razão pela qual não é necessário embalar chips em caixas de chumbo para aumentar a resistência à radiação.

Figura 3. A dependência do LET da energia para diferentes tipos de partículas.

Figura 3. A dependência do LET da energia para diferentes tipos de partículas.Separadamente, vale a pena prestar atenção aos núcleos de hélio (partículas alfa) - não apenas porque existem muitos na composição da radiação solar, mas também porque muitas fontes de radiação alfa podem ser encontradas na vida cotidiana.

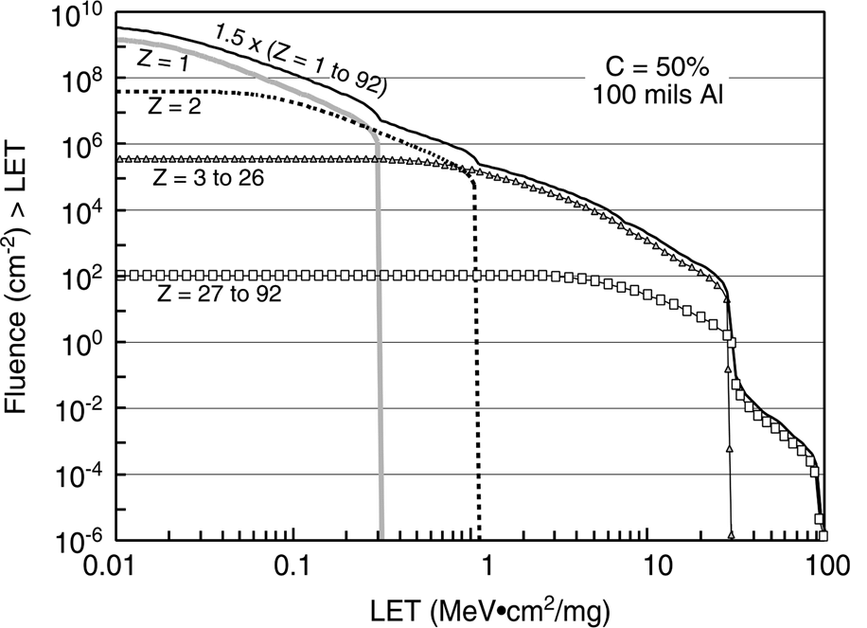

Figura 4. Comparação do número de partículas de diferentes tipos ao longo de uma missão de dois anos em órbita, de acordo com Xapsos et al., “Modelo para espectros cumulativos de energia solar pesada de íons e transferência linear de energia”, IEEE TNS, vol. 5, No. 6., 2007

Figura 4. Comparação do número de partículas de diferentes tipos ao longo de uma missão de dois anos em órbita, de acordo com Xapsos et al., “Modelo para espectros cumulativos de energia solar pesada de íons e transferência linear de energia”, IEEE TNS, vol. 5, No. 6., 20071, 30 ou 60 MeV * cm ^ 2 / (mg) - quanto é isso? O limiar de falha de uma célula de memória padrão na tecnologia de 7 nm é muito menor que a unidade, em 180 nm - na faixa de unidade a dezenas. O uso de circuitos especiais permite aumentar o limite, por exemplo, para centenas, mas geralmente é mais razoável atingir um número de 15 ou 30 unidades e filtrar os restos de eventos raros usando codificação resistente a ruído. 60 unidades é uma figura que geralmente aparece nos requisitos de resistência a efeitos destrutivos.

Efeitos de deslocamentoOs efeitos de deslocamento são a destruição local da rede cristalina, ou seja, a "batida" de um átomo a partir do local pretendido. A energia necessária para danificar a estrutura cristalina é geralmente bastante grande; portanto, a maioria das partículas que passam não causa esse efeito. Mas sua causa pode ser uma reação nuclear como resultado do impacto de um próton ou nêutron, que são muitos em órbita. Tais defeitos da rede local levam a uma diminuição da mobilidade dos portadores de carga, ao aumento do ruído e a alguns outros efeitos. Eles afetam os chips CMOS convencionais menos que os efeitos de dose "comuns", mas dominam as células solares, os fotodetectores, os transistores de potência e os semicondutores complexos que não possuem óxido, por exemplo, arseneto de gálio e nitreto de gálio. Isso explica sua alta resistência à dose - eles simplesmente não têm efeitos que causam rápida degradação dos chips de silício, e o que existe é mais fraco e mais tarde. A quantidade de radiação que causa efeitos de polarização é medida em partículas (geralmente prótons ou nêutrons) por centímetro quadrado de área do chip.

Então, com uma descrição dos fatores influentes da radiação, agora vamos ver onde e em que combinações eles ameaçam os microcircuitos.

O que? Onde Quando?

A Figura 2 mostra um exemplo de cálculo da dose completa definida em diferentes órbitas. Em seguida, precisamos discutir muitas suposições - atividade solar, forma, material e espessura da proteção e assim por diante, mas, em geral, apesar do fato de a imagem ser um cavalo esférico típico no vácuo, a tendência é clara: em órbitas diferentes, a velocidade da dose total pode variar de cinco ordens de magnitude.

Ao mesmo tempo, em órbitas baixas, sob o primeiro cinturão de Van Allen, a dose é acumulada tão lentamente que muitos microcircuitos comerciais comuns podem suportar vários anos nessas condições. Sim, que microchips, pessoas ainda mais frágeis voam para lá por anos sem sérias conseqüências para a saúde. Enquanto isso, órbitas baixas são quase todo o programa espacial tripulado, sensoriamento remoto da Terra, comunicações via satélite, Internet via satélite prometida muito em breve e, como dizem os americanos, o último, mas não menos importante, quase todos os cubsats são lançados em órbitas baixas.Microplaquetas comerciais da órbita baixaNa verdade, é justamente por causa da popularidade e importância das órbitas baixas que cresce a especulação sobre o fato de que microcircuitos caros e resistentes a radiações crescem, e é possível dispensar os comuns. Mas o uso no espaço de microcircuitos comerciais também tem armadilhas, que aparecem mesmo em órbitas baixas.Primeiro, os cintos de van Allen protegem a Terra e seus arredores imediatos apenas das partículas de luz, principalmente dos elétrons e prótons solares. Partículas mais pesadas, embora sejam muito menos comuns, voam calmamente até nosso último escudo - a atmosfera - e, corretamente, causam efeitos únicos, incluindo o efeito tiristor, que pode a qualquer momento destruir irreversivelmente qualquer chip e com ele toda a espaçonave . Portanto, os microcircuitos comerciais só podem ser utilizados se forem tomadas medidas para protegê-los de efeitos únicos.O segundo problema é que os chips no satélite não são apenas processadores e memória, mas também muitos outros tipos de chips, incluindo os de potência e analógicos, e com sua resistência à radiação tudo é muito mais complicado e menos previsível. E os sistemas modernos em um chip contêm um grande número de blocos não digitais; por exemplo, para a maioria dos chips de memória flash, o gerador de alta tensão usado para a gravação é o primeiro a parar de funcionar, e para os circuitos CMOS analógicos, a tensão de referência gerada por um par de transistores bipolares é alterada e até pequenos vazamentos podem alterar seriamente o ponto de operação de cascatas analógicas de baixa potência. A resistência das teclas de força aos efeitos únicos destrutivos pode depender muito da tensão aplicada a elas, e assim por diante.O terceiro problema importante do uso de microcircuitos comerciais no espaço é que a resistência à dose total e ao efeito do tiristor é sensível a alterações nos parâmetros do processo, incluindo os pequenos; portanto, se algo for alterado na fábrica, você poderá jogar os resultados de seus testes no lixo. . E para microcircuitos comerciais, o fabricante garante a estabilidade dos parâmetros funcionais, não o processo tecnológico. Além disso, em lotes diferentes, você pode encontrar cristais de diferentes fábricas; por exemplo, o processador do sexto iPhone, Apple A9, foi fabricado no TSMC de 16 nm e no Samsung de 14 nm, e o usuário não foi informado sobre qual versão está em seu telefone. Institutos confiáveis de fundição ou processos técnicos certificados são usados para combater esse problema em todo o mundo para o desenvolvimento de microcircuitos resistentes à chuva - em resumo,alguma forma de garantia da invariabilidade do processo de fabricação pela fábrica.No total, a resposta correta para a pergunta "é possível usar microcircuitos comerciais convencionais no espaço?" soa assim: "Sim, é possível, em algumas órbitas e sujeito a vários requisitos e condições". Conselho útil: se você ainda decidir usar um chip comercial e investir em seus testes, compre uma ação imediatamente dez anos antes. Aliás, esse é um modelo de negócios para uma grande e respeitada empresa 3DPlus - eles testam todos os microchips comerciais seguidos de alegria, encontram aqueles que têm desempenho suficiente (essencialmente aleatório), compram grandes quantidades e depois embalam os chips em seus próprios gabinetes com sua própria marca. .Outras órbitasNo entanto, os satélites voam não apenas em baixa órbita terrestre. Como exemplo de outros requisitos, vejamos a única maneira de garantir uma comunicação estável nas proximidades do Polo Norte - e esta é uma área estrategicamente importante para a Rússia - a órbita de Molniya, nomeada após a primeira sonda lançada nela. Figura 5. Órbita “relâmpago”.A principal característica dessa órbita é que, devido ao seu grande alongamento (a altura mínima é de cerca de 500 km acima da superfície da Terra, a máxima é de até 40.000 km, o período é de 12 horas), o aparelho cruza os cinturões de radiação quatro vezes por dia. A vida ativa dos primeiros satélites de Molniya durou apenas cerca de seis meses, principalmente por causa da queda induzida pela radiação na potência dos painéis solares, necessária para alimentar um poderoso transmissor de rádio (alta órbita).Em órbitas geoestacionárias de auxílios à navegação, a Figura 2 promete uma dose de várias centenas de crad (Si) - e a resistência à dose de microcircuitos comerciais pode facilmente ser de 5 a 10 crad (Si), ou seja, cerca de 10 a 15 anos de existência ativa desses chips não pode haver discurso em órbita. Mais precisamente, pode, mas para isso você precisará de uma proteção muito mais espessa - ou de algo mais denso que o alumínio. No entanto, aqui mergulhamos no maravilhoso mundo do design de naves espaciais, então vamos nos limitar à frase de que entregar cada quilograma em órbita é caro, e a ideia de esconder os eletrônicos mais vulneráveis mais fundo dentro do gabinete, protegê-lo com outros componentes não é ruim, mas completamente problemática não vai decidir.Fichas militaresAo lidar com a questão de desmascarar mitos sobre a resistência à alegria, é imperativo dizer que você não pode equiparar microcircuitos “resistentes à alegria”, “espaço” e “militares”. Nem todos os microcircuitos militares são resistentes a rádio e nem todos os microcircuitos resistentes a rádio são militares. Se nos voltarmos para o padrão militar americano Mil-Std-883 (para o americano, porque sua contraparte russa é classificada em termos de radiação), encontraremos muitos testes diferentes para a influência do meio ambiente - ciclagem térmica, umidade, ar com sal marinho etc. .d.

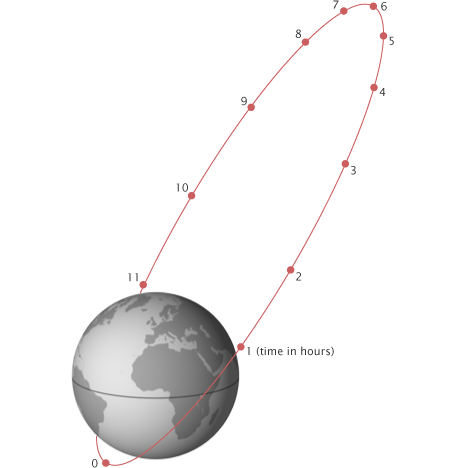

Figura 5. Órbita “relâmpago”.A principal característica dessa órbita é que, devido ao seu grande alongamento (a altura mínima é de cerca de 500 km acima da superfície da Terra, a máxima é de até 40.000 km, o período é de 12 horas), o aparelho cruza os cinturões de radiação quatro vezes por dia. A vida ativa dos primeiros satélites de Molniya durou apenas cerca de seis meses, principalmente por causa da queda induzida pela radiação na potência dos painéis solares, necessária para alimentar um poderoso transmissor de rádio (alta órbita).Em órbitas geoestacionárias de auxílios à navegação, a Figura 2 promete uma dose de várias centenas de crad (Si) - e a resistência à dose de microcircuitos comerciais pode facilmente ser de 5 a 10 crad (Si), ou seja, cerca de 10 a 15 anos de existência ativa desses chips não pode haver discurso em órbita. Mais precisamente, pode, mas para isso você precisará de uma proteção muito mais espessa - ou de algo mais denso que o alumínio. No entanto, aqui mergulhamos no maravilhoso mundo do design de naves espaciais, então vamos nos limitar à frase de que entregar cada quilograma em órbita é caro, e a ideia de esconder os eletrônicos mais vulneráveis mais fundo dentro do gabinete, protegê-lo com outros componentes não é ruim, mas completamente problemática não vai decidir.Fichas militaresAo lidar com a questão de desmascarar mitos sobre a resistência à alegria, é imperativo dizer que você não pode equiparar microcircuitos “resistentes à alegria”, “espaço” e “militares”. Nem todos os microcircuitos militares são resistentes a rádio e nem todos os microcircuitos resistentes a rádio são militares. Se nos voltarmos para o padrão militar americano Mil-Std-883 (para o americano, porque sua contraparte russa é classificada em termos de radiação), encontraremos muitos testes diferentes para a influência do meio ambiente - ciclagem térmica, umidade, ar com sal marinho etc. .d. etc.

Radiação relacionar seguintes itens:1017,2 neutrões irradiação

1019,8 radiação ionizante (dose total) Procedimento de teste

induzida procedimento de teste latchup 1020,1 taxa de dose

1021,3 taxa de dose de teste virada de microcircuitos digitais

1023,3 Dose taxa de resposta de microcircuitos linearesde dose completa e da taxa de dose. Efeitos únicos? De jeito nenhum. As especificações técnicas para o microcircuito podem incluir requisitos de resistência a falhas únicas e / ou efeito de tiristor, mas esses requisitos não são padronizados e são determinados novamente a cada vez, com base nas necessidades de clientes específicos de cada chip. Acontece que o status de "militar" não é uma garantia da capacidade de lançar o chip no espaço? É sim.

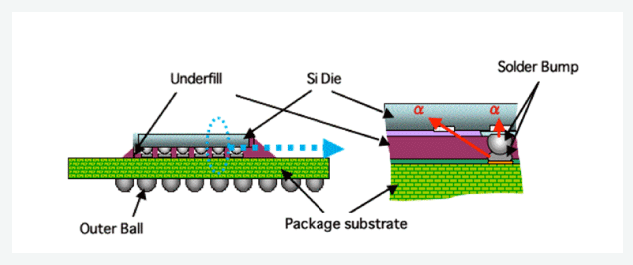

Um exemplo é o destino do infame “solo Phobos”, cuja morte foi causada, de acordo com a versão oficial (muito difícil de provar, mas muito conveniente), pelo impacto de uma partícula carregada pesada no chip de memória da classe militar americana, que não era resistente a falhas únicas .Átomo da paz e outrosA importância da resistência à radiação não se limita às aplicações espaciais e militares. A radiação natural de fundo no nível do mar é muitas vezes menor do que o que acontece em órbita baixa, mas a atmosfera da Terra não serve apenas como o último escudo no caminho da radiação cósmica, mas também gera partículas secundárias ao interagir com ela. Partículas secundárias são principalmente nêutrons. Aparecendo nas camadas superiores da atmosfera, eles geralmente não atingem a superfície; no entanto, nas altitudes dos aviões civis, a dose de radiação também é significativa e estatísticas impressionantes são coletadas para falhas únicas. Os raios X são usados na medicina há muito tempo, e a radioterapia é uma das maneiras importantes de combater tumores malignos, e esses dispositivos também precisam de eletrônicos.E, é claro, não esqueça que todo o barulho com a solda sem chumbo amada por todos os engenheiros eletrônicos foi iniciada em grande parte devido ao fato de que o chumbo e alguns outros materiais usados na fabricação de microcircuitos contêm impurezas de elementos mais pesados, em particular o urânio, e sua aplicação leva à geração de um fluxo de partículas alfa pequeno, mas ainda bem mensurável - bem próximo ao silício vulnerável. No caso de gabinetes BGA ou montagens 3D - em toda a superfície do silício vulnerável. Figura 6. Ilustração de uma bola de solda como fonte de partículas alfa.A boa notícia é que as partículas alfa têm um caminho livre médio bastante pequeno no silício (de unidades a dezenas de mícrons, dependendo da energia), e a metalização multicamada ajuda a reduzir seu efeito. A má notícia é que, com baixos padrões de design, todas as partículas alfa que ainda atingem o silício causam falhas, não apenas únicas, mas também múltiplas (mais sobre isso abaixo). Por exemplo, no ano passado, a TSMC publicou um artigo no Simpósio Internacional de Física de Confiabilidade IEEE 2018 sobre a medição do número de falhas da poluição por partículas alfa na memória, de acordo com os padrões de projeto de 7 nm, ou seja, esse problema continua a existir e requer alguma ação em um mundo onde tudo mudou para solda sem chumbo.Outra aplicação de circuitos resistentes à radiação, sobre a qual gostaria de dizer algumas palavras, é a física de alta energia e a energia atômica. Nas zonas ativas de coletores de hádrons e reatores nucleares (bem como em equipamentos projetados para eliminar desastres de radiação), também são necessários eletrônicos, e é altamente desejável que um que não precise ser substituído e reparado por um tempo considerável. Os requisitos para a dose total absorvida para tais aplicações são dezenas e até centenas de Megarads (Si), ou seja, três ordens de magnitude a mais do que em aplicações espaciais convencionais. Para complicar a situação, essa resistência é necessária não nos circuitos digitais, mas nos circuitos de potência e analógicos - circuitos de controle de acionamento elétrico e processamento primário das leituras dos sensores multicanais.E, embora a garantia da resistência à dose dos circuitos digitais seja cada vez mais clara, mesmo em altas doses, no caso de um analógico, o desenvolvimento de um circuito elétrico é de fundamental importância, e o próprio circuito resultante é ainda mais know-how do que geralmente ocorre em um design analógico.

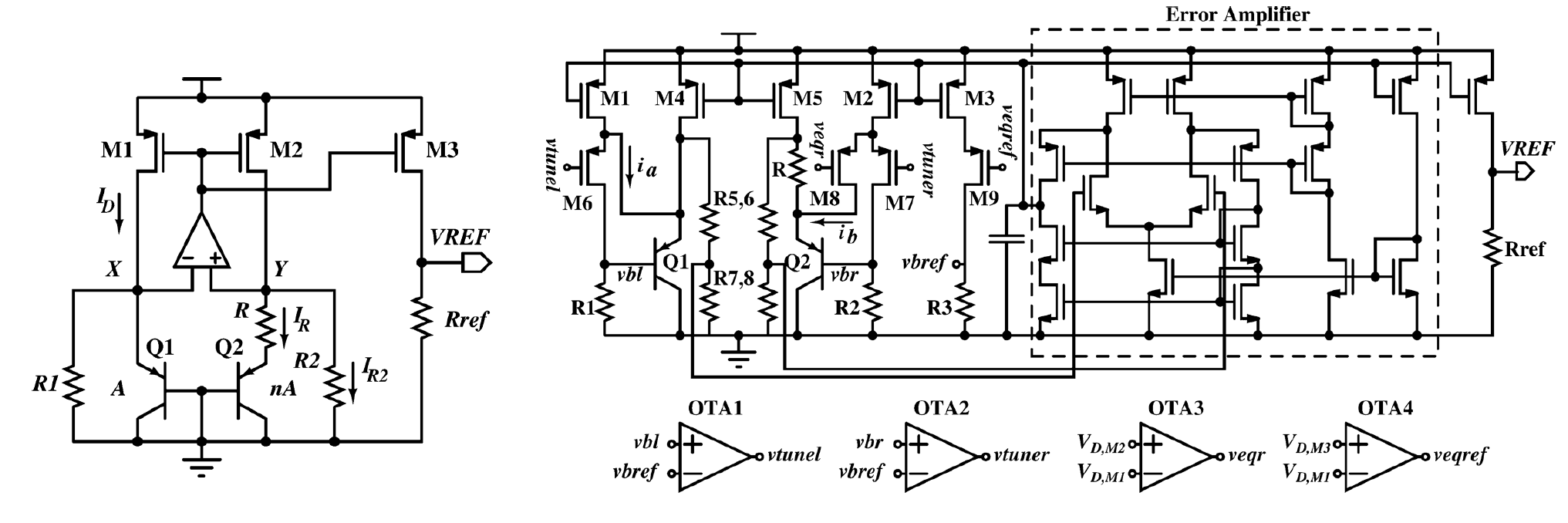

Figura 6. Ilustração de uma bola de solda como fonte de partículas alfa.A boa notícia é que as partículas alfa têm um caminho livre médio bastante pequeno no silício (de unidades a dezenas de mícrons, dependendo da energia), e a metalização multicamada ajuda a reduzir seu efeito. A má notícia é que, com baixos padrões de design, todas as partículas alfa que ainda atingem o silício causam falhas, não apenas únicas, mas também múltiplas (mais sobre isso abaixo). Por exemplo, no ano passado, a TSMC publicou um artigo no Simpósio Internacional de Física de Confiabilidade IEEE 2018 sobre a medição do número de falhas da poluição por partículas alfa na memória, de acordo com os padrões de projeto de 7 nm, ou seja, esse problema continua a existir e requer alguma ação em um mundo onde tudo mudou para solda sem chumbo.Outra aplicação de circuitos resistentes à radiação, sobre a qual gostaria de dizer algumas palavras, é a física de alta energia e a energia atômica. Nas zonas ativas de coletores de hádrons e reatores nucleares (bem como em equipamentos projetados para eliminar desastres de radiação), também são necessários eletrônicos, e é altamente desejável que um que não precise ser substituído e reparado por um tempo considerável. Os requisitos para a dose total absorvida para tais aplicações são dezenas e até centenas de Megarads (Si), ou seja, três ordens de magnitude a mais do que em aplicações espaciais convencionais. Para complicar a situação, essa resistência é necessária não nos circuitos digitais, mas nos circuitos de potência e analógicos - circuitos de controle de acionamento elétrico e processamento primário das leituras dos sensores multicanais.E, embora a garantia da resistência à dose dos circuitos digitais seja cada vez mais clara, mesmo em altas doses, no caso de um analógico, o desenvolvimento de um circuito elétrico é de fundamental importância, e o próprio circuito resultante é ainda mais know-how do que geralmente ocorre em um design analógico. 7. . Y. Cao et.al., «A 4.5 MGy TID-Tolerant CMOS Bandgap Reference Circuit Using a Dynamic Base Leakage Compensation Technique», IEEE TNS, Vol.60, N.4, 2013Ilustrarei a escala dos desafios enfrentados pelos desenvolvedores de chips para energia nuclear com meu exemplo favorito. Uma fonte de tensão de referência (ION) igual ao intervalo de banda de uma referência de tensão de intervalo de banda de silício é um circuito relativamente simples e bem conhecido. Sob a influência da radiação, os parâmetros dos transistores bipolares usados como diodos mudam (o ganho diminui devido ao aparecimento de um vazamento na base do emissor). Como resultado, a tensão de referência de um circuito ION convencional, que determina a precisão de todas as medições, pode mudar, digamos, de 15 a 20%, o que corresponde a uma resolução ADC efetiva de dois a três bits. No circuito à direita, a tensão de referência varia dentro de 1% (que é superior a 7 bits) na dose de radiação ionizante de 4,5 MGy. Para alcançar esse resultado impressionante, o esquema teve que ser seriamente reformulado,adicionando um monte de feedbacks para compensar o vazamento da dose. Na versão à prova de chuva, existem aproximadamente quatro vezes mais elementos do que na versão normal e seu consumo de energia é o dobro. E a pior notícia é que, para cada novo esquema, a estratégia de resistência à radiação e sua implementação devem ser desenvolvidas separadamente. Mas ainda existe o problema de proteger os circuitos analógicos contra efeitos únicos, cuja solução também é pouco formalizada.Mas ainda existe o problema de proteger os circuitos analógicos contra efeitos únicos, cuja solução também é pouco formalizada.Mas ainda existe o problema de proteger os circuitos analógicos contra efeitos únicos, cuja solução também é pouco formalizada.

7. . Y. Cao et.al., «A 4.5 MGy TID-Tolerant CMOS Bandgap Reference Circuit Using a Dynamic Base Leakage Compensation Technique», IEEE TNS, Vol.60, N.4, 2013Ilustrarei a escala dos desafios enfrentados pelos desenvolvedores de chips para energia nuclear com meu exemplo favorito. Uma fonte de tensão de referência (ION) igual ao intervalo de banda de uma referência de tensão de intervalo de banda de silício é um circuito relativamente simples e bem conhecido. Sob a influência da radiação, os parâmetros dos transistores bipolares usados como diodos mudam (o ganho diminui devido ao aparecimento de um vazamento na base do emissor). Como resultado, a tensão de referência de um circuito ION convencional, que determina a precisão de todas as medições, pode mudar, digamos, de 15 a 20%, o que corresponde a uma resolução ADC efetiva de dois a três bits. No circuito à direita, a tensão de referência varia dentro de 1% (que é superior a 7 bits) na dose de radiação ionizante de 4,5 MGy. Para alcançar esse resultado impressionante, o esquema teve que ser seriamente reformulado,adicionando um monte de feedbacks para compensar o vazamento da dose. Na versão à prova de chuva, existem aproximadamente quatro vezes mais elementos do que na versão normal e seu consumo de energia é o dobro. E a pior notícia é que, para cada novo esquema, a estratégia de resistência à radiação e sua implementação devem ser desenvolvidas separadamente. Mas ainda existe o problema de proteger os circuitos analógicos contra efeitos únicos, cuja solução também é pouco formalizada.Mas ainda existe o problema de proteger os circuitos analógicos contra efeitos únicos, cuja solução também é pouco formalizada.Mas ainda existe o problema de proteger os circuitos analógicos contra efeitos únicos, cuja solução também é pouco formalizada.Resistência à radiação e padrões de projeto

No site de uma fábrica de microeletrônica por um longo tempo, houve uma declaração de que a resistência à radiação não pode ser alcançada em padrões de projeto abaixo de 600 nm, porque, caso contrário, "partículas carregadas perfuram o silício". Por uma coincidência surpreendente, os padrões mínimos de design disponíveis para essa fábrica eram de apenas 600 nm. E um funcionário sênior de outra fábrica relatou em uma entrevista que fabricar microchips para o espaço em padrões de projeto abaixo de 90 nm era "tecnologicamente impossível". E, novamente, coincidiu tanto que é tecnologicamente impossível fazer algo a taxas abaixo de 90 nm nesta fábrica em particular. As razões de marketing para essas situações e os benefícios imediatos delas são compreensíveis, mas, a longo prazo, essas frases, dirigidas a um grande público, me parecem causar mais mal do que bem.

Além disso, há discussões regulares que não estão vinculadas a nenhum marketing de que os microchips fabricados de acordo com os padrões de design sejam mais grosseiros que um determinado limite, sejam imunes a falhas únicas destrutivas (em particular ao efeito do tiristor), o que significa que muitos anos de uso de tecnologias antigas não são apenas justificáveis, mas e necessário.

Ou vice-versa, frases que afirmam que os microcircuitos com padrões de projeto abaixo de 250 nm são imunes ao efeito do tiristor, porque possuem tensões operacionais tão baixas que o tiristor simplesmente não pode abrir. Ou há opiniões de que, de fato, o problema não está nos padrões de projeto, mas no fato de que a tecnologia CMOS é fundamentalmente vulnerável à radiação (o que é confirmado por testes realizados pelo candidato nos anos setenta), e os antigos chips resistentes a radiantes são bipolares / KNS / GaAs. E como a tecnologia CMOS é fundamentalmente ruim, mas todos os chips modernos são fabricados - isso significa que os chips modernos não são estáveis por definição, e a única maneira certa para a astronáutica é investir dinheiro para lembrar o arseneto de gálio há muito abandonado (ao mesmo tempo no mercado comercial da Intel ganhar) ou retornar à lógica discreta testada pelo tempo. E ainda melhor - para as lâmpadas.

Radiante - quer dizer velho e atrasado?Para ser justo, deve-se notar que, em circuitos executados em padrões de projeto de cerca de dois mícrons ou mais, geralmente não há efeito de tiristor e falhas únicas. “Normalmente”, no entanto, não significa “sempre” de forma alguma, existem exemplos de circuitos antigos com baixa resistência ao efeito do tiristor, e os padrões de projeto não garantem nada. Uma alta resistência a falhas únicas surge simplesmente porque a troca de elementos em tais padrões de projeto requer muita energia. Também durante a operação normal, gostaria de desejar que aqueles que continuam usando chips antigos tentem montar o processador Intel Core na lógica da série 74 e pensar em que tipo de foguete será capaz de levantar o monstro resultante no ar.

Por outro lado, a microeletrônica não está viva por processadores únicos. Há um grande número de tarefas para as quais padrões de design muito pequenos não são necessários ou não são tão obrigatórios, e níveis de 500-90 nm são suficientes. O mercado comercial global de microcircuitos em bolachas com um diâmetro de 200 mm (e estes são padrões de projeto de 90 nm ou mais) vem crescendo há vários anos, até a escassez de equipamentos de produção. Os microcircuitos “desenvolvidos há muito tempo” e os completamente novos são produzidos com padrões de projeto “desatualizados” e muitas fábricas estão prontas para garantir o futuro a longo prazo dos processos tecnológicos (mas não necessariamente sua invariância completa). Portanto, o "atraso" de uma determinada fábrica em relação ao TSMC condicional não significa, de maneira alguma, a impossibilidade de sucesso comercial no campo civil ou no campo resistente especial.

O alto custo de desenvolvimento, fabricação e certificação de circuitos resistentes a radiantes é uma dor de cabeça ainda maior para os fabricantes do que na eletrônica automotiva ou industrial. Pequenas circulações (e muitas vezes, senão centenas, e milhares) frequentemente complicam a comercialização desse tipo de desenvolvimento, porque se você precisar dividir um milhão de dólares em mil chips (o custo de desenvolvimento é relativamente simples para os padrões de 180 nm), isso significa mil dólares por um chip, mas a certificação ainda é necessária, o que pode facilmente resultar em vários milhões (especialmente se você testar circuitos CMOS no ELDRS). E se você precisar pagar um bilhão de dólares em uma pequena corrida? Isso é quanto custa o desenvolvimento em 5-7 nm. O alto custo de desenvolvimento e certificação levou ao fato de que em todo o mundo o desenvolvimento de uma parte significativa de microcircuitos resistentes à chuva é subsidiado direta ou indiretamente pelos estados. Isso reduz bastante o número de novos projetos, incentiva mais e mais inventividade a vender o que é e maximiza o uso de blocos IP comprovados. Como resultado, os populares microcircuitos resistentes à chuva são produzidos e usados por muitos anos, criando a ilusão de que todos os microcircuitos resistentes à chuva são antigos. E, na maioria dos casos, os clientes estão satisfeitos com isso, porque em uma situação em que a confiabilidade ainda é primária em relação ao desempenho, reutilizar uma solução já comprovada é geralmente o melhor que você pode pensar e ter uma "herança de voo" é uma enorme vantagem competitiva. Isso também ajuda a prolongar o período de produção ativa de desenvolvimentos bem-sucedidos - mesmo quando eles já estão obsoletos e quando já há um substituto. Além disso, mesmo a instalação de um análogo compatível de pino a pino exige, na maioria dos casos, pelo menos uma reconciliação da documentação do projeto, além de um máximo de testes dispendiosos. E isso ocorre em uma situação em que nenhum desenvolvimento é necessário. E o caso em que você realmente precisa refazer algo para usar o novo chip? Obviamente, nessa situação, os desenvolvedores de hardware tendem a reutilizar as soluções comprovadas como um todo.

Isso não ajuda a percepção do público de que o caminho para novos desenvolvimentos no espaço é longo e espinhoso - e ainda mais longo nas notícias, e é das notícias populares da ciência que as pessoas comuns geralmente aprendem sobre as conquistas da indústria espacial. Em 2015, havia várias mensagens no formato “o satélite New Horizons, que chegou a Plutão, tem o mesmo processador que no Sony PlayStation”, e esse prefixo já tinha vinte anos na época do comunicado de imprensa. Excelente e muito competente apresentação do material, você não dirá nada. O New Horizons foi lançado em 2006 e o desenvolvimento do projeto começou em 2000 - no ano do primeiro voo do processador Mongoose-V, ou seja, era o mais novo processador disponível com experiência em órbita. O desenvolvimento deste processador terminou em 1998 e começou em 1994 - exatamente ao mesmo tempo que o lançamento do PlayStation. Aqui está outro exemplo: os processadores de arquitetura Power750 foram lançados para aplicativos civis em 1997 e, em 1998, o iMac estreou com esse processador. Em 2001, o desenvolvimento de um análogo resistente a radiações, o RAD750, foi concluído. Este processador chegou ao cosmos pela primeira vez em 2005 e somente em 2012 após o pouso suave do rover Curiosity em Marte. Obviamente, também havia algumas manchetes amarelas sobre o processador quinze anos atrás, mas o desenvolvimento do projeto Curiosity começou em 2003, isto é, mesmo antes do primeiro vôo do processador RAD750.

VanguardaApesar de tudo isso, no momento, o nível de padrões de design nos quais o desenvolvimento de plataformas de computação para o espaço está em andamento é de 65 a 45 a 22 nm. O chipset RAD5500 americano já foi colocado em produção em série a 45 nm, o processador europeu DAHLIA será lançado em 28 nm no próximo ano, e a plataforma de desenvolvimento ASIC projetada para uso a longo prazo está sendo ativamente criada a 65 nm no IMEC belga. Os desenvolvedores russos também não estão muito atrás - o roadmap NIISI RAS do próximo ano mostra a saída de um processador resistente a radiações de 65 nm, e as publicações sobre esse tópico falam em criar uma plataforma de desenvolvimento, ou seja, esses padrões de design têm um grande futuro não apenas na Europa, mas também na Rússia .

E mesmo nesse nível de padrões de projeto, o desenvolvimento de eletrônicos resistentes à chuva não para - se você olhar para as últimas edições da IEEE Transactions on Nuclear Science, poderá encontrar trabalho suficiente no estudo de transistores com padrões de design de 20-16-14 nm, preparando o caminho para novas gerações de microprocessadores espaciais. Nesses padrões de projeto, os desenvolvedores esperam muitas coisas novas e interessantes: primeiro, transistores de anel não podem ser feitos; segundo, o FinFET possui uma geometria e isolamento de canal completamente diferente; terceiro, existem tecnologias FDSOI, que também têm especificidade suficiente.

Obviamente, uma diminuição nos padrões de projeto afeta a resistência à radiação dos microcircuitos fabricados neles, mas não necessariamente para pior. A tendência geral é que, com uma diminuição nos padrões de design, o efeito da dose total diminua e os efeitos únicos aumentem. A mudança de tensão limiar nos padrões de projeto de 180 nm ou menos é medida em unidades ou dezenas de milivolts, mesmo para grandes doses: o óxido de porta é tão fino que a carga acumulada nele se afunila no canal em vez de acumular. A camada de transição nas tecnologias com isolamento STI é compacta o suficiente, o que em muitos casos permite baixo vazamento em uma dose total de várias dezenas ou até centenas de berços (Si). E se aplicarmos transistores de anel e anéis de proteção na tecnologia volumétrica profundamente submicron, então nos livraremos imediatamente de todos os problemas de dose.

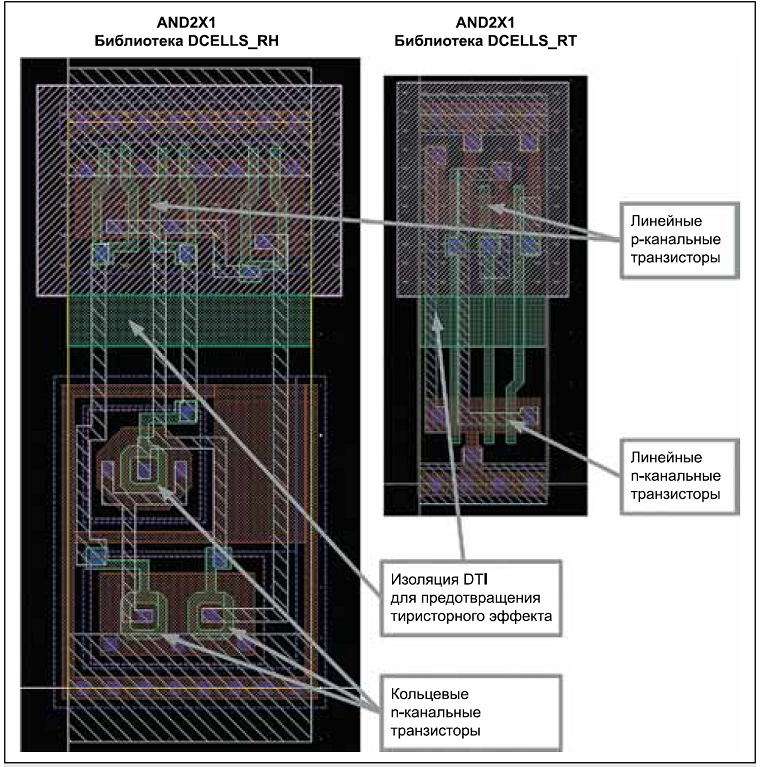

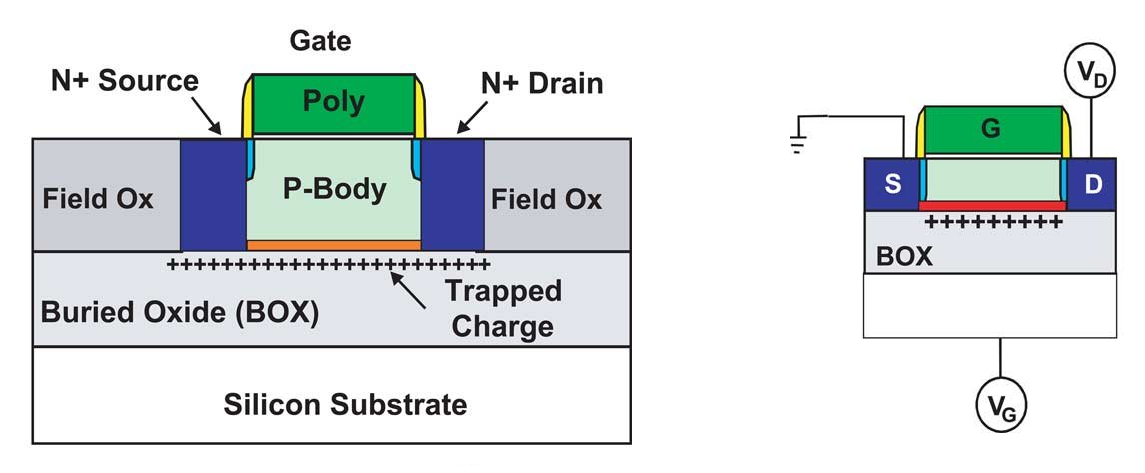

Figura 8. Exemplos de elementos resistentes à radiação E desenvolvidos por Milander usando a tecnologia SOI BCD.

Figura 8. Exemplos de elementos resistentes à radiação E desenvolvidos por Milander usando a tecnologia SOI BCD.A Figura 8 mostra duas opções para implementar o mesmo elemento lógico AND para diferentes condições. À esquerda, vemos os transistores de anéis de vedação completos em anéis de proteção individuais. À direita está a opção mais simples, para uma dose total baixa: transistores lineares, em vez de anéis de proteção, apenas bons contatos no solo. E em ambos os casos, o isolamento dielétrico dos transistores de canal n do canal p para proteger o chip do efeito do tiristor. Na tecnologia volumétrica, os anéis de proteção desempenham essa função. Deve-se notar que, para muitas aplicações espaciais, a resistência à dose total no nível de 50-100 crad (Si) é suficiente e os transistores lineares fazem isso muito bem, sem exigir deterioração significativa dos parâmetros funcionais do circuito, a fim de alcançar a estabilidade.

Com falhas únicas, a situação é a seguinte: o diâmetro aproximado da região em que a carga é coletada quando uma única partícula entra é da ordem de um mícron, ou seja, mais do que o tamanho de uma célula de memória feita de acordo com padrões de design profundamente submicrônicos. De fato, as chamadas falhas múltiplas são descobertas experimentalmente, quando uma partícula causa a troca de vários bits ao mesmo tempo. Além disso, com uma diminuição nos padrões de projeto, a energia necessária para trocar o bit de memória também diminui, ou seja, mais ocorrências resultam em falhas do que em chips feitos de acordo com padrões de projeto mais rigorosos. Incluindo a entrada de partículas alfa de impurezas radioativas em materiais estruturais.

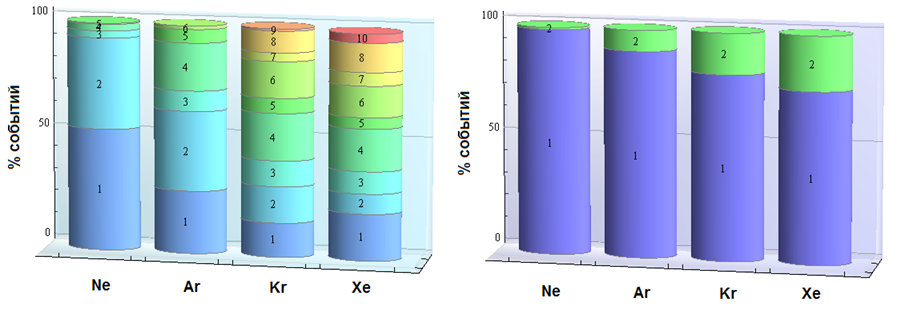

Figura 9. Comparação do número de falhas de uma única partícula atingida por duas variantes diferentes de SRT de 6T na tecnologia com padrões de projeto de 65 nm. Fonte - A. Balbekov et al., “Questões de aplicabilidade do VLSI para a tecnologia CMOS de 65 nm sob a influência de fatores do espaço sideral”.

Figura 9. Comparação do número de falhas de uma única partícula atingida por duas variantes diferentes de SRT de 6T na tecnologia com padrões de projeto de 65 nm. Fonte - A. Balbekov et al., “Questões de aplicabilidade do VLSI para a tecnologia CMOS de 65 nm sob a influência de fatores do espaço sideral”.A Figura 9 mostra os dados experimentais sobre falhas únicas na tecnologia volumétrica de 65 nm. À esquerda está o habitual 6T-SRAM. Dez falhas de um hit! O código Hamming não o protegerá disso. Portanto, se estamos falando de microcircuitos comerciais, em padrões de projeto aproximados, com falhas únicas, tudo será um pouco melhor do que nas finas. No mínimo, eles permanecerão solitários e podem realmente ser corrigidos por codificação. Mas se o chip foi criado especialmente para aplicações espaciais, o arsenal do desenvolvedor possui um grande número de soluções arquitetônicas, de circuito e topológicas que podem fornecer alta durabilidade ao mesmo tempo que alto desempenho. No lado direito da figura também está o 6T-SRAM, com exatamente o mesmo circuito elétrico, mas com uma topologia diferente. O preço das melhorias que removem várias falhas, o efeito do tiristor e aumentam a resistência à dose total é um aumento de quatro vezes na área. Não parece muito bom, mas ninguém disse que seria fácil. No entanto, o Radiation Hardening by Design funciona e permite que você atinja indicadores de resistência predeterminados em pequenos padrões de projeto em qualquer tecnologia volumétrica.

Por que pré-definido? Como a obtenção de diferentes níveis de resistência requer o uso de métodos diferentes para aumentá-la, e para cada tecnologia e tarefa técnica, o conjunto de métodos necessário é diferente. Então, por que não aplicar tudo de uma vez para que se sinta bem? Como a obtenção de resistência à radiação sempre ocorre devido à deterioração dos parâmetros funcionais (consumo de energia, área de cristal, velocidade, etc.), e eles são a primeira prioridade. É por isso que precisamos de requisitos claros para especificações técnicas, tanto em funcionalidade quanto em durabilidade. É verdade que os microcircuitos não costumam ser feitos para resolver um único problema, especialmente radicalmente estável, no qual a circulação para cada uma das aplicações disponíveis pode ser de várias dezenas de peças. No entanto, uma boa compreensão dos requisitos permite, por exemplo, não usar transistores em anel, aumentando muito a área e o consumo atual e, no final, obter produtos mais competitivos.

Os olhos do leitor atento provavelmente estão atraídos pela palavra "volumétrico" na frase "indicadores predefinidos de resistência em pequenos padrões de projeto para qualquer tecnologia volumétrica". Não é supérfluo lá? Todo mundo sabe que microcircuitos resistentes a radiantes precisam ser fabricados usando a tecnologia "silício em um isolador" ou "silício em safira".

Silício no isolador

A tecnologia "silício no isolador" tem sido firmemente enraizada na glória dos resistentes à radiação. As raízes desse equívoco popular datam da antiguidade, quando o precursor do SOI, silício sobre safira, foi usado ativamente para o desenvolvimento militar. Porque Os transistores nesta tecnologia são eletricamente separados um do outro e, mais importante, do substrato. Isso significa que a área de coleta de carga induzida por radiação após exposição a curto prazo do chip à radiação com uma alta taxa de dose será pequena. Isso, por sua vez, reduz significativamente o tempo de perda de capacidade de trabalho - o que você precisa para trabalhar em uma guerra atômica. E, de fato, não existe outro método para reduzir o tempo de perda de capacidade de trabalho, exceto o isolamento dielétrico total.

A segunda parte importante do mito “SOI = resistência à alegria” é a resistência ao efeito do tiristor, inclusive quando exposto a uma alta taxa de dose. O efeito tiristor ou "trava" é quase a principal dor de cabeça para desenvolvedores de microchips e dispositivos para o espaço, e não é de surpreender que a tecnologia que permite que você se livre dele ganhe fama por ser resistente à radiação. Mas, na realidade, a situação é novamente um pouco mais complicada.

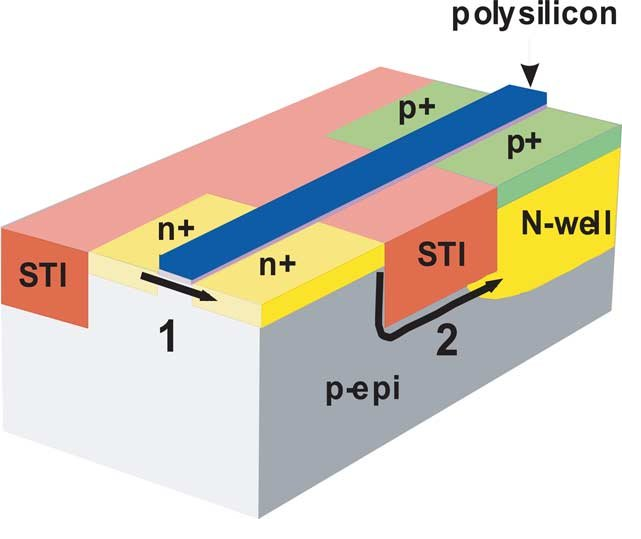

Figura 10. Seção transversal de uma tecnologia CMOS em massa com um tiristor parasita.

Figura 10. Seção transversal de uma tecnologia CMOS em massa com um tiristor parasita.A causa do efeito do tiristor é a estrutura parasitária do tiristor presente dentro dos elementos da tecnologia de volume CMOS. Se as resistências Rs e Rw forem grandes o suficiente, então essa estrutura do tiristor, quando uma partícula carregada entrar, poderá abrir e causar um curto-circuito no terra do chip com energia, o que, como você sabe, não é bom. Quão grandes são essas resistências em microchips reais? A resposta a esta pergunta é bastante simples: o contato com o substrato ou o bolso é uma área extra, portanto eles tentam minimizar seu número. E isso, por sua vez, significa que, por padrão, o efeito do tiristor no chip "comum" será mais provável do que não. É verdade que o efeito do tiristor pode ocorrer não apenas pela radiação, mas também quando exposto, por exemplo, a uma descarga eletrostática ou mesmo simplesmente a uma temperatura elevada e alta densidade de corrente com uma topologia malsucedida. Em aplicações "comuns", os fabricantes de energia e eletrônicos automotivos são confrontados com um efeito tiristor.

Em uma parte significativa dos sistemas espaciais, uma reinicialização é bastante aceitável em caso de circunstâncias imprevistas, ou seja, você pode tentar usar um chip propenso a "travamento", colocando um circuito de controle de energia na fonte de alimentação e redefinindo a energia se a norma for excedida. De fato, isso é feito regularmente em situações em que é muito necessário o uso de um microcircuito comercial de alto desempenho, e os chips de proteção contra o efeito tiristor (Limitador de Corrente Latchup) são um produto resistente a radiações bastante popular. Mas essa solução tem muitas limitações. Você pode reiniciar a energia nem em todos os lugares e nem sempre; uma reinicialização no processo de executar uma manobra importante pode acabar com uma longa missão. O consumo atual de um microcircuito moderno pode variar muitas vezes, dependendo do modo de operação, ou seja, o consumo no modo “nada acontece e existe uma trava” pode ser menor do que no caso de operação regular em outro modo. Em que nível o limite atual deve ser definido? Também não está claro. O tempo necessário para desligar a energia e impedir a destruição do chip depende de muitos fatores, incluindo o chip específico.

Em algum lugar você não pode se apressar em qualquer lugar e redefinir a energia quantas vezes for necessário, mas em algum lugar após a primeira ou a segunda vez o chip ainda queima irreversivelmente.Em um microcircuito produzido usando a tecnologia SOI, o efeito do tiristor não pode ser, em princípio, porque todos os transistores são eletricamente separados. E o melhor é que, para obter resistência ao efeito do tiristor, você não precisa fazer nada. Ou seja, os microcircuitos comerciais fabricados de acordo com a tecnologia SOI também são absolutamente resistentes, o que facilita muito o uso no espaço. Assim, por exemplo, um processador SOI comercial controlará a nova espaçonave American Orion. Figura 11. Vazamentos induzidos por radiação na tecnologia CMOS a granel. Fonte - J. Schwank et al., "Efeitos da radiação em óxidos MOS", IEEE TNS, vol. 55, No. 4, 2008Qual é o problema? O fato de que, além dos efeitos da taxa de dose e da "trava", ainda existem falhas únicas e uma dose absorvida completa, com as quais a tecnologia KNI está longe de ser tão otimista. A figura mostra dois caminhos de fluência na tecnologia CMOS em massa. Ambos os caminhos são facilmente fechados com design topológico adequado - um usando transistores de anel n-canal e o segundo usando anéis de proteção. Essas soluções apresentam desvantagens do ponto de vista do funcionamento do circuito (restrições no tamanho mínimo de um transistor de anel, perda de área ao usar anéis de proteção), mas do ponto de vista de garantir a resistência à radiação, elas são muito eficazes.

Figura 11. Vazamentos induzidos por radiação na tecnologia CMOS a granel. Fonte - J. Schwank et al., "Efeitos da radiação em óxidos MOS", IEEE TNS, vol. 55, No. 4, 2008Qual é o problema? O fato de que, além dos efeitos da taxa de dose e da "trava", ainda existem falhas únicas e uma dose absorvida completa, com as quais a tecnologia KNI está longe de ser tão otimista. A figura mostra dois caminhos de fluência na tecnologia CMOS em massa. Ambos os caminhos são facilmente fechados com design topológico adequado - um usando transistores de anel n-canal e o segundo usando anéis de proteção. Essas soluções apresentam desvantagens do ponto de vista do funcionamento do circuito (restrições no tamanho mínimo de um transistor de anel, perda de área ao usar anéis de proteção), mas do ponto de vista de garantir a resistência à radiação, elas são muito eficazes. 12. .Na tecnologia SOI, há outro caminho de vazamento da fonte para drenar ao longo dos limites de silício e óxido latente. O óxido oculto é muito mais espesso que o portão, o que significa que muita carga positiva pode se acumular nele. Se considerarmos o transistor “inferior” (lado direito da Figura 12), para o qual o óxido latente é uma porta, veremos que, em uma situação normal, a tensão da porta de fonte desse transistor é zero e sua tensão limite é de várias dezenas de volts, ou seja, nenhuma corrente flui através deste transistor. Após a irradiação, uma carga positiva se acumula no óxido latente (a geometria do transistor principal afeta esse processo, em particular, a espessura da camada de instrumento de silício) e a tensão limiar do transistor de canal n "inferior" cai. Assim que cai abaixo de zero, a corrente começa a fluir livremente através do transistor através de um canal inferior não controlado.Assim, do ponto de vista da dose total absorvida, a tecnologia SOI é fundamentalmente estritamente pior que a tecnologia volumétrica. Mas talvez haja uma maneira de corrigir a situação?Normalmente, o substrato do microcircuito é aterrado, mas no SOI, nada nos impede de aplicar uma voltagem negativa a ele, e não ao terra, e assim fechar o transistor inferior? Por um lado, a ideia é sólida e é usada ativamente. Além disso, no caso de um SOI totalmente empobrecido (FDSOI) e normas de 45-28 nm, o monitoramento potencial sob óxido latente também é usado em operação normal. Por outro lado, o campo elétrico no óxido latente não apenas fecha o transistor parasitário, mas também acelera o acúmulo de uma carga positiva no óxido latente. Como resultado, dependendo dos parâmetros do processo e da magnitude da tensão negativa aplicada, a resistência à dose do microcircuito com a tensão negativa aplicada ao substrato pode não apenas não melhorar, mas também piorar! Além disso, como é geralmente o caso, existem sutilezas, mas fundamentalmente a situação éque os métodos topológicos e de circuito que utilizam a tecnologia volumétrica tornam possível atingir quase qualquer nível razoável de resistência a uma dose completa e, por "níveis razoáveis", entendo aqui, digamos 100 Mrad (Si). Na SOI, existem limitações fundamentais e o nível de resistência de um processo específico pode ser bastante baixo. Você não pode contornar essas limitações sem interferir na tecnologia (geralmente indisponível por razões comerciais) e não poderá descobrir os parâmetros de resistência à dose sem testes caros.e o nível de resistência de um processo específico pode ser bastante baixo. Você não pode contornar essas limitações sem interferir na tecnologia (geralmente não disponível por razões comerciais) e não poderá descobrir os parâmetros de resistência à dose sem testes caros.e o nível de resistência de um processo específico pode ser bastante baixo. Você não pode contornar essas limitações sem interferir na tecnologia (geralmente não disponível por razões comerciais) e não poderá descobrir os parâmetros de resistência à dose sem testes caros.A situação com falhas únicas no SOI não é menos interessante. Por um lado, há muito menos volume no SOI do qual a carga liberada quando uma partícula ionizante é coletada (embora as disputas entre os principais cientistas já existam há muitos anos sobre a forma exata desse volume). Por outro lado, a região do gate ("corpo") da SOI do transistor MOS é tão pequena que mesmo uma pequena carga que entra nele pode aumentar significativamente a tensão nele. Se a tensão subir o suficiente para abrir o corpo-fonte da junção pn, o transistor parasita-fonte-corpo-dreno será ativado e a carga introduzida pela partícula ionizante será multiplicada pelo ganho desse transistor. Na prática, isso significa uma queda no limiar LET para níveis abaixo de 1 MeV * cm ^ 2 / (mg), ou seja, qualquer coisa entrará no chip. Claroo efeito parasita do tiristor no SOI pode ser tratado anexando a região do portão à fonte do transistor ou ao solo / energia. Mas, primeiro, ninguém faz isso em microcircuitos comerciais (porque não há necessidade) e, em segundo lugar, o contato com o corpo é uma perda de área, especialmente sensível às chaves, onde deve ser independente. Cada célula de cache possui pelo menos duas chaves, o que leva a um aumento significativo na área do cache e do cristal como um todo. Ao mesmo tempo, na tecnologia volumétrica, para suprimir o efeito tiristor e o efeito bipolar parasitário, um contato em 4-8 células de memória pode ser suficiente, e até anéis de guarda podem ser feitos com menos perda de área do que nos contatos com o corpo do transistor no SOI. Uma vantagem importante do SOI em tecnologias profundamente submicrométricas é queesse isolamento dielétrico evita a propagação da carga e várias falhas com alta ampliação, que podem aparecer na tecnologia volumétrica. No entanto, o tamanho da trilha da partícula ionizante é comparável ao tamanho da célula de memória, e as falhas duplas no SOI são bastante registradas.No total, a situação com resistência à radiação do silício na tecnologia do isolador parece não ser "resistente à radiação em si mesma", mas possui várias vantagens e várias desvantagens em relação à tecnologia a granel. Parte das desvantagens do SOI pode ser contornada com a ajuda de técnicas especiais de design, mas o mesmo pode ser feito com a tecnologia volumétrica. Portanto, ao escolher um microcircuito comercial para uso em condições de exposição à radiação, não se pode confiar na SOI como uma panacéia, e ao escolher uma tecnologia para o desenvolvimento de um VLSI resistente a rádio especializado, é preciso pesar cuidadosamente os prós e contras da SOI e da tecnologia volumétrica para resolver um problema específico e fornecer os requisitos necessários. níveis de resistência a vários efeitos de radiação.

12. .Na tecnologia SOI, há outro caminho de vazamento da fonte para drenar ao longo dos limites de silício e óxido latente. O óxido oculto é muito mais espesso que o portão, o que significa que muita carga positiva pode se acumular nele. Se considerarmos o transistor “inferior” (lado direito da Figura 12), para o qual o óxido latente é uma porta, veremos que, em uma situação normal, a tensão da porta de fonte desse transistor é zero e sua tensão limite é de várias dezenas de volts, ou seja, nenhuma corrente flui através deste transistor. Após a irradiação, uma carga positiva se acumula no óxido latente (a geometria do transistor principal afeta esse processo, em particular, a espessura da camada de instrumento de silício) e a tensão limiar do transistor de canal n "inferior" cai. Assim que cai abaixo de zero, a corrente começa a fluir livremente através do transistor através de um canal inferior não controlado.Assim, do ponto de vista da dose total absorvida, a tecnologia SOI é fundamentalmente estritamente pior que a tecnologia volumétrica. Mas talvez haja uma maneira de corrigir a situação?Normalmente, o substrato do microcircuito é aterrado, mas no SOI, nada nos impede de aplicar uma voltagem negativa a ele, e não ao terra, e assim fechar o transistor inferior? Por um lado, a ideia é sólida e é usada ativamente. Além disso, no caso de um SOI totalmente empobrecido (FDSOI) e normas de 45-28 nm, o monitoramento potencial sob óxido latente também é usado em operação normal. Por outro lado, o campo elétrico no óxido latente não apenas fecha o transistor parasitário, mas também acelera o acúmulo de uma carga positiva no óxido latente. Como resultado, dependendo dos parâmetros do processo e da magnitude da tensão negativa aplicada, a resistência à dose do microcircuito com a tensão negativa aplicada ao substrato pode não apenas não melhorar, mas também piorar! Além disso, como é geralmente o caso, existem sutilezas, mas fundamentalmente a situação éque os métodos topológicos e de circuito que utilizam a tecnologia volumétrica tornam possível atingir quase qualquer nível razoável de resistência a uma dose completa e, por "níveis razoáveis", entendo aqui, digamos 100 Mrad (Si). Na SOI, existem limitações fundamentais e o nível de resistência de um processo específico pode ser bastante baixo. Você não pode contornar essas limitações sem interferir na tecnologia (geralmente indisponível por razões comerciais) e não poderá descobrir os parâmetros de resistência à dose sem testes caros.e o nível de resistência de um processo específico pode ser bastante baixo. Você não pode contornar essas limitações sem interferir na tecnologia (geralmente não disponível por razões comerciais) e não poderá descobrir os parâmetros de resistência à dose sem testes caros.e o nível de resistência de um processo específico pode ser bastante baixo. Você não pode contornar essas limitações sem interferir na tecnologia (geralmente não disponível por razões comerciais) e não poderá descobrir os parâmetros de resistência à dose sem testes caros.A situação com falhas únicas no SOI não é menos interessante. Por um lado, há muito menos volume no SOI do qual a carga liberada quando uma partícula ionizante é coletada (embora as disputas entre os principais cientistas já existam há muitos anos sobre a forma exata desse volume). Por outro lado, a região do gate ("corpo") da SOI do transistor MOS é tão pequena que mesmo uma pequena carga que entra nele pode aumentar significativamente a tensão nele. Se a tensão subir o suficiente para abrir o corpo-fonte da junção pn, o transistor parasita-fonte-corpo-dreno será ativado e a carga introduzida pela partícula ionizante será multiplicada pelo ganho desse transistor. Na prática, isso significa uma queda no limiar LET para níveis abaixo de 1 MeV * cm ^ 2 / (mg), ou seja, qualquer coisa entrará no chip. Claroo efeito parasita do tiristor no SOI pode ser tratado anexando a região do portão à fonte do transistor ou ao solo / energia. Mas, primeiro, ninguém faz isso em microcircuitos comerciais (porque não há necessidade) e, em segundo lugar, o contato com o corpo é uma perda de área, especialmente sensível às chaves, onde deve ser independente. Cada célula de cache possui pelo menos duas chaves, o que leva a um aumento significativo na área do cache e do cristal como um todo. Ao mesmo tempo, na tecnologia volumétrica, para suprimir o efeito tiristor e o efeito bipolar parasitário, um contato em 4-8 células de memória pode ser suficiente, e até anéis de guarda podem ser feitos com menos perda de área do que nos contatos com o corpo do transistor no SOI. Uma vantagem importante do SOI em tecnologias profundamente submicrométricas é queesse isolamento dielétrico evita a propagação da carga e várias falhas com alta ampliação, que podem aparecer na tecnologia volumétrica. No entanto, o tamanho da trilha da partícula ionizante é comparável ao tamanho da célula de memória, e as falhas duplas no SOI são bastante registradas.No total, a situação com resistência à radiação do silício na tecnologia do isolador parece não ser "resistente à radiação em si mesma", mas possui várias vantagens e várias desvantagens em relação à tecnologia a granel. Parte das desvantagens do SOI pode ser contornada com a ajuda de técnicas especiais de design, mas o mesmo pode ser feito com a tecnologia volumétrica. Portanto, ao escolher um microcircuito comercial para uso em condições de exposição à radiação, não se pode confiar na SOI como uma panacéia, e ao escolher uma tecnologia para o desenvolvimento de um VLSI resistente a rádio especializado, é preciso pesar cuidadosamente os prós e contras da SOI e da tecnologia volumétrica para resolver um problema específico e fornecer os requisitos necessários. níveis de resistência a vários efeitos de radiação.Conclusão

Centenas de milhares de especialistas em todo o mundo estão trabalhando para garantir a resistência à radiação dos circuitos integrados, e é impossível compreender a imensidão em um artigo científico popular. Sim, este tópico não é para o artigo e nem para a dissertação. De qualquer forma, não para a dissertação de candidato. Devido às especificidades do formato, colegas especialistas encontrarão aqui simplificações, imprecisões e talvez até erros reais. Eu gostaria que não, mas as mensagens sobre as edições necessárias são recebidas no PM. Sem pretender ser completo e inovador, espero ter conseguido descrever claramente as questões mais populares relacionadas à resistência à radiação e conceitos errôneos, bem como transmitir ao leitor a ideia de que a microeletrônica em geral e a microeletrônica espacial em particular são um dos campos que progridem mais rapidamente ciência e tecnologiaportanto, o conhecimento e os estereótipos testados pelo tempo costumam estar desatualizados, incompletos ou incorretos, e ninguém usa receitas simples e óbvias, porque na realidade elas não existem.