Você tem esse sonho: você se encontra em uma prova ou fala na frente de uma determinada platéia e, de repente, percebe que não estava se preparando e agora precisa improvisar. Foi nessa situação, mas não em um sonho, mas na vida real, que enfrentei as férias de maio em Moscou, onde voei da Califórnia para realizar um seminário de três dias para estudantes cuidadosamente selecionados das principais escolas de física de Moscou. Sob os auspícios de RUSNANO, no ginásio da RUT (MIIT) e na presença de professores do MIET, MIREA, MEPhI, MPEI e HSE MIEM.

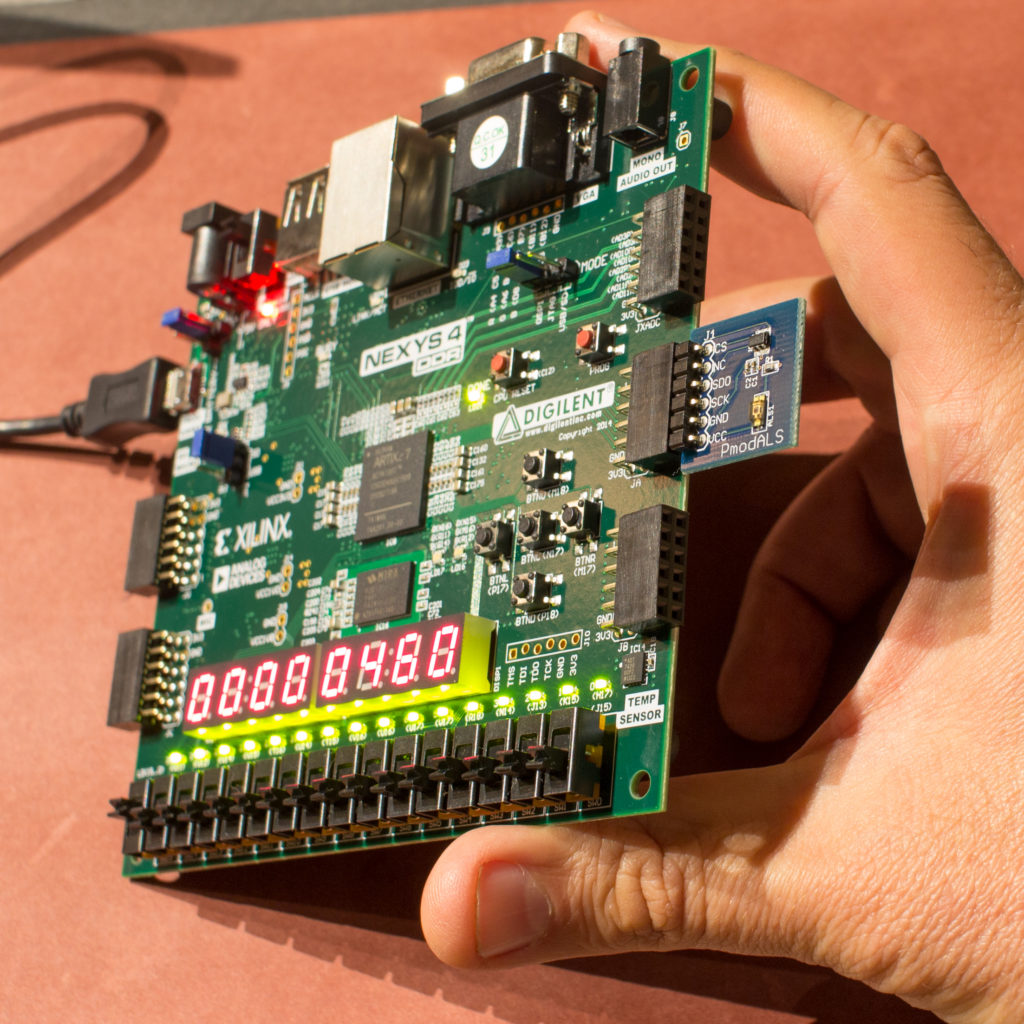

Meus colegas de Moscou esperavam por mim, e teoricamente eu deveria ter trazido instruções passo a passo e exemplos de vários exercícios em uma placa de circuito com um microcircuito lógico reconfigurável. Na verdade, eu tinha vários exemplos de outros conselhos, dos quais não construí nada na confusão de voos e outros eventos.

Portanto, tomei um exemplo universal, que escrevi há um ano e meio, sentado em um avião de Alma-Ata-Astana, joguei fora todo o interior do exemplo e comecei a preenchê-lo com crianças em idade escolar sem um plano rígido. E por incrível que pareça - funcionou. No processo de preenchimento, surgiram momentos instrutivos dos circuitos digitais e a linguagem de descrição de hardware da Verilog, que durante o planejamento não teriam surgido.

Em 4 de junho, eu e meus colegas da Wave Computing realizaremos um seminário semelhante em Las Vegas, mas apenas para adultos, e nos dias 8 e 19 de julho eu ajudo o MIET a conduzir uma escola de verão em Zelenograd. Planos para esses eventos (não finais, mas para discussão em um grupo de professores e engenheiros, inclusive aqui em Habré) - no final do post.

Por que precisamos de um seminário sobre FPGAs para crianças em idade escolar? Os circuitos lógicos programáveis (FPGAs ou FPGAs - Field Programmable Gate Arrays) são uma maneira tradicional de consolidar o conhecimento na prática ao estudar o design de circuitos digitais no nível de transferências de registros usando linguagens de descrição de hardware. Em outras palavras, a principal tecnologia para o desenvolvimento de iPhones - os microchips nos iPhones são projetados dessa maneira. O atraso da Rússia em relação aos iPhones também se deveu ao fato de que FPGAs, microarquitetura e linguagens de descrição de hardware foram introduzidas em Berkeley e MIT no início dos anos 90 e na Rússia devido ao colapso da URSS muito mais tarde.

O último seminário de Rosnanov foi surpreendentemente tranquilo, principalmente porque os alunos que o frequentaram haviam concluído anteriormente um curso teórico on-line com uma pesquisa orientada para a carreira dos métodos modernos de design de microcircuitos. O curso on-line é destinado a alunos avançados do tipo olimpíada e consiste em três módulos:

“Do transistor ao microcircuito” ,

“O lado lógico do circuito digital” e

“O lado físico do circuito digital” . Neste curso, os alunos se familiarizam com a chamada rota RTL2GDSII - um grupo de tecnologias que os engenheiros usam em empresas eletrônicas para projetar chips em massa, ASIC. FPGAs / FPGAs são usados para prototipar ASICs, incluindo empresas como Intel, Apple e NVidia.

Desde que os alunos fizeram o curso on-line, eles já aprenderam o que é o D-trigger, a máquina de estados, a síntese lógica e o rastreamento. Eles também viram a linguagem de descrição de hardware no curso online. Agora, esse conhecimento, que estava passivamente na memória deles, só precisava ser revivido.

Agora, sempre participarei de quaisquer seminários nos países da CEI (além dos seminários já planejados, tenho propostas para realizá-lo em Minsk, Sochi e Yakutsk) para definir a condição para o lado anfitrião pré-admitir crianças em idade escolar ou estudantes através de três módulos do curso on-line, desde depois restam apenas pessoas motivadas que já passaram por todos os aspectos tediosos, e a pura criatividade permanece como reforço, o último momento, como a queda de uma maçã que atingiu a cabeça de Newton. Além disso, o curso on-line vincula toda essa atividade a profissões para adultos, a próxima etapa traça um objetivo distante.

No total, antes de voar para Moscou, lancei um exemplo universal em minha casa em Sunnyvale, Califórnia.

Código de exemplo :

No primeiro dia do workshop, praticamos com microcircuitos com um pequeno grau de integração em uma tábua de pão. Essa tecnologia tem 50 anos, mas ninguém teve uma idéia melhor, na vida real, do que na simulação, de mostrar como os acionadores D funcionam, por exemplo. Embora pareça para muitos professores de tecnologia moderna nas escolas que isso esteja desatualizado e desnecessário, mas agora no curso 6.111 do Massachusetts Institute of Technology, agora, no ano acadêmico 2018/2019, o primeiro laboratório de circuitos digitais segue exatamente esse caminho com microcircuitos com um pequeno grau de integração - veja

http: //web.mit.edu/6.111/volume2/www/f2018/index.html .

Além disso, usando o exemplo de conexão de microcircuitos com um pequeno grau de integração com botões, é conveniente explicar o que é, por que é necessário e como os resistores pull-up funcionam. E por que eles dão um potencial de 0 quando o botão não é pressionado e como isso está relacionado ao divisor de tensão.

Mesmo quando, com o exemplo de um microcircuito de pequeno grau de integração, o LED queima, os alunos obtêm uma experiência de vida que é necessário colocar um resistor lá. Se eles virem isso na tela do computador em um simulador de software de uma tábua de pão, eles não terão uma experiência de vida, pois você pode desenhar qualquer coisa na tela e os alunos não terão certeza de que o desgaste é verdadeiro.

Aqui está como a função do D-flip-flop é claramente visível em microcircuitos com um pequeno grau de integração:

O segundo dia começou com um esboço histórico: como os microchips foram projetados 50 anos atrás e como mudou duas vezes desde então. Uma das revoluções foi sobreposta ao colapso da URSS e esta é a principal razão técnica pela qual a Rússia não possui iPhones.

Às 8h45, a história de como o espião bóia soviético, que monitorava o movimento de navios americanos, foi capturado nos oceanos e o que isso levou.

Em 13 de março, a história de como a publicação de um blogueiro John Cooley deslocou toda a indústria global de VHDL para Verilog.

Em 16.10, a história de como o Microsoft Windows perdeu para o Linux como uma plataforma para o trabalho de designers de chips.

Nesta parte - uma demonstração de como executar um programa para a síntese da lógica digital e configuração de firmware no FPGA. De duas maneiras - executando um script no Linux e em um shell gráfico integrado. Também uma breve descrição do conteúdo da demonstração. Após esse galope pela Europa, os alunos sentam-se na carcaça gráfica e fazem exercícios simples, começando com os elementos lógicos AND-OR-NOT, cujas entradas são conectadas aos botões e as saídas aos LEDs. Algo assim:

module top (input [2:0] key, output [7:0] led); wire a = ~ key [0]; // 0, , wire b = ~ key [1]; wire c = a & b; assign led [0] = ~ c; // , 0 endmodule

No processo, duas questões interessantes surgiram imediatamente. Primeiro, eu mesmo esqueci que os botões e os LEDs estão invertidos nesta placa. Ou seja, quando o botão é pressionado, então 0 no fio e, quando não pressionado, então 1. E quando 0 é alimentado pelo LED, ele está aceso e quando 1 não está aceso. Se você não conhece a inversão, o elemento lógico AND (led [0] = chave [0] e chave [1]) começa a se comportar como OR e OR - como I. Leis de Morgan em ação! ~ (a & b) == ~ a | ~ b, assim como ~ (a | b) == ~ a & ~ b.

Mas, mesmo depois que algumas crianças em idade escolar foram corrigidas, esse negócio ainda funcionava ao contrário. Depois, examinei o código deles e descobri que quando eles estavam reescrevendo o código que escrevi no quadro, eles pensaram que “~” (til) é “-” (menos). Isso me deu um excelente motivo para contar sobre a diferença entre código

direto e

adicional , e também por que, para números de um único bit (- 0) == 0 e (- 1) == 1, enquanto (~ 0) == 1 e (~ 1) == 0. E também, para calcular sua negação para números de vários bits em um código adicional, é suficiente invertê-lo em bits e adicionar um: - a == ((~ a) + 1).

Continuação - partes

2.3 ,

2.4 ,

2.5 .

Toda a lição foi realizada no Linux, mais precisamente no Lubuntu 18.04, com o Intel FPGA Quartus II instalado. O Lubuntu foi carregado com SSDs nos quais o Intel FPGA Quartus II Lite Edition 18.1 também foi instalado. Para inicializar a partir do SSD, basta conectá-lo à porta USB 3.0, ligue o computador e pressione F12. Então entre no menu e diga "carregar do USB".

Embora o software de síntese para FPGA também esteja disponível no Windows, o Linux é bom por dois motivos:

1. O Linux é capaz de rodar em computadores mais fracos que o Windows. Por exemplo, eu tenho um laptop com 2 gigabytes de memória, então o Intel FPGA / Altera Quartus II para Windows o estabelece e funciona bem no Linux.

2. Todos os desenvolvedores adultos de chips em massa da Apple, NVidia e outras empresas eletrônicas usam Linux, que executa os programas Synopsys Design Compiler, Synopsys IC Compiler, Synopsys VCS, Cadence IES, etc.

Por que é melhor fazer tudo em SSDs inicializáveis e não colocá-los em computadores na sala de aula? Como a instalação de software de empresas FPGA é um processo bastante sombrio, e no Altera Quartus ou no Xilinx Vivado você precisa executar com um pandeiro, alterar arquivos no / etc e instalar bibliotecas de 32 bits antigas para alguns componentes, em particular, para a versão gratuita do Mentor ModelSim. Algumas bibliotecas precisam ser compiladas a partir de códigos-fonte. Existem

scripts do Stanislav Zhelnio que fazem tudo automaticamente, mas mesmo com esse script, a instalação de tudo no computador leva algumas horas.

Por que não fazer tudo em máquinas virtuais? Por exemplo, com o VirtualBox? Tentamos fazer isso na Universidade Estadual de Moscou e em outros lugares, mas podem ocorrer falhas no uso do USB. Um SSD inicializável com Lubuntu parece a melhor opção.

Para preparar o conjunto de SSDs para o workshop, você precisa colocar tudo em um SSD e cloná-lo com um comando que permita gravar imediatamente em três SSDs de um:

time sudo dcfldd if=/dev/sdb bs=1M of=/dev/sdc of=/dev/sdd of=/dev/sde

Aqui você precisa saber que nem todos os gabinetes SSD suportam Linux, por exemplo, o Kingwin Data Star estraga os discos. Os gabinetes corretos são Orico e Eluteng.

Além disso, não recomendo tentar substituir os SSDs por unidades flash USB simples e disponíveis para download. Embora também funcione em pen drives, algumas operações são incrivelmente lentas, causando desconforto e irritação. Mas em unidades SSD carregadas com USB 3.0, tudo voa mais rápido que o Linux em um disco rígido interno.

Também tentei colocar uma unidade SSD inicializável no Apple Mac pressionando a tecla Opção no momento da inicialização, mas não deu certo. Nem pela porta USB 3.1 nem pela 3.0. Parece que o Mac na inicialização não deseja entender nem o sistema de arquivos Ext4 nem a tabela de partição. Existem drivers de papoula e linuxids entre meus leitores? Seria interessante saber o que fazer (além da opção de usar o VirtualBox ou outras máquinas virtuais).

Curiosamente, apenas 2 estudantes de todo o grupo usaram o Linux antes do seminário. Isso é muito estranho para mim, já que no lugar do Ministério da Educação da Rússia eu transferia todas as escolas de russo para o Linux há 10 anos, quando o Ubuntu se tornou fácil de usar. Além do Ubuntu, pode-se criar uma versão russa especial do Linux para educação. O Windows está entupido de vírus, você precisa pagar royalties por isso. Por que o Windows é melhor que o Linux para, por exemplo, os cursos escolares de programação em Python? Ou os documentos do Google não serão suficientes para crianças em idade escolar, mas o Microsoft Word é necessário? Eu simplesmente não entendo.

Até o governo sul-coreano decidiu em 2020 mudar para o Linux .

De qualquer forma, no meu seminário, as crianças em idade escolar não tiveram problemas com o Linux, embora, como eu disse, a maioria das crianças em idade escolar o tenha usado pela primeira vez.

No início do terceiro dia, eu estava atrasado porque fui convidado para dar uma palestra para a filial russa da Samsung e o evento se arrastou por 3 horas (você pode fazer o download dos slides da palestra:

1 ,

2 ,

3 e

um artigo sobre parte do conteúdo ), depois do qual fiquei com fome e apenas durante comer trigo sarraceno e olivier em Mumu (que realmente sinto falta na Califórnia) descobriu que minha aula no ginásio começaria em 5 minutos.

Então liguei para Alexander Silantiev do MIET e pedi para iniciar a lição sem mim. No dia anterior, os alunos começaram a se exercitar com um indicador de sete segmentos, exibindo uma letra. Agora, se você cruzar a saída de uma letra com um registro de deslocamento, poderá implementar a saída em um indicador dinâmico de sete segmentos e vários bits e, ao mesmo tempo, os alunos aprenderão a codificar a lógica seqüencial no veril.

O plano foi um sucesso - quando entrei na sala de aula, algumas crianças em idade escolar já estavam escrevendo letras lentamente no indicador dinâmico e, para que se fundissem em palavras, bastava aumentar a frequência da geração do sinal de habilitação (habilitar) para o registro de turno:

Então passei a palavra para Stanislav Zhelnio

sparf, da IVA Technologies, e ele descreveu brevemente como passar de blocos lógicos simples para um processador minúsculo, mas completamente real (veja as

postagens de Stanislav no Habr e

schoolMIPS no GitHub ):

Continuação da palestra de Stanislav ZhelnioO seminário foi realizado na Escola de Gramática da Universidade Russa de Transportes (MIIT). No seminário e antes dele, Irina Grunicheva e Gleb Romanov (eNano) ajudaram; Alexey Pereverzev, Alexander Silantiev e Yevgeny Primakov do MIET, Alexander Romanov do HSE MIEM e seus alunos, Alexei Kochnov do NIIIS, Liga dos Robôs (obraz.pro), Pavel Kirichenko (ICST, Intel, autor dos livros

bhv.ru/books/book. php? id = 201192 ), Yegor Kuzmin, do

Instituto de Matemática Aplicada , Academia Russa de Ciências, Daria Krivoruchko, uma estudante do SSC, estava no LYuP, Timofei Cherkasov (Academia de Tecnologias Digitais de São Petersburgo, Escola de Engenharia de Pensamento LNMO), Alexander Bakerenkov e Julia Shaltaeva da Pré-Universidade de MEPhI Vladimir Vorontsov de MPEI, Evgeny Pevtsov de MIREA, Vitaliy Kravchenko de Nautekh, Arkady Poe Yakov e Sergey Pevchenko de MEI.

Ruslan Tikhonov da Amperka trouxe componentes para exercícios com microcircuitos de pequeno grau de integração.

A editora Dmitry Movchan, da DMK Press, apresentou a cada participante livros úteis - um livro abrangente e abrangente de David Harris e Sarah Harris, circuitos digitais e arquitetura de computadores, e fácil leitura de A. Hideharu, Eletrônica divertida. Circuitos digitais. Mangá

Maxim Maslov, afiliado ao Instituto de Física e Tecnologia de Moscou, veio ao seminário e doou conselhos FPGA para escolas de verão (costumavam dizer que na Rússia há pouca caridade para a educação).

O que acontecerá depois? E então haverá dois eventos que irão expandir e aprofundar o que fizemos na RTH Grammar School. De 8 a 26 de julho será a escola de verão MIET em Zelenograd. Aqui está uma sugestão para o seu programa. Suas duas primeiras semanas consistem em cinco partes:

- O básico de circuitos digitais em microcircuitos com um pequeno grau de integração.

- Exercícios simples com lógica combinacional e seqüencial na placa FPGA.

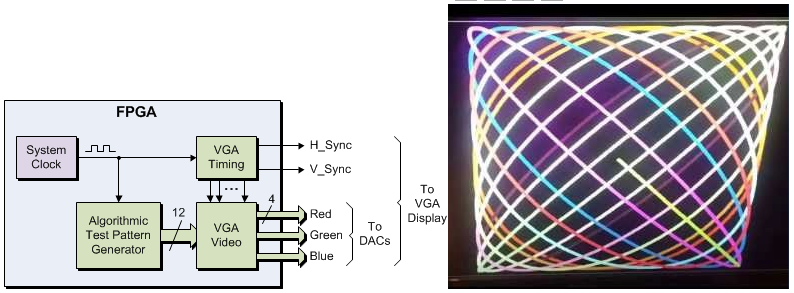

- Usando FPGAs para controlar a exibição gráfica.

- O dispositivo e a implementação do microprocessador mais simples no FPGA.

- Projetos individuais para criação de jogos, como o Angry Birds simplificado, ambos baseados na máquina de estado puramente no hardware FPGA e com controle de programa do processador mais simples sintetizado no FPGA.

Mas antes da escola, em 4 de junho, haverá um seminário em Las Vegas, no qual trataremos não do processador da escola, mas do industrial.

Programa mais detalhado em Zelenograd:

Semana 1. Noções básicas de lógica digital.

Dia 1. Circuitos integrados de pequena escala, exercícios de lógica combinatória

Dia 2. Microcircuitos com pequeno grau de integração, exercícios com lógica seqüencial

Dia 3. FPGA, exercícios com botões, interruptores, LED, indicador de sete segmentos

Dia 4. FPGA, saída de formas geométricas para VGA

Dia 5. FPGA, máquina de estado para Angry Birds

Semana 2. Processador

Dia 1. Programação em linguagem assembly.

Dia 2. Processador schoolMIPS de um ciclo.

Dia 3. Interação do processador com a conclusão de formas geométricas em VGA.

Dia 4. Palestra sobre interrupções e multitarefa. Projeto individual - um jogo de vídeo programado no processador com saída para VGA.

Dia 5. Palestra sobre o transportador. Concorrência de projetos individuais.

Semana 1. Dia 1. Circuitos integrados de pequena escala.

1.1 Exercícios com lógica combinatória.

1.1.1 Elemento lógico XOR no CD4070, sem botões e registros de pull-up - repita a demonstração.

1.1.2 Elemento lógico XOR, adicione botões e registros de pull-up - repita a demonstração.

1.1.3 Tarefa individual - por datashit para criar uma demonstração de um dos elementos lógicos AND / OR / NOT / XOR / NOR / NAND / XNOR, com duas, três, quatro ou oito entradas:

1.1.3.1 CD4081, quad 2 entradas AND

1.1.3.2 CD4071, Quad 2 entradas OU

1.1.3.3 CD4011, quad NAND de 2 entradas

1.1.3.4 CD4001, quad 2 entradas NOR

1.1.3.5 CD4073, AND triplo de 3 entradas

1.1.3.6 CD4025, NOR triplo com 3 entradas

1.1.3.7 CD4082, AND duplo de 4 entradas

1.1.3.8 CD4072, 4 entradas duplas OU

1.1.3.9 CD4012, NAND duplo de 4 entradas

1.1.3.10 CD4002, NOR com 4 entradas

1.1.3.11 CD4068, 8 entradas E NAND

1.1.3.12 CD4078, 8 entradas NOR

1.2 Indicador de 7 segmentos com um cátodo comum.

1.2.1 Monte em uma placa de ensaio com resistores, tente segmentos individuais.

1.2.2 Combinação com driver indicador de 7 segmentos, CD4511, decodificador de trava de BCD para 7 segmentos.

1.2.3 Opção - indicador com um ânodo comum. Combine com o inversor CD4069, Inversor.

1.2.4 Opção - adicione 4 botões com resistores pull-up à entrada CD4511.

1.3 Blocos lógicos combinacionais - uma tarefa individual no final do dia ou na forma de lição de casa:

1.3.1 CD4532, codificador de prioridade de 8 bits

1.3.2 CD4051, Switch analógico de 8 canais único, usado como decodificador digital

1.3.3 CD4051, Switch analógico de 8 canais único, usado como multiplexador digital

1.3.4 CD4052, Switch analógico duplo de 4 canais, usado como multiplexador digital

1.3.5 CD4053, Switch analógico triplo de 2 canais, usado como multiplexador digital

1.3.6 CD4008, somador combinatório de 4 bits

1.3.7 CD4063, Comparador digital de 4 bits

1.3.8 CD4585, Comparador digital de 4 bits

No final do dia, todos mostram quem fez o quê.

Semana 1. Dia 2. Exercícios com lógica seqüencial.

1.2.1 Monte um gerador de relógio baseado no chip 555. Tente diferentes capacitores e resistências.

1.2.2 D-trigger no chip CD4013, D-Flip-Flop duplo com reinicialização programada.

1.2.3 Projeto individual:

1.2.3.1 Registro de deslocamento baseado no CD4015, Registro de deslocamento estático duplo de 4 bits, entrada serial e saída paralela.

1.2.3.2 Registro de mudança com base no CD4035, Registro de mudança de quatro estágios, entrada paralela e saída paralela.

1.2.3.3 Registro de turno baseado no CD4014, registrador de turno de 8 estágios, entrada paralela e saída serial.

1.2.3.4 Contador com saída de LED CD4029, Binário Decimal Up Down Counter.

1.2.3.5 Contador com saída para um indicador de 7 segmentos através do driver.

1.2.3.6 Mais complexa é uma combinação de registradores de deslocamento CD4035 (entrada paralela, saída serial) com o somador serial CD4038. Precisa de um inversor CD4069. Antes disso, demonstrarei o somador serial CD4032 sem um inversor.

1.2.3.7 Mais complexa é uma combinação dos registros de turnos CD4014 (entrada paralela, saída serial) com o somador serial CD4038. Precisa de um inversor CD4069.

Semana 1. Dia 3. FPGA, exercícios com botões, interruptores, LED, indicador de sete segmentos

1.3.1 Um elemento lógico na lógica combinacional é entrada de botões, saída para LEDs.

1.3.2 A saída de uma letra em um indicador de sete segmentos.

1.3.3 O multiplexador mais simples é a saída em letra, dependendo da tecla pressionada. Implementação usando as construções "?", "If", "case".

1.3.4 Registro de turno.

1.3.5 A palavra é exibida em um indicador dinâmico de sete segmentos de oito bits usando um registro de deslocamento.

1.3.6 Projeto individual, talvez lição de casa para o fim de semana:

1.3.6.1 Formas na matriz de LED.

1.3.6.2 Cobra rodando em um indicador de sete segmentos.

1.3.6.3 Geração de sinal de frequência sonora, órgão sonoro.

1.3.6.4 Entrada de um teclado de 16 botões.

1.3.6.5 Bloqueio de código - reconhecimento de uma sequência de teclas por uma máquina de estado.

1.3.6.6 Integração com um sensor de rangefinder.

1.3.6.7 Integração com codificador de ângulo.

Dia 4. FPGA, saída de formas geométricas para VGA

Dia 5. FPGA, máquina de estado para Angry Birds

Semana 2. Processador

Dia 1. Programação em linguagem assembly.

Dia 2. Processador schoolMIPS de um ciclo.

Dia 3. Interação do processador com a conclusão de formas geométricas em VGA.

Dia 4. Palestra sobre interrupções e multitarefa. Projeto individual - um jogo de vídeo programado no processador com saída para VGA.

Dia 5. Palestra sobre o transportador. Concorrência de projetos individuais.

Semana 3. Rádio programável. O programa de blocos consiste em três partes principais:

- Noções básicas de eletrodinâmica e propagação de ondas de rádio (parte teórica);

- O princípio de operação do caminho do transceptor (teoria e prática);

- Noções básicas de processamento de sinal digital - filtragem, análise espectral (teoria e prática).

Dia 1. Fundamentos teóricos da eletrodinâmica e propagação de ondas de rádio. O diagrama estrutural do caminho de transmissão, as funções dos componentes. Sinais (harmônicos, retangulares). Prática de sinal usando o NI Elvis.

Dia 2. Transferindo sinais para uma alta frequência. Justificativa matemática para transferência de frequência usando o Matlab. Exercício prático em transferência de frequência usando o NI Datex.

Dia 3. Amplificação e emissão de sinais. Pratique usando o NI Datex. Demonstração da diretividade das antenas.

Dia 4. Filtrando o sinal. Pratique usando o NI Datex. Filtragem de sinais digitais em Matlab

Dia 5. Transferindo sinais para uma frequência baixa. Pratique usando o NI Datex. Resumindo o material coberto, resumindo.

Sobre o resto dos dias da escola, mais detalhes estarão em um post separado, depois de discutir isso no comitê organizador da escola de verão. Se você deseja participar da escola de verão do MIET em Zelenograd como estudante ou instrutor, os

organizadores acabaram de postar os contatos e a inscrição . Se você é um estudante, é importante que, até julho, você complete completamente os três módulos do curso on-line de Rosnanov (

“Do transistor ao microcircuito” ,

“O lado lógico do circuito digital” e

“O lado físico do circuito digital” ). A prática será difícil e não seremos capazes de parar para descobrir em qual ciclo o valor está na entrada ou saída do D-trigger. Isso não cabe imediatamente na sua cabeça, mas se você fizer um curso on-line, será mais fácil para você.

Alguns detalhes

sobre o seminário em Las Vegas em 4 de junho :

Não costuma acontecer que um seminário de engenharia, desenvolvido inicialmente para a Rússia e testado na Rússia (incluindo MIPT), Ucrânia e Cazaquistão, comece em Las Vegas, em uma conferência de automação de design eletrônico. Na Rússia e na Ucrânia, foi chamado de MIPSfpga Workshop e, na Design Automation Conference, foi chamado de MIPS Open Developer Day. Em 4 de junho, no Embassy Suites by Hilton Convention Center, na 3600 Paradise Road, Las Vegas, você participará de um programa que estudantes e professores da Universidade Estadual de Moscou, Instituto de Física e Tecnologia de Moscou, Instituto de Física de Engenharia de Moscou, Zelenograd MIET, São Petersburgo ITMO, São Petersburgo ITMO, Tomsk TSU, Kiev KPI, Almaty AlmaU e parcialmente Nazarbayev University em Astana.

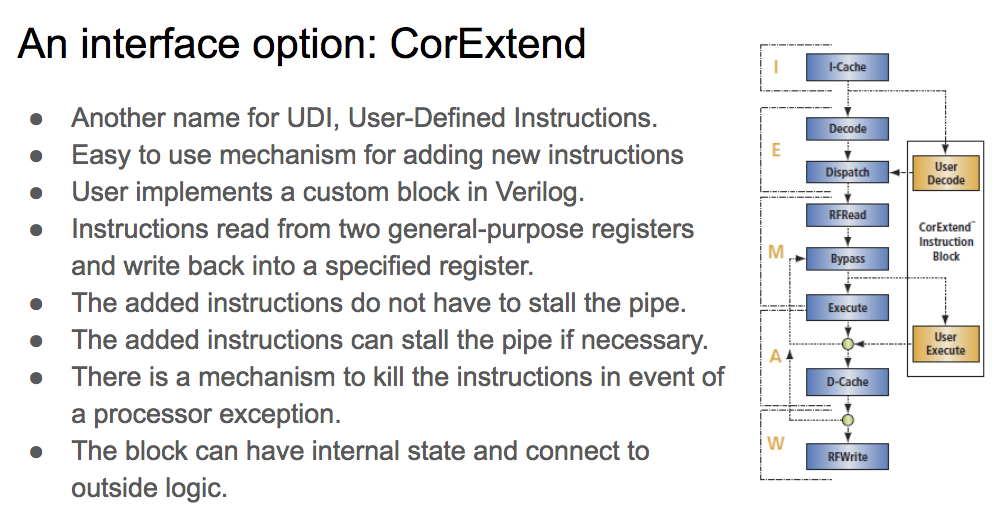

O MIPSfpga é um pacote que contém o núcleo do processador no código-fonte Verilog, que você pode alterar, adicionar novas instruções, observar a operação de cache e pipeline, criar sistemas multiprocessadores, alterar software e hardware ao mesmo tempo, etc. Na nova versão do seminário, você adicionará um coprocessador ao processador para acelerar os algoritmos de inteligência artificial.

Além disso, na nova versão do seminário, mostraremos como configurar o kernel do pacote MIPS microAptiv UP e inseri-lo na ligação MIPSfpga. Quando configurado, você pode criar opções exóticas de processador, por exemplo, um processador com 16 conjuntos de 32 registros. Você pode alternar automaticamente esses conjuntos ao inserir uma interrupção e, assim, alterar rapidamente o contexto sem salvar / restaurar o contexto da memória, que no RTOS comum leva cerca de mil ciclos.

O MIPSfpga não se destina a ser injetado em um objeto a partir do zero absoluto. Para seu uso frutífero, é necessário que o aluno já conheça o básico dos circuitos digitais, seja capaz de programar em C e em montador, além de apresentar os conceitos de microarquitetura - transporte, conflitos de tubulações, etc. É isso que está sendo estudado no schoolMIPS, que usamos em Zelenograd.

Aqui está um slide sobre o mecanismo para adicionar instruções ao processador MIPS microAptiv UP:

Em um seminário em Las Vegas em 4 de junho e provavelmente em uma escola de verão para jovens engenheiros eletrônicos, que será realizada de 8 a 26 de julho no MIET em Zelenograd, minha filha Elizabeth Panchul me ajudará (se receber um visto a tempo). Como Elizabeth é semi-russa-semi-russa / ucraniana, ela fala apenas inglês. Portanto, instrutores russos (estudantes ou estudantes de pós-graduação do Instituto de Física e Tecnologia de Moscou, Universidade Estadual de Moscou, etc., que estão prontos para nos ajudar com Elizabeth e o MIET na condução da escola) podem aprender o sotaque correto do inglês dela e dela - o básico do russo. Além de estudar Verilog, MIPS, arquitetura, microarquitetura e organizar DMA na memória quando exibido em uma tela gráfica:

Estamos esperando por você em todos os seminários, bem como em comitês para a criação de seus programas!