Foto possível de 10 nm IceLake. Fonte

Foto possível de 10 nm IceLake. FonteCoisas estranhas estão acontecendo no mercado de processadores. O líder mundial na pessoa da Intel vem lutando pelo quinto ano na tentativa de mudar para o processo de fabricação de 10 nm. Inicialmente, eles anunciaram a transição para 10 nm em 2015, depois em 2016, 2017 ... No quintal de 2019, e 10 nm da Intel na série não é. Bem, não, existem algumas amostras experimentais / de engenharia, mas um alto rendimento é um problema. Uma transição real é esperada

não antes de 2022 já.

Na verdade, esse foi o motivo da escassez de processadores Intel no mercado. Para superá-lo, a empresa expande a produção de processadores modificados de 14 nm (o mesmo lago apenas em perfil) e até retorna para 22 nm. Parece que a regressão é óbvia. No momento, a Samsung coreana, a TSMC de Taiwan e a AMD, que se juntaram à plataforma ZEN 2, estão relatando a introdução de até 7 nm e estão prestes a mudar para 5 nm. Eles tiraram a "Lei de Moore" do armário empoeirado e a declararam mais viva que todos os vivos. Em breve haverá 3 nm e 2 nm e até 1 nm (

sic! ) - pourquoi pas ?!

O que aconteceu? Os

asiáticos realmente

astutos venceram os

malditos pendos em um setor-chave?

Posso abrir champanhe?Isenção de responsabilidade: encontrei

este artigo por acidente e fiquei extremamente impressionado com a competência e os detalhes em que revela os problemas da microeletrônica moderna, em particular a morte da lei e do marketing de Moore. Era uma vez eu mesmo me dediquei a escrever artigos sobre

fabricação de chips e ,

na série de artigos “Inside Look”, eu até olhei dentro deles, ou seja, O tópico é extremamente interessante para mim. Naturalmente, gostaria que

o autor do artigo original o publicasse no Habré, mas em relação ao emprego, ele me permitiu transferi-lo para cá. Infelizmente, as regras do Habr não permitem copiar e colar diretamente, então adicionei links para fontes, imagens e um pouco de mordaça e tentei endireitar o texto um pouco. Sim, eu conheço e respeito os artigos (

1 e

2 ) sobre esse tópico da

amartology .

Então, vamos resolver o problema juntos. Vamos tentar, tanto quanto possível, nos aprofundarmos na física e na tecnologia, e não nos detalhes (das quais o nome é legião!). A descrição abaixo é simplificada e, às vezes, esquemática. Escreva comentários, tentaremos discutir construtivamente.

Prefácio

"Nem tudo é tão simples ...", dizia a filha de um oficial. Se você observar a densidade dos transistores, é quase o mesmo na tecnologia de 14 nm da Intel e na tecnologia de 7 nm da TSMC (

ooops !!! ). E mesmo a reversão da Intel para 22 nm não teve um grande impacto no desempenho. Que diabos? Por todas as regras, a transição da tecnologia de 14 nm para 7 nm deve aumentar a densidade dos transistores em até 4 vezes. E isso está de acordo com os preceitos de Gordon Moore, cujo

50º aniversário da lei foi celebrado recentemente, e no nariz está o 55º aniversário!

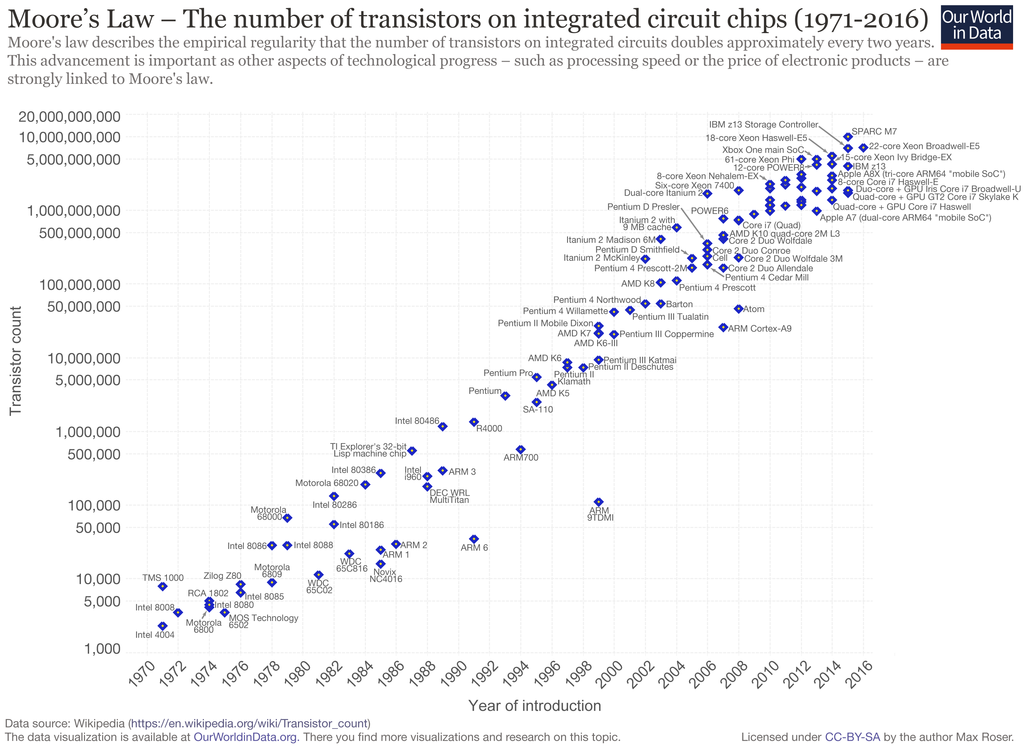

A lei de Moore fundida em ferro. Como você pode ver, estamos “marcando” no local há cerca de 5 anos.

A lei de Moore fundida em ferro. Como você pode ver, estamos “marcando” no local há cerca de 5 anos.Ao mesmo tempo, declarações confusas estão sendo feitas. Alguns argumentam que a "Lei de Moore" é mais relevante do que nunca, e a microeletrônica se desenvolverá como antes. Cientistas, designers e engenheiros brilhantes vão superar quaisquer limitações, até as leis da física. As pessoas exigem novas conquistas e não demoram muito.

Outros dizem que todos os caras atingiram os limites físicos, vamos lamber o que é, mas isso é normal. Isso foi avisado há muito tempo. Então, o chefe da NVIDIA

disse durante a CES 2019 que a lei de Moore está morta e agora o vetor (Huang não deve ser um vetor, mas um tensor) de desenvolvimento deve ser alterado. O especialista em litografia da AMD e da GlobalFoundries

concorda com ele.

De fato, todos esses padrões tecnológicos de unidades e dezenas de nanômetros há muito se divorciaram das dimensões físicas e se tornaram mais elementos de marketing. Pelo menos nos últimos 15 anos: após a transição de 130 nm para 90 nm. Foi então que, pela primeira vez, enfrentamos limitações não tecnológicas, mas físicas básicas. Os especialistas, a propósito, conversaram sobre isso, mas sua voz calma foi abafada pelas bravuras transmissões de profissionais de marketing que fingiram que nada havia acontecido, que tudo estava seguindo o seu caminho, de acordo com os preceitos de

Leni ... Dr. Moore.

Infelizmente, para os profissionais de marketing, e talvez felizmente para nós, a lei de Moore não é uma lei da natureza, mas uma observação empírica formulada em 1965 por um dos fundadores da Intel, Gordon Moore. Segundo suas observações, novas séries de microcircuitos saíram com um intervalo de um ano, enquanto o número de transistores neles cresceu cerca de 2 vezes. Em 1975, a lei foi alterada e, segundo ela, a duplicação deve ocorrer a cada 24 meses. Desde então, por quase 40 anos, a lei de Moore foi elevada à categoria de ícone e banner para fabricantes de microeletrônica digital, que às vezes são distorcidas (24 meses se transformaram em 36, agora estagnação - veja a foto acima).

Ao longo do caminho, surgiram várias limitações tecnológicas que retardaram o processo (a mesma transição através do limite de difração). Ou avanços que deram um forte aumento na miniaturização. Para um observador externo, tudo parecia um crescimento estável, em total conformidade com a lei de Moore, e não apenas pelos esforços dos profissionais de marketing.

Física de "Sua Majestade Silício"

Vou começar com ode de silício.

O silício é apenas um presente do céu para os fabricantes de microeletrônica. Além disso, literalmente, sob os pés, o silício também é um bom semicondutor com parâmetros muito adequados (em termos de combinação de características elétricas, energéticas e físicas). O silício puro é quase um dielétrico; a condutividade é completamente determinada pela concentração de impurezas. Possui alta condutividade térmica, é tecnologicamente avançado e é resistente a ambientes agressivos.

Likbez para iniciantesO silício a temperaturas comuns é um semicondutor com uma estrutura de cristal cúbico. 4 elétrons externos de átomos de silício são "socializados", isto é, pertencem a todos os átomos da rede cristalina. Eles não são livres, mas não estão rigidamente ligados ao seu átomo. Esta é uma característica dos semicondutores. Por um tempo, esses elétrons giram em torno de seu átomo, depois são transferidos para o vizinho, e os vizinhos entram em seu lugar. Assim, elétrons externos (valência) viajam aleatoriamente de átomo a átomo por todo o cristal (

nota: não exatamente, os próprios elétrons não viajam, apenas transferem energia através da interação entre si ). Ocasionalmente, algum tipo de elétron é completamente separado do átomo e começa (quase) a se mover livremente entre a rede cristalina. Em seu lugar, permanece um íon positivo de silício com uma vaga de elétrons não preenchida - um "buraco". Na próxima vez que os elétrons são encaminhados de um vizinho, a vaga é preenchida, mas aparece no vizinho, depois no vizinho, etc. O buraco também começa a viajar aleatoriamente através do cristal.

Se agora aplicarmos um campo elétrico, um elétron livre voará de menos para mais. Os elétrons de valência também estão sujeitos à ação do campo e começam a preencher rapidamente as vagas em direção ao lado positivo, e as vagas de buraco fluirão em direção ao lado negativo. Esse comportamento parece que um buraco é um portador de carga livre, um elétron tão livre, apenas com uma carga positiva. O comportamento do buraco é descrito pelas mesmas fórmulas do elétron, corrigidas para

uma "

massa efetiva " maior. Portanto, eles geralmente não são vaporizados e, por simplicidade, consideram que os orifícios são partículas elementares comuns com carga positiva.

À temperatura ambiente, um par de elétrons-buraco por trilhão de átomos de silício (concentração de 10 a

12 ), o silício puro à temperatura ambiente é um isolador (condicionalmente: elétrons e buracos se aniquilam muito rapidamente, não tendo tempo para chegar ao fim do cristal).

Se agora um átomo com 5 elétrons externos, por exemplo, fósforo, é introduzido na rede de silício, ele é incluído na troca de 4 elétrons e o quinto elétron fica livre. Obtemos íons positivos de fósforo e um "gás de elétron" incorporado no silício a partir de elétrons livres. A condutividade do silício com tal impureza aumenta linearmente; as concentrações de um átomo de fósforo por milhão de átomos de silício (

ppm ) já alteram drasticamente as propriedades elétricas. Uma mistura de fósforo é chamada de doador, e o próprio semicondutor é chamado

de condutividade do tipo N. Além do fósforo, pode ser arsênico ou antimônio.

Agora adicionamos átomos de silício puro com 3 elétrons externos, por exemplo, boro. Também está incluído na troca de 4 elétrons, mas pode fornecer apenas 3 elétrons. Nos átomos de silício vizinhos, um “buraco” aparece e parte em uma jornada através do cristal. Temos íons de boro negativos e um gás de buraco carregado positivamente. Essa impureza é chamada aceitadora e o semicondutor é

do tipo P. Além do boro, os aceitadores são alumínio, gálio e índio.

A propósito, o silício extremamente puro (de modo que é um isolante) é incrivelmente difícil de obter. A presença de boro

sempre faz do silício um semicondutor do tipo p.

Um bônus para o silício é o óxido - dióxido de silício SiO

2 . É um dielétrico quase perfeito, com alta resistência e dureza, resistente a todos os ácidos, exceto os fluorídricos (HF). Ao mesmo tempo, o ácido fluorídrico não dissolve o próprio silício, você não pode ter medo de conservar o excesso. Um fino filme de óxido é formado na superfície do silício, mesmo em temperatura ambiente (naturalmente, no ar). Para obter filmes espessos de óxido, o silício é aquecido ou é utilizada a deposição em baixa temperatura a partir de um gás contendo silício. A precipitação é usada quando as camadas já estão depositadas no cristal, e o aquecimento resultará em uma "mancha" da topologia.

Tédio de um químico, uma vez por ano do Sistema Periódico: um passo à direita - P, fósforo, óxido forma ácido fosfórico, à esquerda - Al, alumínio, metal, para cima - C, carbono, óxido - gás, para baixo - Ge com baixa prevalência na crosta terrestre (quilo) agora custa ~ 1k $).

Apesar das conversas constantes sobre o fim iminente da era do silício e a transição para outros semicondutores, por exemplo, as estruturas A

3 B

5 (aresenida de gálio, fosfeto de gálio ou nitreto de gálio), carboneto de silício, diamante,

grafeno e outros, uma vez que possuem maior mobilidade eletrônica efetiva e furos, menor dependência de temperatura, maior condutividade térmica, o silício reina na microeletrônica de massa.

Sim, para A

3 B

5, é possível criar

heterojunções . É quando as áreas dentro do transistor diferem não apenas no tipo de condutividade, mas também na estrutura física, o que oferece oportunidades adicionais. Em outras circunstâncias, os microcircuitos de nitreto de gálio podem operar com maior frequência, são resistentes a altas temperaturas e proporcionam melhor dissipação de calor. Mas enquanto esses materiais são usados apenas para elementos discretos e pequenos microcircuitos. Para microcircuitos grandes, a complexidade da tecnologia torna seus pedidos de magnitude superiores ao silício. Sim, e "outro igual" não é obtido. Portanto, microcircuitos alternativos sem silício têm uma especialização estreita.

MOSFETs

Considere o bloco principal de microcircuitos digitais - um transistor de campo plano (plano) com um canal induzido. Ele é

MOS (semicondutor de óxido de metal), ele é MIS (semicondutor de dielétrico de metal), ele é MOS (semicondutor de óxido de metal), ele é

MOSFET .

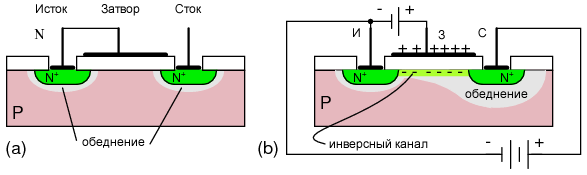

Vista esquemática em corte de um transistor de canal n

Vista esquemática em corte de um transistor de canal nDescrição dos princípios do trabalhoTemos um substrato de silicone de condutividade do tipo p. Criou 2 camadas do tipo n - fonte e dreno. Análogos do emissor e coletor em

transistores bipolares . Entre eles, um eletrodo separado do silício por uma camada dielétrica (geralmente óxido de silício) é uma porta. A área sob o obturador é chamada de base. Se aplicarmos uma tensão entre a fonte e o dreno, não haverá corrente, pois haverá uma

junção pn com polarização reversa entre elas - o transistor está fechado. Esquematicamente, este é um análogo de um diodo de bloqueio. Quando conectado corretamente, é uma transição entre a base e o dreno.

Agora aplique uma tensão positiva no portão. Um campo elétrico passa pelo óxido, penetra no silício, repele os furos (+) da camada superficial do buraco e atrai elétrons livres (-). Este último no substrato do tipo p, embora poucos, estejam presentes. A uma certa voltagem no portão, na camada superficial de elétrons, ela se torna mais do que buracos. A inversão ocorre e um canal do tipo n aparece sob a camada de óxido. Uma corrente fluirá da fonte para o dreno - o transistor está aberto. Um transistor aberto é uma unidade lógica, um fechado é um 0. lógico. Bem, ou vice-versa, dependendo da implementação.

Para transistores de canal p, as regiões n e p são trocadas e o transistor é aberto com uma tensão de porta negativa.

As vantagens dos transistores MOS são a compactação. Mas há também uma séria desvantagem - alto consumo de energia, uma vez que no estado aberto uma corrente contínua flui através do transistor. Portanto, desde a década de 1970,

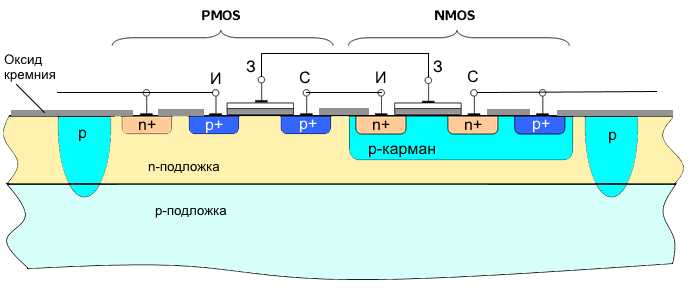

os transistores CMOS (

MOS complementares ) têm sido dominantes na tecnologia digital. São transistores de canal p e canal n conectados em série, com portas combinadas. Geralmente feito em uma célula.

Se alimentarmos os portões mais - o transistor de canal n está aberto, o canal p está fechado. Não há corrente contínua, menos a saída. Se alimentarmos o portão com um sinal de menos - o transistor de canal n está fechado, o canal p está aberto. Não há corrente de passagem novamente, mais saída. I.e. O elemento também funciona como um inversor.

Esta é a tecnologia com maior eficiência energética. Em um estado estático, o elemento não consome nada (exceto a corrente de fuga perdida), apenas a corrente de comutação é consumida. O consumo de energia é quase diretamente proporcional à frequência do chip (o número de ciclos de recarga). Baixo consumo de energia e compacidade determinaram o domínio da tecnologia CMOS na eletrônica digital.

Os circuitos de transistor bipolar inicialmente proporcionavam maior desempenho, mas eram mais complexos, ocupavam mais espaço e consumiam uma ordem de magnitude mais energia. Devo dizer que a escolha a favor do CMOS valeu a pena. Seria quase impossível obter características como os processadores atuais em outras tecnologias. E enquanto as alternativas não são visíveis no horizonte.

Recursos de topologia

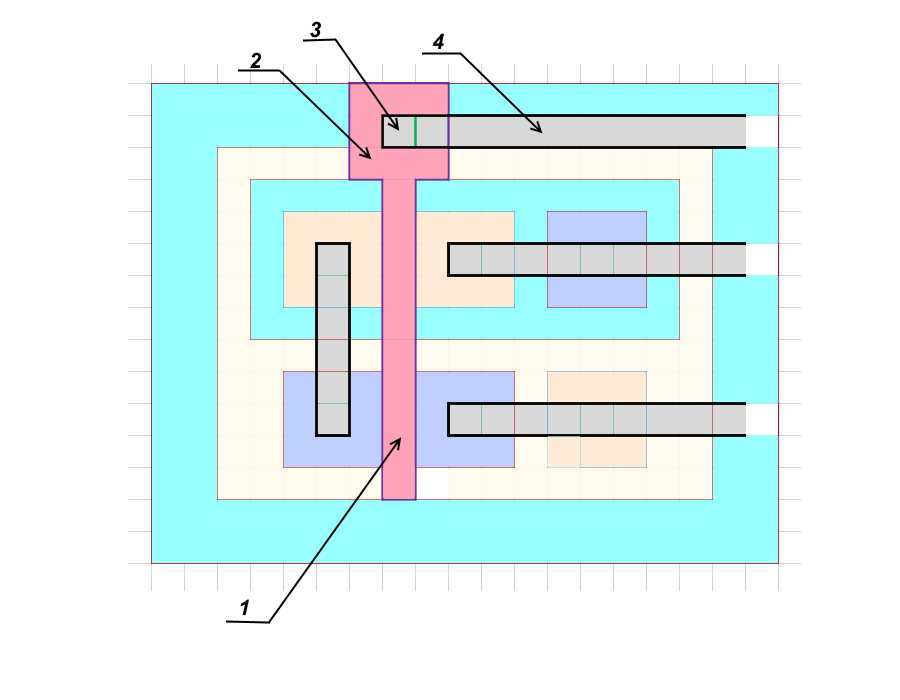

A topologia do chip pode ser convencionalmente representada como uma grande folha de papel em uma célula, onde os limites das áreas são desenhados ao longo das linhas e o tamanho tecnológico é o tamanho da célula. De fato, para elementos não críticos, você também pode recuar meia célula (a regra de duas lambdas), mas essas são nuances.

Projeto detalhado de topologiaVoltemos mentalmente ao final dos anos 80, quando as tecnologias ainda eram simples e compreensíveis. Considere um par real de transistores CMOS. As janelas n + ep + são altamente dopadas (1 átomo de impureza por várias centenas ou até dezenas de átomos de silício), ou seja, o nível de impurezas é uma ordem de magnitude superior a apenas n e p.

Suponha que recebamos TK para desenhar a topologia de um par de transistores em um bolso isolado. Como não haverá grandes correntes através de transistores, calcularemos com base no menor tamanho tecnológico possível, a chamada folga técnica. Chame de d.

Perfil

Perfil Vista superior

Vista superiorVamos começar com a janela de contato da fonte do transistor de canal n

(1) . Tornamos o menor

d * d possível.

A fonte

(2) terá o tamanho

3d * 3d (é necessário recuar pelo menos pelas bordas da janela).

A base

(3) é feita com a largura mínima

d .

Além disso, o material

(4) com sua janela de contato, também

3d * 3d .

O último elemento é a zona de alta liga

(5) para contato com a base-p e também

3d * 3d . É necessário equalizar a tensão da fonte e da base, para que a aparência espontânea do canal não ocorra.

Desenhe as bordas do próprio bolso-p

(6) , outro

d das janelas desenhadas. O tamanho da janela p é

5d * 13d .

Abaixo, desenhamos um transistor de canal p. Fazemos esse arranjo para aproximar todo o elemento a uma forma quadrada - é mais fácil de montar.

Mudamos a localização da fonte e drenamos. Esse arranjo minimiza o comprimento das faixas de metal de contato. Vamos começar com a janela de contato do dreno

(7) , o tamanho é mínimo -

d * d .

O dreno

(8) será

3d * 3d , a base

(9) tem largura

d e está alinhada com a base do transistor de canal n. A fonte

(10) e a área de contato altamente ligada à base

(11) também serão

3d * 3d .

O último tamanho é o recuo mínimo do caminho de divisão

(12) , outro

d .

O total recebeu o tamanho do par de transistores

11d * 15d . A trilha separada em nosso caso é outra região do tipo p, que com um substrato n forma uma junção pn com polarização reversa.

Existe outra opção para isolamento com dióxido de silício dielétrico SiO

2 ou safira Al

2 O

3 . A última opção é preferível, mas notavelmente mais cara. Nesse caso, as áreas podem ser formadas próximas ao caminho de divisão e a corrente de fuga entre as células será zero. Normalmente, a largura da pista de separação é ligeiramente maior que a espessura da camada epitaxial (mais sobre isso abaixo) e é igual a

2d .

O tamanho total da célula efetiva no meio dos caminhos de divisão é

13d * 17d .

Em seguida, na parte superior do óxido, desenhe um obturador

(1) , remova a área de contato

(2) do obturador mais perto do caminho de divisão e forme uma janela de contato

(3) .

A etapa final são os caminhos de metalização e contato

(4) . O alumínio foi originalmente usado como material do portão e dos caminhos de contato (embora o alumínio ainda seja usado

em alguns dispositivos ); posteriormente, o portão foi feito de silício policristalino de alta liga e os caminhos de contato foram feitos de cobre.

Suponha que vivamos em uma tecnologia de processo de

3 mícrons . Então, nossa célula de dois transistores

11d * 15d , como mostrado acima, terá um tamanho de

33 * 45 mícrons . Mas então estávamos com problemas, mudamos para uma nova tecnologia de processo de

1,5 mícrons . O tamanho da nossa célula se tornou

16,5 * 22,5 mícrons . , , . , ( ). , . . .

, . .

( )? .

(

). , (

.: , () , , , , .

CorneliusAgrippa :

, , (, ). , ). (boule) 200 300 , (

aka wafers ) 0,5-0,7 . . 450 , . ( , ).

, — . : , (SiCl

4 ). . , . p- n-. n- p-. .

, , p-, . , , , .

.

, 700 .

, , . . , , . , . , .

. , , . , . , , . .

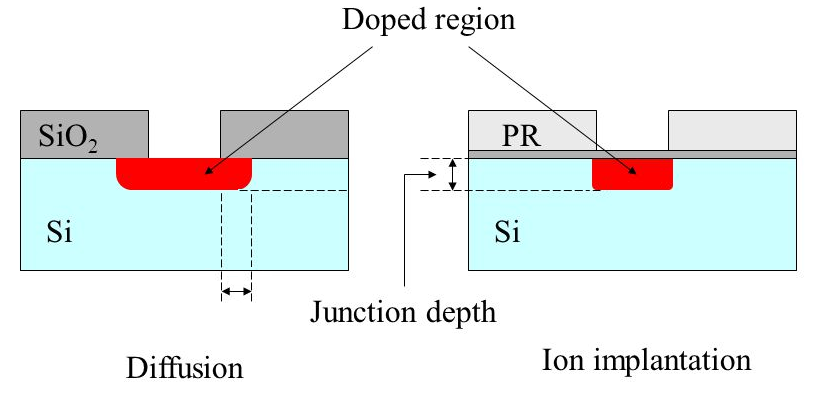

, . , , . . , . , , .

, , ,

.

tnenergy .

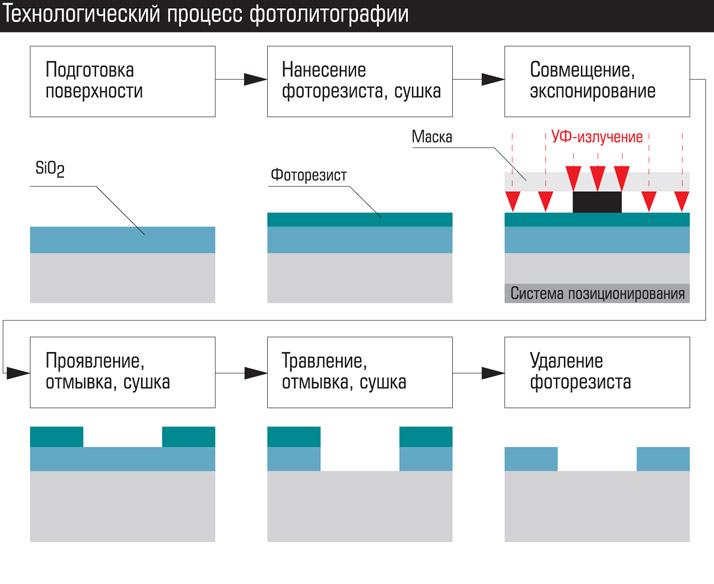

– . . ().

:

- .

- – . , .

- . – . , , p- . ( .: -) .

- . . , ( ) ( ). .

- – .

- . . , , ( shadowing effect).

- .

No final da operação, obtemos uma placa com porções de óxido removidas, que podem ser enviadas para difusão, implantação de íons ou deposição de metais (

nota: ou eletrodeposição). Depois de criar a camada, o óxido é geralmente gravado em toda a área da placa e uma nova é depositada.

O Windows cria do amplo ao estreito. No nosso caso, a sequência será a seguinte: áreas de separação, bolsos p, camadas p +, n + camadas, janelas de contato com metalização, aplicação do obturador, áreas de contato do obturador, a primeira camada de trilhos de metal com áreas de contato sob a segunda camada, a segunda camada de metalização, etc. . Nos processadores modernos, a metalização é de até 10 a 15 camadas.

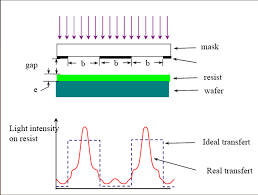

A fotolitografia de contato foi usada no início da microeletrônica. Agora, o principal é a fotolitografia de projeção. É quando os sistemas de lentes e espelhos são colocados entre a fonte de radiação e a máscara fotográfica para criar um feixe estreito de fótons. Métodos esquematicamente diferentes de fotolitografia são mostrados na figura abaixo: fotolitografia de contato, com uma lacuna, projeção através de lentes, espelho de projeção.

As vantagens da fotolitografia são alta velocidade e baixo custo. Toda a área da placa com todos os seus microcircuitos é exposta ao mesmo tempo e o processo leva vários minutos. Ou um quadrado de vários microcircuitos, seguido de uma troca de placas.

Além da fotolitografia, existem outros tipos - eletrônico, raio-x e iônico. O mais interessante é a litografia eletrônica (por exemplo, o projeto Mapper, sobre o qual

BarsMonster escreveu ).

Na litografia eletrônica, a exposição da resistência é realizada não pela luz, mas por um feixe de elétrons. Na sua forma mais simples, assemelha-se à formação de imagens nos tubos de imagem

CRT . De todos os tipos de litografia, é a litografia eletrônica que fornece a imagem mais nítida e a mais alta resolução. A desvantagem é o longo tempo de exposição. Nas tecnologias modernas, o feixe de elétrons tem uma espessura de alguns nanômetros e até frações de nanômetro, e o diâmetro da placa é de 300 mm. Naturalmente, não é usado um pacote, mas dezenas de milhares controlados por um computador. Mas é necessário um fluxo total de elétrons muito poderoso. Para comparação, a energia do quantum de radiação UV é de vários

eV , a energia eletrônica no feixe é de vários milhares de elétron-volts.

Além disso, os elétrons são eletricamente carregados e se repelem, o que leva a uma divergência de feixe. Obviamente, é possível aumentar a velocidade dos elétrons, mas eles perfuram a resistência ou refletem em alta velocidade em direções arbitrárias, causando radiação secundária (

elétrons secundários ) e, consequentemente, exposição. Tudo isso limita o uso da tecnologia.

A litografia eletrônica é usada para criar máscaras fotográficas. O tempo de exposição para uma máscara fotográfica é de vários dias. Portanto, a fotolitografia domina na produção de microcircuitos.

Um moderno conjunto de máscaras fotográficas para um processador custa dezenas de milhões de dólares. Não é de surpreender, dado que os processadores modernos contêm bilhões de transistores, e existem centenas de processadores disponíveis. Além disso, as janelas da máscara fotográfica moderna não são apenas buracos no material, mas geralmente outros materiais com propriedades ópticas específicas. Um conjunto real de máscaras fotográficas consiste em dezenas de máscaras. Nos mais recentes processos de fabricação, mais de 50 (

sic! ).

Mas eles permitem que você carimbe microchips como bolos quentes. Durante sua vida útil, um conjunto de modelos de fotos permite obter centenas de milhares ou até milhões de microchips na saída.

Então, o que limita o tamanho da tecnologia de processo?

4 grupos de fatores podem ser distinguidos condicionalmente:

- Hardware e tecnologia. Associado à resolução de hardware.

- Física dos processos tecnológicos. É determinado pelas limitações físicas de um processo específico, que podem ser contornadas por uma mudança na tecnologia ou nos materiais.

- Físico. Essas são limitações que não podem ser contornadas, mas seu impacto pode ser minimizado.

- Extrema física.

Limitações de hardware e tecnologia

Esse tipo de limitação foi decisivo nos estágios iniciais da microeletrônica. Refere-se principalmente à produção de "salas limpas", equipamentos sofisticados para processos técnicos, instrumentação (importante para o controle de qualidade dos produtos). Por exemplo, a fotolitografia requer ótica ultraprecisa, microscópios poderosos, mecanismos para combinar máscaras e placas com uma precisão de frações de nanômetros, uma atmosfera ultrapura ou vácuo durante a exposição e assim por diante. É necessário suportar com muita precisão os parâmetros dos processos tecnológicos - temperatura, duração, composição da atmosfera, potência da radiação, preparação da superfície.

Agora, a precisão do equipamento não é um fator limitante. Não porque é um problema simples. Basta olhar o diagrama de uma projeção moderna ou fotolitografia espelhada para entender o nível de complexidade. Mas aqui é realmente o caso quando não há barreiras para designers e engenheiros talentosos.

Problemas com a tecnologia são geralmente relevantes na primeira série. Com uma mudança na norma do processo técnico, não apenas os tamanhos horizontais, mas também os verticais, a concentração de impurezas e as proporções das zonas ativas mudam. E agora, a cada nova etapa, a física dos processos também está mudando. Naturalmente, todos os parâmetros são preliminarmente calculados e modelados, mas a realidade sempre faz ajustes. Portanto, para a primeira série, o rendimento de 3% dos circuitos adequados (97% com defeito) é considerado a norma. Gradualmente, os processos tecnológicos são otimizados e a porcentagem de rendimento adequada para as últimas séries passa de 90%.

Física dos processos tecnológicos

Por mais de 30 anos, até recentemente, eram esses fatores que limitavam. Eu já listei algumas dessas limitações - a entrada de impurezas sob o óxido durante a difusão, roer o óxido sob o fotorresistente durante a gravação e a erosão de camadas já depositadas durante processos térmicos.

Os métodos de solução também são parcialmente descritos.

A difusão foi substituída pelo implante de íons. Além disso, para as menores camadas, o material de impureza foi alterado - em vez de fósforo, o arsênico é usado, em vez de boro de gálio. Seus átomos são maiores e mais pesados; portanto, eles se dissolvem pior em silício às mesmas temperaturas (e o mais importante, é mais difícil para eles se difundirem!). Para a implantação de íons, isso não é importante, mas após o aquecimento subsequente, essas camadas se desgastam muito mais fracamente.

A produção de óxido por aquecimento substituiu a deposição catalítica a baixa temperatura do gás. O aquecimento é usado, mas apenas no início, enquanto o cristal está limpo. Em algumas operações, nitreto de silício (Si

3 N

4 ) ou camadas sucessivas de óxido e nitreto são usados em vez de óxido.

A gravação de ácido líquido foi alterada para gravação de íons. O ácido é usado apenas para remover o óxido de toda a área.

Outro problema foi a produção de óxido ultrapuro para um dielétrico de porta. Esse óxido permanece como um elemento de trabalho no chip e possui altos requisitos de pureza e uniformidade. A espessura do óxido em alguns locais é inferior a 10 camadas atômicas. Um pequeno defeito leva a um furo ou quebra. Isso fornece um fechamento elétrico do obturador para a base e a falha do elemento. Por algum tempo, uma alternância de uma camada de óxido e nitreto de silício foi usada. Na tecnologia de 90 nm, o óxido de háfnio HfO2 foi usado como um dielétrico de porta.

A propósito, durante a URSS, foram precisamente os problemas com a obtenção de óxido de alta qualidade que retardaram a transição para o CMOS. Daí a busca por caminhos alternativos e o atraso geral na microeletrônica digital.

A operação mais crítica é a fotolitografia. Tanto que até agora muitos colocaram um sinal de igualdade entre a resolução de todo o processo técnico e a resolução da fotolitografia. E o principal problema da fotolitografia desde o final dos anos 80 é a difração da luz. Mais precisamente, radiação ultravioleta, embora o princípio seja o mesmo. Não seria exagero dizer que por 30 anos a luta para reduzir o tamanho dos processos tecnológicos foi primariamente uma luta contra a difração.

A difração da luz foi descoberta no século XVIII pelos pais dos fundadores da óptica:

Ao penetrar no buraco, os raios de luz e qualquer outra radiação eletromagnética (EMP) desviam-se do caminho reto, divergem e penetram na área de sombra. O fenômeno é observado em tamanhos de furo próximos ao comprimento de onda. Quanto menor o buraco em comparação com a onda, mais forte a dispersão. A regra é válida até intervalos de um quarto de comprimento de onda. O furo tem menos de um quarto do comprimento de onda, o feixe EMP simplesmente “não vê” e é refletido da superfície com intervalos tão pequenos quanto os de um sólido.

O comprimento de onda dos LEDs de silicone é de cerca de 1 μm (próximo ao infravermelho), o comprimento de onda da luz visível de 780 nm (vermelho) a 380 nm (roxo). Menos de 380 nm, a radiação ultravioleta (UV) começa. Os emissores usados hoje em fotolitografia têm um comprimento de onda de 248 nm e 193 nm, que é a radiação dos lasers excímeros (por exemplo,

no XeF 2 ). Consequentemente, os problemas de difração atingiram seu auge após superar a barra de tecnologia de 3 mícrons e, após 800 nm, eles se tornaram dominantes. Devido à difração durante a exposição, o UVI entra na área sob uma máscara opaca e ilumina o fotorresistente na sombra. Como resultado, em vez de um quadrado claro, temos uma panqueca embaçada.

Além da erosão das janelas, há o efeito de sobreposição de ondas laterais (interferência) para janelas com espaçamento estreito. Os picos de reflexo aparecem bem abaixo da parte reflexiva da máscara fotográfica.

Óptica - sem coração você ...Quais métodos são usados para combater esse fenômeno?

Óptica - sem coração você ...Quais métodos são usados para combater esse fenômeno?O primeiro passo foi usar a fotolitografia de projeção. Se bastante simplificada, uma lente é instalada entre a foto-máscara e a placa, que coleta os raios divergentes e os focaliza no fotorresiste.

Outro método foi reduzir o comprimento de onda da radiação de exposição. Ao mesmo tempo, eles começaram com lâmpadas de arco de mercúrio com um comprimento de onda de radiação de 436 nm - isso é luz azul. Então 405 nm (violeta), 365 nm (quase ultravioleta). Com isso, terminou a era das lâmpadas de mercúrio, começou o uso de lasers excimer. Primeiro, 248 nm (ultravioleta médio), depois 193 nm (ultravioleta profundo). Sobre este processo e parado.

O fato é que eles atingiram os limites de transmissão da óptica de quartzo. Ondas mais curtas absorvem o quartzo. Era necessário mudar para sistemas de espelhamento ou usar lentes de outros materiais. Instalações experimentais a 157 nm foram feitas com base na óptica de fluoreto de cálcio. No entanto, eles nunca entraram na série. Como havia maneiras de otimizar a litografia de 193 nm.

Infografia visual em lasers.

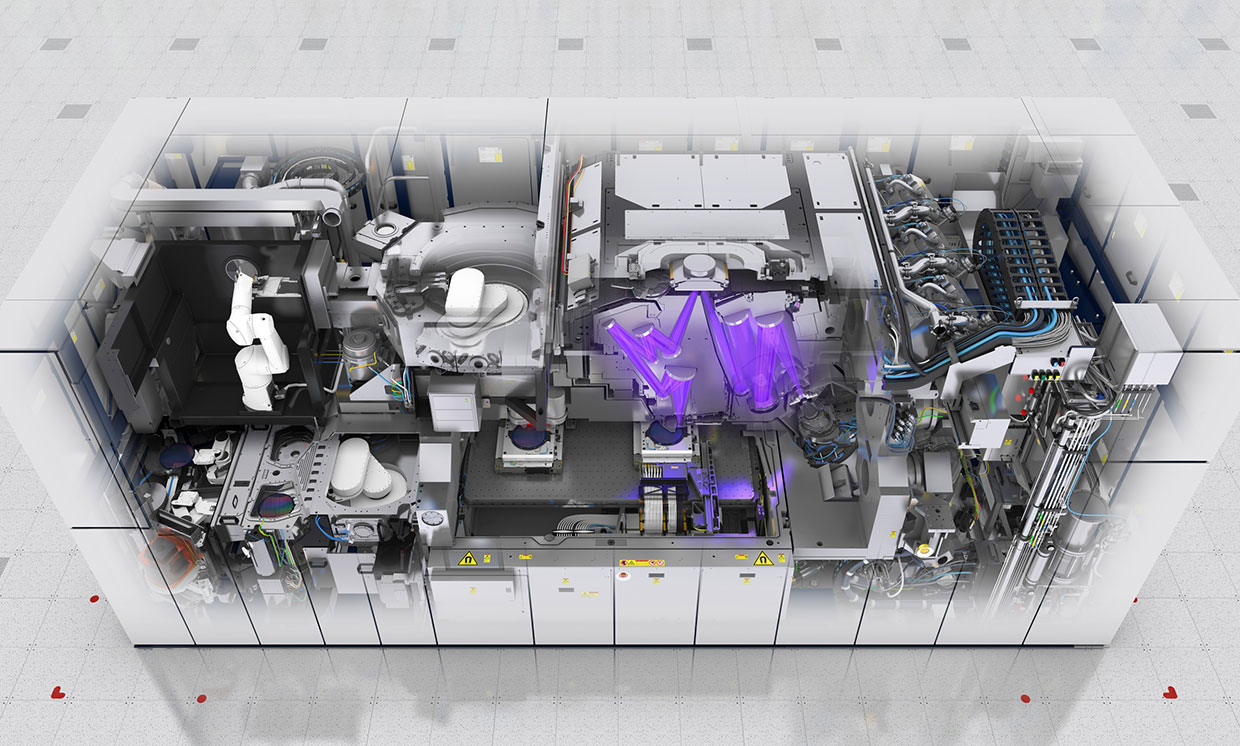

FonteLitografia EUV

Em meados da década de 1990, eles desenvolveram uma fotolitografia padrão em ultravioleta extremo (

litografia EUV ) com um comprimento de onda de 13,5 nm. Este comprimento de onda tornou possível dar uma resolução em unidades de nm.

No início dos anos 2000, as primeiras amostras experimentais apareceram.

No final dos anos 2000, a tecnologia deveria entrar em uma série. E finalmente, chegou a notícia de que em 2019 a Samsung e o TSMC de Taiwan mudarão para a litografia EUV. Menos de 15 anos se passaram (

sic! ). A Intel se tornou o principal antagonista da litografia EUV, embora fosse originalmente um dos iniciadores. Reconhecendo que tudo o que era possível foi extraído do UVI de 193 nm, eles anunciaram a transição para 126 nm (ha ha!).

Qual o motivo dessa rejeição?O fato é que 13,5 nm já é praticamente radiação de raios-x. A fronteira entre UVI e raio-X é convencionalmente considerada 10 nm, mas o ultravioleta não difere do raio-X macio no comportamento de 13,5 nm. Portanto, a litografia EUV é mais como raio-x. As lentes para esse comprimento de onda

não existem na natureza; portanto, é necessário mudar para espelhos a partir de camadas heterogêneas de metal.

Além de produzir uma estrutura muito fina e complexa, os espelhos de metal absorvem a maior parte da radiação. Unidades de porcentagem da potência inicial de radiação atingem o fotorresistente. Se levarmos em conta que a eficiência do próprio emissor também é de alguns por cento, para obter um tempo de exposição normal, são

necessários alta potência e alto consumo de energia (

ooops! ).

Este é o scanner ASML EUV

Este é o scanner ASML EUVA fonte de radiação é o plasma. Uma substância muito caprichosa, da qual é difícil obter um fluxo uniforme sem pulsações. Até o ar absorve ativamente 13,5 nm, portanto a exposição só pode ser realizada no vácuo.

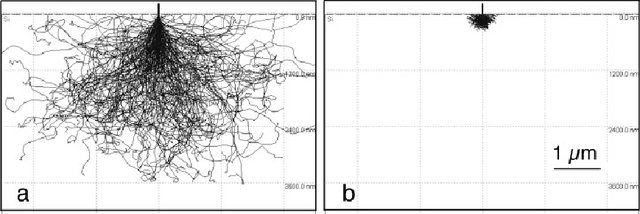

O problema com a seleção de fotorresiste. Quanto menor o comprimento de onda, maior a energia do fóton. Fontes anteriores forneceram energia em unidades de elétron-volts, essa é a energia usual de reações químicas. A energia do fóton para uma onda de 13,5 nm é de 92 elétron-volts. Essa é a energia de ligação de elétrons profundos. Ao absorver esse fóton, o elétron fica muito "quente", começa a se apressar, irradia excesso de energia e causa exposição secundária para fora da janela. Portanto, a seleção de um fotorresiste com o conjunto de parâmetros desejado também é uma tarefa difícil.

Resultados da simulação de Monte Carlo do deslocamento de elétrons em silício com energias de 20 e 5 eV. Fonte

Resultados da simulação de Monte Carlo do deslocamento de elétrons em silício com energias de 20 e 5 eV. FonteEssas dificuldades determinaram as razões pelas quais eles postergaram a transição para a EUV até a última.

Métodos reais de combate à difração

Assim, até recentemente, o mesmo UVI com comprimento de onda de 193 nm era usado como fonte de radiação. Até a tecnologia de 10 nm e 7 nm. E agora lembramos que a radiação não pode penetrar na lacuna se sua largura for menor que um quarto do comprimento de onda. Para 193 nm, é 48 nm. Surge a pergunta -

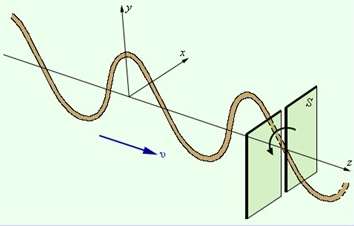

COMO ?!Este é o pequeno milagre que os engenheiros fizeram. Eles usaram o método de polarização de radiação.

Pegamos um espaço estreito retangular (com uma largura inferior a um quarto do comprimento de onda) e direcionamos a luz em direção a ele, polarizada ao longo do eixo. A luz passará através da abertura; mesmo a difração na direção transversal será insignificante.

E agora tomamos 2 slots perpendiculares: horizontal e vertical. Primeiro, irradiamos um fotorresistente de dois componentes com luz polarizada através de uma fenda vertical e depois através de uma horizontal. Apenas a área irradiada 2 vezes aparece. Assim como todos os engenhosos.

É verdade que você terá que usar 2 vezes mais modelos de fotos e 2 processos de exposição para criar uma janela. Mas você pode usar a boa e velha ótica de quartzo e os fotorresistentes comprovados por anos.

Esta é uma torção!Existem outras maneiras de combater a difração ...

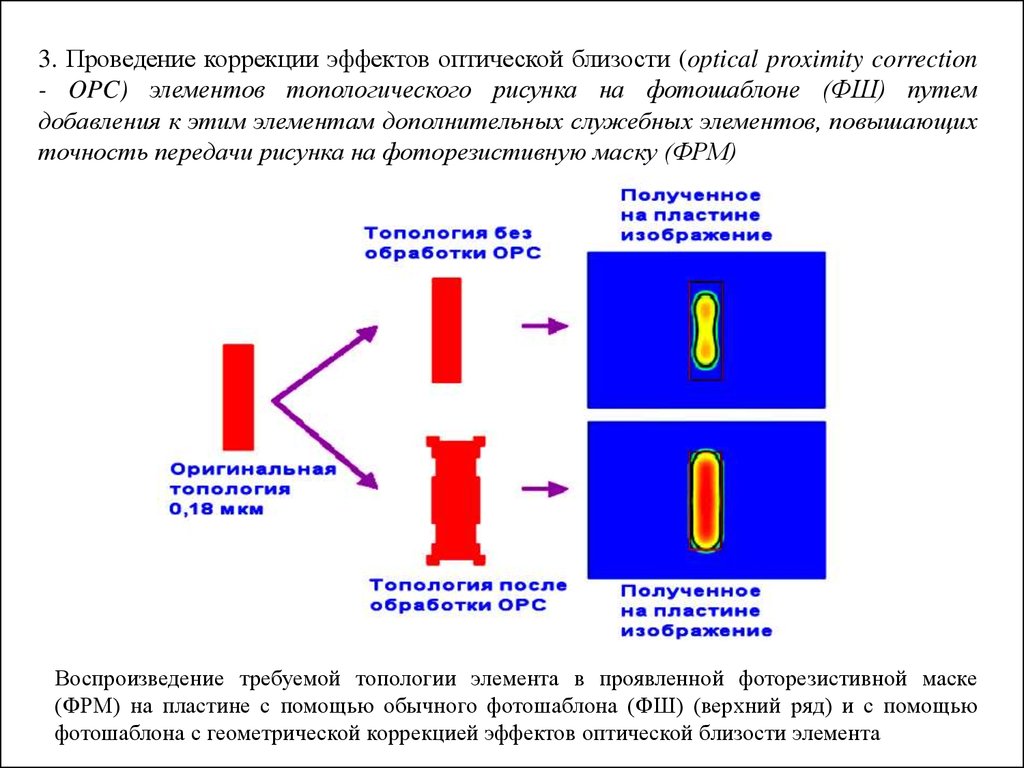

Correção óptica de proximidade. A forma das janelas da máscara fotográfica é feita de forma não retangular para compensar os defeitos durante a difração.

O método óptico de correção de proximidade é esquemático ...

O uso de máscaras de mudança de fase. Nas laterais da janela principal da máscara fotográfica, auxiliar, cujo material muda a fase da onda. Quando as ondas são aplicadas (

interferência ), elas cortam parcialmente os deslocamentos laterais um do outro.

Iluminação fora do eixo.

Iluminação fora do eixo. O feixe não cai perpendicularmente à superfície da placa, mas de duas fontes em um ângulo discreto. Ao aplicar fontes, os deslocamentos laterais são parcialmente compensados.

Exposição múltipla. Por exemplo, precisamos expor seis janelas próximas. Primeiro, conduzimos a exposição de 1, 3 e 5 janelas. E depois 2, 4 e 6. Isso aumenta o número de ciclos de exposição e modelos de fotos em 2 vezes, mas ainda melhor do que nada. Dada a polarização horizontal e vertical, obtemos 4 ciclos de exposição para criar uma camada.

Portanto, se olharmos para a máscara fotográfica moderna, não veremos as áreas do microcircuito de forma explícita. Haverá um conjunto de figuras horizontais e verticais que, quando sobrepostas, darão uma imagem. Na verdade, caracteres chineses sólidos: talvez seja por isso que os chineses ocuparam a produção de microeletrônica ?!

Após 45 nm, eles passaram para a fotolitografia de imersão. É quando o espaço entre a lente extrema e o fotorresistente é preenchido com líquido. No começo era água. Agora fluidos especiais com um alto índice de refração (até 1,8). O líquido reduz o comprimento de onda efetivo e neutraliza a refração da luz na interface da mídia.

Foi assim que eles atingiram a resolução de ~ 10 nm. Mas esse parece ser o limite para a litografia de 193 nm.

Foto da primeira camada de metalização para a tecnologia 24 nm. À esquerda, criada pela litografia de 193 nm, à direita, 13,5 nm (EUV). Como você pode ver, das formas retangulares claras anteriores existem apenas memórias. Ainda funciona.

Foto da primeira camada de metalização para a tecnologia 24 nm. À esquerda, criada pela litografia de 193 nm, à direita, 13,5 nm (EUV). Como você pode ver, das formas retangulares claras anteriores existem apenas memórias. Ainda funciona.Sobre limitações físicas, como elas afetam e como mudaram a produção

na segunda parte em alguns dias - fique atento!

Não se esqueça de se inscrever no

blog : não é difícil para você - estou satisfeito!

E sim, por favor, escreva sobre as deficiências observadas no texto no PM.