Na

primeira parte, examinamos brevemente a física do silício, a tecnologia de microeletrônica e as limitações tecnológicas. Agora vamos falar sobre limitações físicas e efeitos físicos que afetam o tamanho dos elementos em um transistor. Existem muitos deles, então vamos ver os principais. Aqui você tem que entrar na física, caso contrário nada.

Exoneração de responsabilidade: Era uma vez uma vez que escrevi artigos sobre

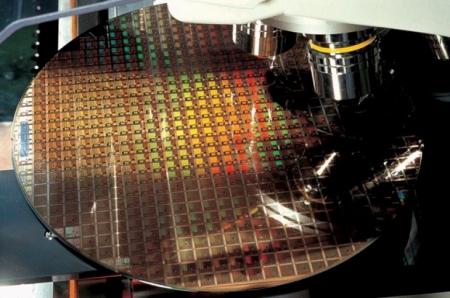

fabricação de chips e,

na série de artigos "Inside Look", até olhei dentro deles, ou seja, O tópico é extremamente interessante para mim. Naturalmente, gostaria que

o autor do artigo original o publicasse no Habré, mas em relação ao emprego, ele me permitiu transferi-lo para cá. Infelizmente, as regras do Habr não permitem copiar e colar diretamente, então adicionei links para fontes, imagens e um pouco de mordaça e tentei endireitar o texto um pouco. Sim, eu conheço e respeito os artigos (

1 e

2 ) sobre esse tópico da

amartology .

Efeitos físicos em microeletrônica

A ordem das quantidades básicas de silício

A concentração de átomos de silício no cristal é de 10

22 cm

-3Concentração de elétrons e orifícios intrínsecos à temperatura ambiente - 10

10 cm

-3Concentração de átomos de impureza de regiões levemente dopadas - 10

16 -10

18 cm

-3Concentração de átomos de impureza de regiões fortemente dopadas - 10

19 -10

20 cm

-3A concentração de átomos de impureza em regiões muito dopadas é de 10

21 cm

-3 . Nesse caso, já se fala de um

semicondutor degenerado , pois essa concentração (um átomo de impureza por 10 ou menos átomos de silício) altera a estrutura energética do cristal.

Dependências de temperatura das características do silício

Desde a primeira parte, lembramos que, à temperatura ambiente, o silício puro é um dielétrico. Um par elétron-buraco surge em apenas um de um trilhão de casos, mas essa fração aumenta exponencialmente com o aumento da temperatura. Existe uma coisa - a temperatura de duplicar a concentração de portadores de carga próprios. Para o silício, são cerca de 9 graus.

I.e. aumentar a temperatura em 9 graus, a porcentagem de átomos de silício em decomposição aumenta em 2 vezes; 18 graus - 4 vezes; 27 graus - 8 vezes; 36 graus - 16 vezes; 45 - 32 vezes; 90 - 1024 vezes; 180 - 10

6 vezes; 270 - 10

9 vezes.

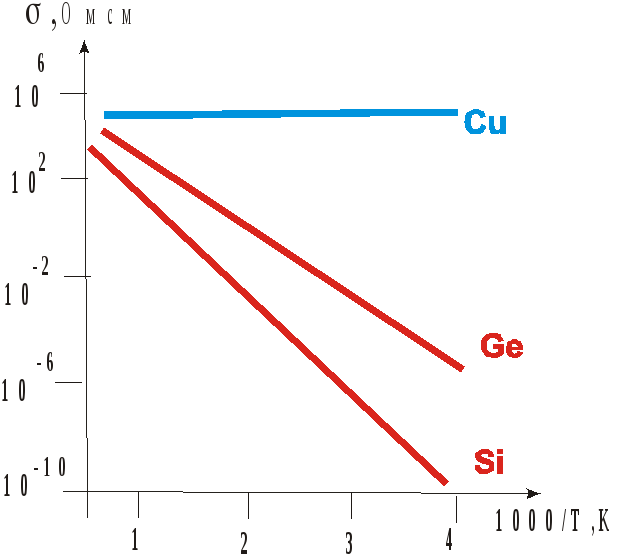

Comparação da condutividade térmica de cobre, silício e germânio. Fonte

Comparação da condutividade térmica de cobre, silício e germânio. FonteConcluímos que, quando aquecido a 200 graus (~ 2,1 no gráfico acima), a concentração intrínseca dos pares elétron-buraco se torna 10

16 , que é igual à concentração de impureza das camadas levemente dopadas. A 300 graus (~ 1,75) já 10

19 , esta é a concentração de camadas fortemente dopadas (n + ep +). A essa temperatura, o silício se transforma em condutor e os transistores perdem a capacidade de controle.

Os problemas começarão muito mais cedo. A temperatura no chip é irregular. Existem zonas de aquecimento local, geralmente no meio do chip. Se a temperatura em uma área pequena exceder 200 graus, devido ao aumento da condutividade intrínseca do silício, a corrente de fuga começará a aumentar. Isso leva a um aquecimento ainda maior e aumenta ainda mais a corrente de fuga e expande a área de superaquecimento. O processo se torna irreversível e ... boom. E irrevogavelmente. Portanto, em todos os microcircuitos grandes, a proteção automática contra superaquecimento é definida.

É por isso que é tão importante não permitir um forte aquecimento do cristal.

Para comparação, a concentração de elétrons intrínsecos e buracos no nitreto de gálio à temperatura ambiente é várias ordens de magnitude mais baixa, e a temperatura de duplicar o número de portadores de carga intrínseca é de cerca de 25 graus. Os problemas descritos acima no nitreto de gálio começam em cerca de 600-700 graus.

Corrente do túnel

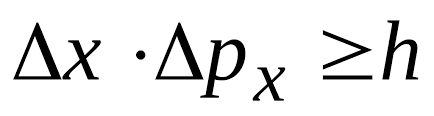

Esse fenômeno é complexo e simples ao mesmo tempo. As raízes estão na natureza quântica do elétron. Um elétron vive de acordo com as leis da mecânica quântica, que nem sempre são entendidas do ponto de vista da física clássica. De acordo com essas leis, um elétron não é apenas uma partícula, mas também uma onda, e seu comportamento pode ser calculado apenas com alguma probabilidade. Existe uma fórmula de Heisenberg:

É também chamada de

relação de incerteza de Heisenberg . Da fórmula resulta que os parâmetros espaciais do elétron não podem ser determinados com uma precisão maior que um determinado valor (constante de Planck). Em casos extremos da equação, se soubermos a localização exata do elétron, não saberemos nada sobre sua velocidade e direção do movimento. Se você souber exatamente a velocidade e a direção, nada será conhecido sobre o paradeiro dele. Acontece que o elétron é uma partícula tão borrada no espaço com picos de probabilidade de ser. A qualquer momento, um elétron pode estar em qualquer lugar do Universo sem nenhuma influência externa. É verdade que a probabilidade de sua aparência está muito longe da localização atual e é muito pequena.

Agora imagine a estrutura do tipo metal - dielétrico - semicondutor n (MIS). Em um metal, a concentração de elétrons livres é aproximadamente igual à concentração de átomos (10

22 / cm

3 ). Eles não podem penetrar em um dielétrico, porque para elétrons de um metal esta é uma região de energias proibidas. Dentro do dielétrico, uma onda de elétrons com energia como em um metal começará a interferir (se autodestruir). Mas eles podem se materializar em um semicondutor do tipo n, onde para eles existe uma zona de energias permitidas. Os elétrons passam de um metal para um semicondutor através de uma camada de óxido sem nenhuma influência externa, simplesmente por causa de sua natureza probabilística. Esta é a

corrente do

túnel . O processo em si é chamado de tunelamento, ou tunelamento quântico (soa mais legal!).

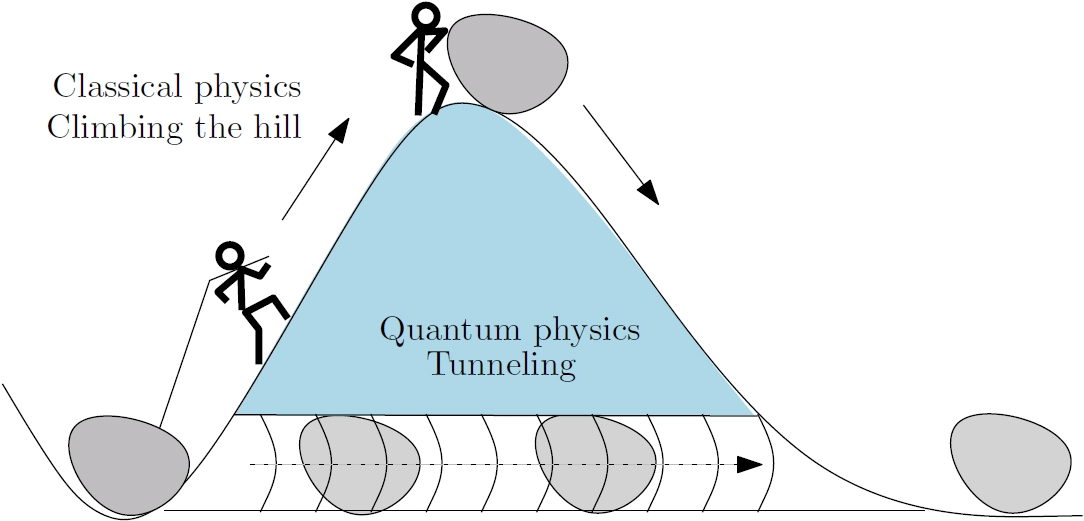

A energia adicional que teria que ser adicionada ao elétron para penetração "clássica" no óxido é chamada de barreira potencial. Esquematicamente, um elétron roe através de um túnel através de uma barreira potencial.

Há um fluxo na direção oposta - de um semicondutor para um metal. Mas como a concentração de elétrons livres no semicondutor é várias ordens de magnitude mais baixa, o fluxo reverso é proporcionalmente menor.

Um semicondutor do tipo p para elétrons de um metal também é uma banda de energias proibidas. No entanto, o processo inverso é possível aqui - o tunelamento de elétrons de valência de um semicondutor para um metal com a aparência de orifícios no silício. Parece que buracos estão escavando em metal. A intensidade, sendo outras coisas iguais, é cerca de 10 vezes menor que o tunelamento de elétrons livres.

A corrente de tunelamento para distâncias acima de 1 μm pode ser negligenciada. Probabilidade muito baixa e transições muito raras. À medida que a distância diminui, a probabilidade de transições espontâneas aumenta acentuadamente. A distâncias de unidades de nm, a corrente de tunelamento cresce 10 vezes ao se aproximar de 0,2 nm.

Um mecanismo semelhante funciona para as camadas de silicone npn. Para um elétron livre da região n, a região p é uma banda de energias proibidas, sem transições. Mas se a largura da base-p for muito estreita, os elétrons começarão a tunelar diretamente da fonte para a pia. Isso limita a largura básica máxima teórica a 8 nm. Em tamanhos menores, devido à corrente de tunelamento, o transistor de dreno de fonte se torna, em princípio, incontrolável.

Para estruturas pnp, a situação é semelhante, mas os buracos (elétrons de valência) escavam um túnel.

Nos semicondutores degenerados (fortemente dopados) na faixa de energias proibidas, existem ilhas de energias permitidas. Para eles, a opção de escavar um túnel através dessas ilhas é possível. Sobre como superar um riacho saltando sobre pedras furadas.

Região de Carga Espacial (SCR)

A região de carga espacial (SCR), também é a região de depleção, é também a região de carga espacial - é uma camada eletricamente carregada que se forma no limite das regiões n e p.

Conecte mentalmente 2 pedaços de silício, um tipo n, o outro tipo p. Na camada n existem muitos elétrons livres, na camada p existem muitos buracos, eles se movem aleatoriamente. Parte dos elétrons livres vai para a camada p, parte dos orifícios para a camada n. Como resultado, íons positivos não compensados permanecem na camada n e íons negativos não são compensados na camada p. Um campo elétrico local aparece ao longo do limite das regiões, o que começa a impedir novas transições. A intensidade do campo é máxima no limite e diminui gradualmente com a distância. No final, a força do campo torna-se tal que a transferência de orifícios e elétrons cessa e um estado de equilíbrio é estabelecido. Para o silício, a tensão desse campo interno é de cerca de 0,5 volts. Depende da concentração de impurezas dos dois lados. A dependência é fraca, cerca de 0,1 volts, quando a concentração muda 10 vezes.

Além da aparência de um campo elétrico na fronteira, há uma diminuição na concentração de elétrons e buracos livres. Diretamente no limite das camadas para zero. Daí o segundo nome - "região esgotada". A largura desta região depende da tensão na transição e da concentração de impurezas. A dependência da concentração de impurezas é inversamente quadrática, isto é, com um aumento na concentração de um fator de 100, a largura do SCR diminui de um fator de 10 (na verdade, um pouco menos, porque a tensão na junção aumenta).

Este é um estado em que a tensão externa não é aplicada à estrutura.

Se você aplicar uma tensão externa, ela será vetorizada com a interna.

Aplicamos uma pequena voltagem direta na junção, ou seja, mais (+) para a camada p, menos (-) para a camada n. Os campos externo e interno são direcionados em direções diferentes e começam a se compensar. A tensão de transição e a largura do SCR são reduzidas. Quando a tensão do campo externo se torna mais alta que a interna, o SCR desaparece, a junção pn se abre completamente. Para diodos semicondutores, existe até esse parâmetro - tensão limite. Essa é a tensão direta na qual o diodo se abre completamente.

Agora aplique a tensão reversa: menos (-) na camada p, mais (+) na camada n. Os campos externo e interno aumentam, a tensão na junção e a largura do SCR aumentam.

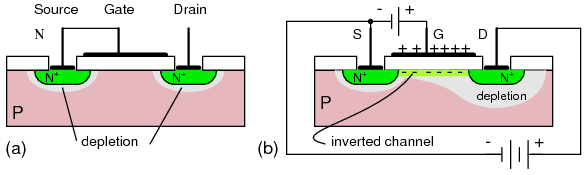

Se transferirmos este modelo para o nosso transistor de efeito de campo, obteremos a imagem abaixo:

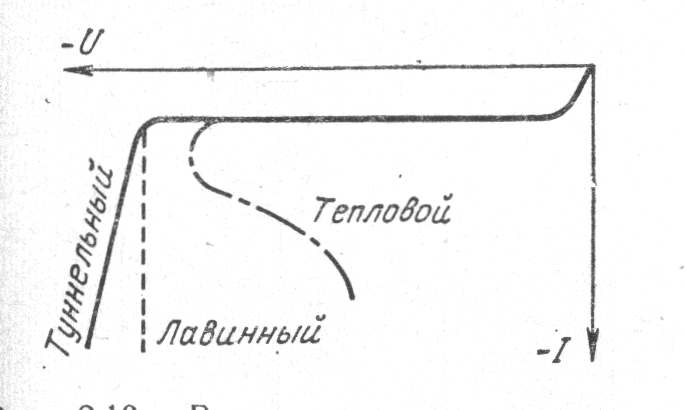

Rosa claro indica áreas esgotadas (SCR). Concluímos que a largura real da

base ativa , que é controlada pela tensão do portão, é menor que a distância do dreno da fonte. Ou seja, o tamanho da base menos a largura das transições do SCR. Na ausência de tensão de alimentação, a largura do SCR da fonte e do dreno é a mesma. Se você aplicar a tensão operacional, a largura do SCR do dreno aumenta, pois está sob polarização reversa. A base ativa está se estreitando ainda mais:

Se a base for muito curta, o SCR do dreno e da fonte será conectado. A largura da base ativa torna-se 0, e a corrente contínua flui do dreno para a fonte, o transistor é aberto. Independentemente da tensão no obturador. O transistor se torna incontrolável. O efeito é chamado de "punção de base" (

nota: como F376 observou corretamente , provavelmente estamos falando de "quebra de base").

Ainda existe uma opção intermediária quando o SCR não fecha, mas a distância da fonte até o limite do SCR do escoamento é menor que 8 nm. Então, no SCR, os elétrons começam a tunelar da fonte. Uma vez no SCR, eles são jogados no ralo por um campo elétrico. Simplificando, uma corrente de encapsulamento decente fluirá da fonte para o dreno.

Repartição das avalanches

Se o campo elétrico dentro do SCR ficar muito alto, um elétron que acidentalmente voa para ele acelera tanto que remove o elétron de um átomo neutro. 2 elétrons aparecem, eles novamente aceleram e retiram os elétrons dos seguintes, etc. O processo se assemelha a uma avalanche, daí o nome. Um canal condutor aparece no SCR através do qual a corrente flui. O transistor se abre espontaneamente.

Uma situação semelhante pode ocorrer no dielétrico do portão. Se a intensidade do campo estiver acima do limite, um elétron "rápido" que sai do metal acelera e causa uma avalanche.

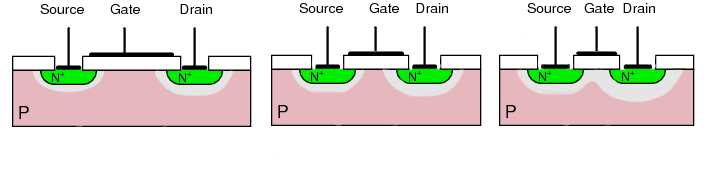

Uma comparação clara de diferentes tipos de discriminação. Fonte

Uma comparação clara de diferentes tipos de discriminação. FontePara evitar tal colapso de avalanche, é necessário evitar forças excessivas do campo acima do valor de colapso. Intensidade do campo = tensões / comprimento. I.e. é necessário reduzir a tensão e aumentar a largura do SCR (ou a espessura do dielétrico).

Áreas de resistência elétrica

Esta já é uma engenharia elétrica clássica. E o dreno, a fonte, o canal e até as faixas de metal condutoras têm sua própria resistência elétrica. A resistência é maior, quanto maior o comprimento da plotagem e menor a área da seção transversal.

Suponha que todos os elementos do transistor sejam reduzidos proporcionalmente em 2 vezes. Ao reduzir o comprimento, a resistência da seção

é reduzida em 2 vezes e a largura e a altura

aumentam em 4 vezes . No total, isso

aumenta a resistência do elemento em 2 vezes . Com a passagem da corrente, a resistência causa uma queda de tensão. Para tensões de transistor na região de 1 V e abaixo, mesmo uma pequena queda de tensão será crítica.

Para metalização, essa questão foi resolvida simplesmente - a primeira camada estreita de metal conecta apenas os elementos dentro da célula. Todo o resto é levado aos níveis superiores de metalização: ali a camada de óxido é mais espessa e as faixas mais largas. No entanto, o tamanho das janelas de contato e das faixas de metalização não pode ser infinitamente reduzido.

Para regiões de silício, um aumento na resistência foi compensado por um aumento na concentração de impurezas. Pelo menos até recentemente, até que os efeitos do tunelamento e do colapso começaram a afetar.

Outra maneira foi a tecnologia do "silicone esticado", ou "silicone esticado". Sua essência é que uma camada de germânio é depositada em um substrato de silício. O germânio é um elemento do mesmo grupo que o silício, semelhante na estrutura cristalina. No entanto, os átomos de germânio são maiores, respectivamente, a distância entre eles na estrutura cristalina é maior. Então, um fino filme epitaxial de silício é formado sobre o germânio. O silício no filme começa a repetir a estrutura cristalina do germânio; o passo da treliça de cristal será tanto no germânio quanto maior que no silício comum. Acontece que o silício é esticado em todas as direções. Daí o nome. Isso aumenta a mobilidade de elétrons e buracos.

O efeito combinado de efeitos físicos

Agora considere os efeitos desses efeitos juntos.

A principal ameaça na miniaturização de transistores é uma base de punção. Para removê-lo, você precisa reduzir a largura do SCR. Pode ser reduzido reduzindo o estresse externo e aumentando a concentração de impurezas na base.

A tensão de alimentação não tem onde reduzir, já está na região de 1V - cerca de dois limites. Se fizermos menos ainda, correremos o risco de obter uma abertura "arrastada" dos transistores devido à resistência elétrica.

Você pode aumentar a concentração de impurezas no banco de dados, mas obtemos:

- um aumento acentuado na corrente de fuga do túnel do dreno para a base;

- aumento do risco de sofrer uma avalanche de avalanche na transição;

- aumentando o limiar de tensão para induzir o canal, com o risco de sofrer uma quebra do dielétrico da porta.

Devido a essas limitações, a

concentração de impurezas na base é fixada em 10 18 -10 19 .

Todos esses fatores e os sem nome restringem a

largura mínima da base para transistores MOS de silício na região de 25 nm . É possível menos, mas a corrente de fuga se torna inadequada e a probabilidade de falha aumenta exponencialmente.

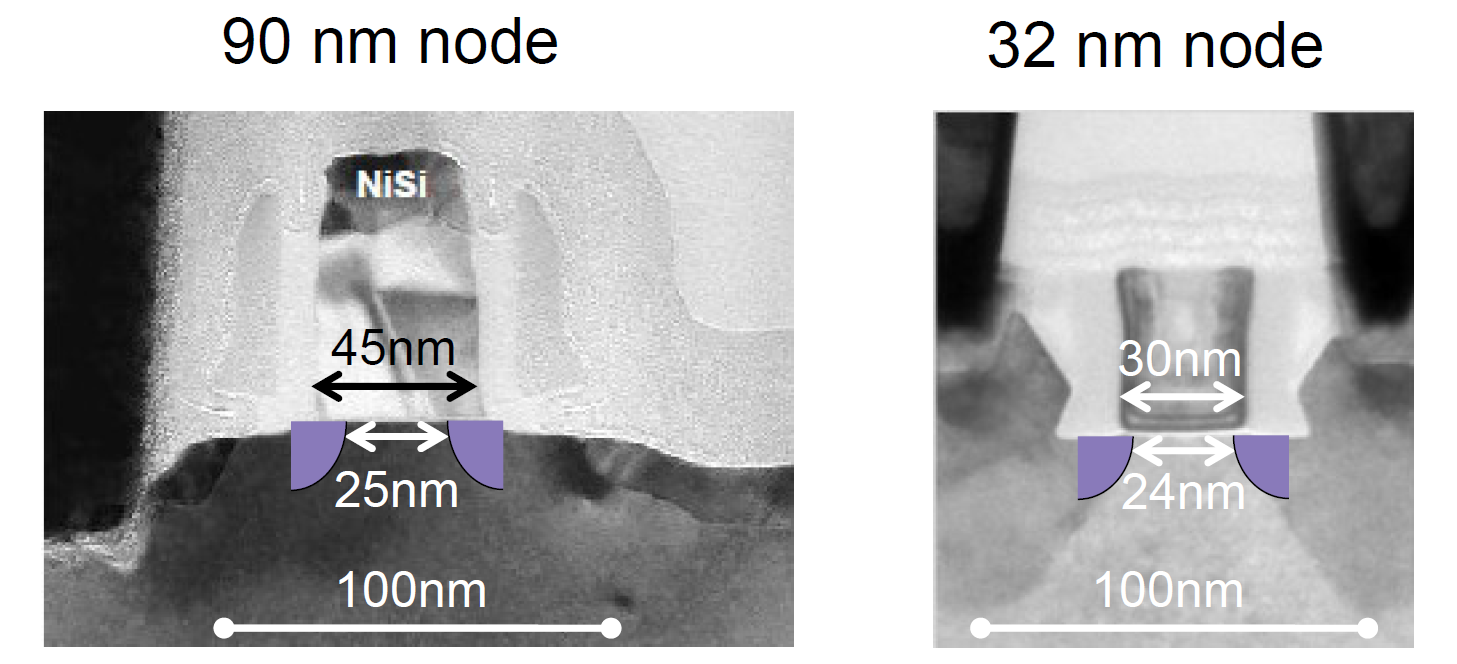

Micrografia de transistores fabricados em tecnologia de processo de 90 nm e 32 nm. Zoom e escala são idênticos. Fonte

Micrografia de transistores fabricados em tecnologia de processo de 90 nm e 32 nm. Zoom e escala são idênticos. FonteComo podemos ver, o tamanho dos contatos de metal se tornou muito menor, mas a largura da base não mudou. Todos os mesmos 25 nm. Além disso, para transistores que usam a tecnologia de 14 nm, 10 nm e 7 nm, é o mesmo (

ooops! ).

Isso foi encontrado pela primeira vez ao passar de 130 nm para as primeiras séries de 90 nm. Então, pela primeira vez, eles não puderam reduzir a largura da base na proporção de todos os outros tamanhos, permanecendo aproximadamente 35 nm. Mais tarde, ainda foi reduzido para 25 nm, mas desde então a largura da base não está mais sujeita às proporções da tecnologia. E quanto menores os transistores, mais isso se manifestava.

Foi necessário alterar os critérios dos processos técnicos. O que você fez? A maioria não fez nada. Eles continuaram a emitir permissão de fotolitografia como norma do processo tecnológico. Ou a largura mínima do caminho da metalização como uma manifestação da operação mais simples e intuitiva. E então passamos ao marketing ...

Os profissionais de marketing mais criativos vieram da Intel. Eles começaram a calcular a taxa de processo técnico a partir do tamanho dos elementos, por exemplo, com base na área da célula de seis transistores da memória estática. Na tecnologia com resolução litográfica de 65 nm, era de 0,77 μm

2 e, na resolução de 40 nm, era de 0,37 μm

2 . Se os tamanhos dos transistores foram reduzidos proporcionalmente como antes, isso corresponde à tecnologia de 45 nm. Então, assumiremos que temos tecnologia de 45 nm. Foi daí que surgiram as discrepâncias entre a tecnologia Intel e outras - 28 nm para todos, 32 nm para a Intel; 20 nm para todos, 22 nm para Intel; 10 nm para todos, 14 nm para Intel.

Como a história subseqüente mostrou, a Intel acabou sendo mais honesta do que seus concorrentes.

Efeito das correntes de fuga

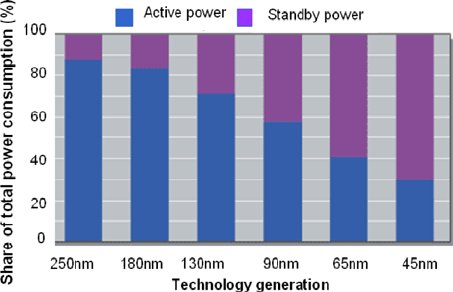

Há uma programação maravilhosa de um artigo já em 2010:

Fonte

FonteO gráfico mostra a porcentagem de trabalho e consumo de energia espúria. Azul - liberação de energia como resultado de correntes de recarga (corrente de operação), roxo - resultado de correntes de vazamento (corrente perdida). Isso leva em consideração as medidas que foram tomadas para reduzir as correntes dispersas.

A razão pela qual o crescimento da velocidade do clock do processador parou é claramente visível. Os primeiros processadores em 3 GHz (

Pentium 4 , por exemplo) apareceram no início dos anos 2000. Então, a este nível e ficou. Normalmente, isso é explicado pelo fato de o número de núcleos ter aumentado, a lógica ter se tornado mais complicada, o pipelining ter se aprofundado, de modo que os requisitos de estabilidade e, em geral, a felicidade em gigahertz aumentaram. Parcialmente verdade.

Mas! - .

, . , 2 , 4 , 6-7 . , , -. . , .

.

180 130 . , , .

. - , , . , 45 .

, 2000- .

, — .High-k . , NiSi. - .

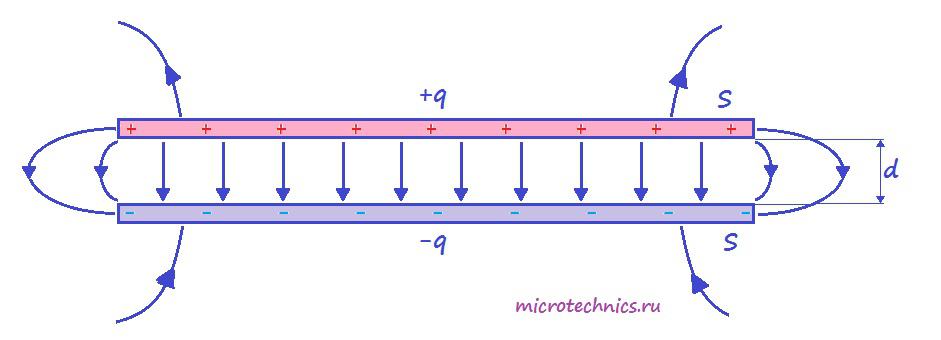

High-k. . , . , , . – – .

— . . , . . . :

S – ,

d – ,

ԑ – , 1, 1,

ԑ

0 – .

, . , . 1,2 (

sic! ). 6

(!!!) . . 5 , .. 1 , 10 (

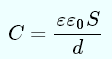

!!! ) ( 10 0,2 ). .

– . — High-k . HfO

2 Ta

2 O

5 . 3.9, High-k 25-30. , , - .

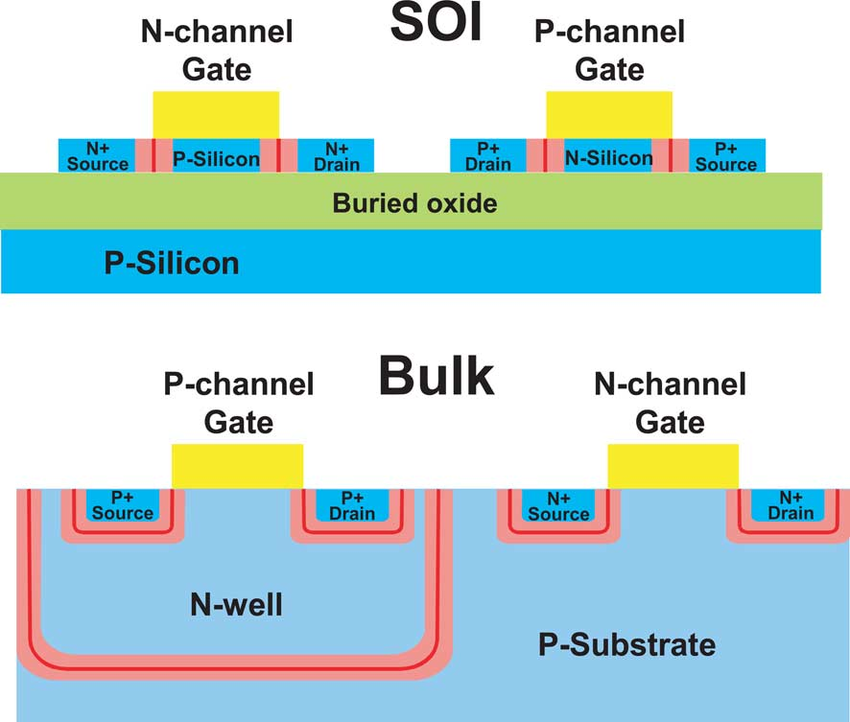

(SOI)

, , SOI, . : , (

UPD: , ,

SIMOX Smart Cut ).

SOI-

SOI-.

. . , - , . . . , .

Al

2 O

3 , . , . High-k 15 . .

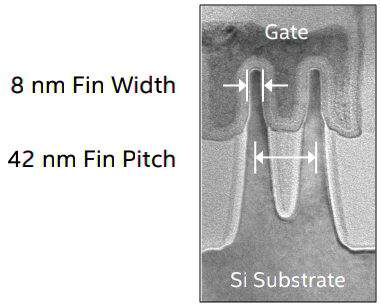

FinFET

Fin – , . 22 . , , .

UPD: FinFET

a5b , «».

, . Fonte

, . Fonte — . Fonte

— . Fonte. , () , . , , , . , .

- () . , .

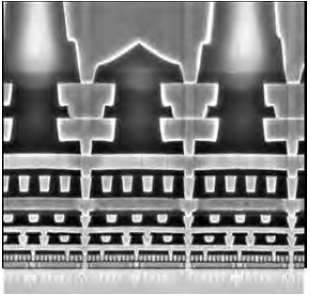

. 6 , 3 n-, 3 p- ( Fin ), (Gate), . , , ( 25 ), . . , 22 54 , 14 – 42 , 10 – 34 . .

3 , . Intel, Samsung TSMC. AMD – GlobalFoundries – . AMD TSMC Samsung.

, . , --. . , . . . , – , . , .

?! , . FinFET . High-k , , . . . I.e. .

I.e. . , 7 22 . FinFET 22 , 7 3 , . , , 10 7 1,8 . …

? . , Samsung GAAFET 5 .

CMOS, FinFET GAAFET . Fonte

CMOS, FinFET GAAFET . FonteI.e. , . : ? — .

UPD: F376 , FinFet . Gate-All-Around FET , .

, . FinFET SOI. , , .

.

Assim, os três líderes se destacaram - Intel, Samsung e TSMC. Intel produz sob suas próprias marcas, o resto está principalmente em ordem. Sob as marcas AMD, NVIDIA, Qualcomm, Apple, IBM estão escondendo chips fabricados nas fábricas TSMC ou Samsung. Alguns líderes antigos caíram ou se depararam com uma barreira. Os chineses estão tentando entrar na grande liga, mas até agora sem muito sucesso: eles não têm sua própria base tecnológica e os líderes mundiais na produção de equipamentos mantêm as últimas linhas tecnológicas para os chineses.

O otimismo dos especialistas está associado à transição para estruturas a granel e ao início do uso da litografia EUV. A Samsung e a TSMC começaram a usá-lo de forma limitada, para as estruturas mais delicadas. Isso lhes dá a oportunidade de informar sobre o alcance de padrões de 7 nm e, no futuro, até 5 nm. Embora, como já descrito, esses números realmente tenham pouco efeito. A mesma Intel geralmente abandonou o EUV. Aparentemente, eles não acreditam que isso melhore muito o desempenho.

Por outro lado, as pessoas no assunto entendem que a era Moore terminou e cada novo passo no crescimento da produtividade exigirá mais esforço e tempo. O rápido crescimento da microeletrônica termina (

soluço! ). Como isso aconteceu uma vez na indústria automotiva e na aviação. Após um crescimento explosivo, segue-se um desenvolvimento lento.

Entre os pontos de avanço promissores, pode-se destacar a transição para outro material (não o silício) e a criação de microcircuitos multicamadas (integração 3D - saudações às idéias da AMD). Para a integração 3D, você precisará reduzir drasticamente a geração de calor ou melhorar a dissipação de calor.

Isso é tudo para tamanhos de transistor. Há outras reservas de crescimento de produtividade em outra. Na otimização da arquitetura, por exemplo. Você pode até fazer uma jogada de marketing, dizendo que um novo processador com arquitetura aprimorada funciona como se fosse um antigo com tecnologia de 0,5 nm. Portanto, marcamos como 0,5 nm. E figs com ele que as dimensões dos transistores são as mesmas.

É possível criar novos tipos de células a partir de combinações de transistores. Por exemplo, em vez de 6 células de memória de transistor, faça 2 estruturas de transistor com física complexa de influência mútua. As estruturas volumétricas aqui oferecem muitas oportunidades.

Limites físicos

Alguém pode dizer que o pessimismo do autor não se justifica. Eles encontram maneiras de contornar as restrições. Talvez não tão rápido quanto antes, mas mesmo assim.

O fato é que ainda existem processos físicos que não podem ser ignorados. Os principais são compostos de átomos e os portadores de carga são elétrons. Criar um transistor menor que um átomo não funciona. Não funcionará para criar menos de 1000 átomos. Porque existe um elétron e a relação de incerteza de Heisenberg. Um elétron é uma partícula muito instável, um comportamento mais ou menos estável é possível apenas para uma matriz de milhares e milhões de elétrons. Em um elétron, você só pode destruir o gato Schrödinger.

Nota: embora haja desenvolvimentos em transistores de elétron único (

1 ,

2 e

3 )

Mesmo nos tamanhos atuais, as colisões ocorrem devido à operação espontânea dos transistores. Se a probabilidade de uma colisão for de 10 a

9 (um por bilhão), então, com o número de elementos em bilhões e frequências em GHz, isso fornecerá uma média de 1 colisão por ciclo ou vários bilhões de colisões por segundo. Para capturá-los, existem sistemas para monitorar a integridade das operações e uma operação suspeita é enviada para reexecução.

Com a miniaturização, o número de colisões começa a aumentar muito acentuadamente. Como resultado, chegamos a uma situação de efeito zero ou mesmo negativo da miniaturização. I.e. Os transistores fabricaram menos, se ajustaram mais ao cristal, mas, devido ao crescimento de colisões e ciclos de reprocessamento, a produtividade total não aumentou. Ou talvez até tenha caído. E esse limiar está bem no horizonte.

Algumas palavras sobre microeletrônica digital doméstica

Ao contrário da crença popular, até 1985 o atraso da URSS em relação aos líderes não era tão grande. Cerca de 3-4 anos. Isso acontece se tomarmos as empresas

líderes em Zelenograd (nota:

BarsMonster escreveu sobre a Micron

na época ). Segundo a lei de Moore, mesmo um atraso de 3 a 4 anos afetou bastante o desempenho. Houve problemas na obtenção de óxido de alta qualidade, com a clareza das junções pn. Se adicionarmos uma política conservadora à embalagem de chips no caso (longas linhas de contato não aumentaram a produtividade dos dispositivos), bem como aos padrões soviéticos para a produção de placas e estojos com um monte de ferro (aqueles que desmontaram os gravadores soviéticos entenderão), temos uma piada sobre o chip soviético com ferro fundido alças para transporte.

Há muitas razões para o backlog. Mais tarde startanuli, recursos limitados, recursos de pulverização. Quando os americanos se concentraram no CMOS, o nosso continuou a experimentar várias tecnologias. Eles trabalharam ativamente com alternativas de silício, principalmente com materiais A

3 B

5 . Bem, o relaxamento geral dos últimos institutos de pesquisa soviéticos.

Depois de 1985, os americanos começaram abruptamente e começamos a ter problemas. Então, a década de 1990, quando a vida na indústria era quente pela inércia. Como resultado, eles entraram no século XXI com tecnologia de 800 nm, quando os líderes já haviam invadido 130 nm. A segunda vida da indústria foi dada pela chipização em massa de cartões e pedidos do governo. A principal produção de aço: chips para cartões SIM, cartões bancários, cartões de pagamento, cartões de transporte e desconto e outros bens de consumo. Não são necessários grandes gigahertz e pequenos nanômetros.

Nota: a propósito, enquanto em Moscou há bilhetes únicos (comprados usados descartados, carregados com uma fábrica), na mesma China eles estão promovendo ativamente tecnologias de economia de recursos, em particular, o uso reutilizável do "token" no metrô (mesmo para uma curta viagem) .

Vídeo sobre o metrô de Shenzhen

No entanto, há uma tentativa de entrar na “grande liga” da microeletrônica. O desenvolvimento segue em quatro direções principais.

- Processos técnicos "soberanos". Uma tentativa de criar um ciclo completo de produção de equipamentos domésticos e nossos próprios processos tecnológicos. Seguimos o mesmo caminho que os líderes seguiram há 20 anos, mas levando em consideração o rake encontrado e as soluções. Desses, o que estava em código aberto é de 250 nm na série e 150 nm no processo de implementação. Isso também inclui uma tentativa de criar nossas próprias instalações de litografia EUV a 13,5 nm e, assim, sair imediatamente, se não nas grandes ligas, e próximo a elas.

- Compra de linhas tecnológicas dos principais fabricantes. O problema aqui é que as instalações mais modernas não foram vendidas para nós, mesmo nos melhores anos. Geralmente eles vendem linhas obsoletas que foram descontinuadas. Agora, em conexão com as sanções, mais ainda. Aqui podemos recordar o épico com a compra pela Angstrom dos equipamentos da planta AMD Dresden em 2007, sob o processo de fabricação de 180 nm. Ou a compra da linha Micron 90 nm da STMicroelectronics francesa, seguida de uma atualização para 65 nm. Embora este seja o processo de fabricação mais fino da Rússia, eles conseguiram arrebatar antes das sanções. É verdade que agora existe uma solução alternativa - compras na China.

- Encomende a produção em fábricas na China ou Taiwan. Ao mesmo tempo, arquitetura e topologia são totalmente desenvolvidas conosco,

agora fazemos até nossas próprias máscaras fotográficas . Os chineses só podem reproduzir os processos tecnológicos em suas fábricas. Temos processadores produtivos mais avançados e desenvolvemos competência no desenvolvimento dos mais modernos sistemas de processadores. Aqui, não um grupo de cientistas Kulibin está envolvido, mas grandes equipes de design. Somente a última seção, produção, é retirada do ciclo completo.

Nota: O Baikal é fabricado de acordo com os padrões de 28 nm na fábrica da TSMC. Um artigo sobre a saída de Baikal e sua análise.

- O desenvolvimento de tecnologias alternativas. Este é o desenvolvimento de tecnologias promissoras que podem se disseminar no futuro. Isso inclui trabalhos sobre compostos e heteroestruturas A 3 B 5 , principalmente arseneto de gálio e nitreto. Assim como as tentativas de otimizar a litografia por feixe de elétrons e raios X para produção em massa, o que geralmente remove as limitações da litografia.

Nota: herdamos uma forte escola de heteroestruturas do final de Alferov, mas mesmo com o apoio do Estado, o OptoGaN não o estendeu , o mercado e as condições do mercado estão falhando.

Em geral, a situação não é brilhante para a microeletrônica russa. Mas há esperança de que os líderes desacelerem inevitavelmente devido a limitações físicas, e aqui nós, lentamente, nos arrastando para trás.

O acorde final sobre memória e janelas de oportunidade na terceira parte em alguns dias - fique ligado!

Não se esqueça de se inscrever no

blog : não é difícil para você - estou satisfeito!

E sim, por favor, escreva sobre as deficiências observadas no texto no PM.