Vamos falar sobre o design das vias - para eletrônicos sérios, sua qualidade é muito importante. No início do artigo, destaquei os fatores que afetam a integridade do sinal e, em seguida, mostrei exemplos de cálculo e ajuste da impedância de vias únicas e diferenciais.

Olá pessoal, meu nome é Vyacheslav. Desenvolvo placas de circuito impresso por 5 anos e, durante esse período, não apenas li muitas regras e recomendações para rastreamento, mas também encontrei a fonte e trabalhei com elas.

Nos complexos sistemas de computação que a YADRO está desenvolvendo, os sinais de alta velocidade no caminho do transmissor para o receptor cobrem distâncias significativas, passando por várias placas e fazendo dezenas de transições entre camadas. Sob tais condições, cada via projetada de forma descuidada fará uma pequena contribuição para a degradação do sinal e, como resultado, a interface pode não funcionar.

Integridade do sinal

Vias (daqui em diante p / o, via inglês) são heterogeneidades na linha de transmissão. Como outras heterogeneidades, elas estragam o sinal. Este efeito é fracamente pronunciado em baixas frequências, mas aumenta significativamente com o aumento da frequência. Freqüentemente, os desenvolvedores prestam pouca atenção à estrutura das vias: eles podem ser copiados de um projeto "vizinho", retirado de uma folha de dados ou não especificado em CAD (a configuração padrão).

Antes de usar a estrutura calculada, é necessário entender por que foi feita assim? A repetição cega só pode causar danos.

A integridade do sinal no canal ao passar pelas vias é afetada principalmente pelos seguintes fatores:

- reflexão de sinal devido a mudanças na impedância de onda;

- degradação do sinal devido à capacitância e indutância perdidas;

- reflexões de um trecho não utilizado de semi-plástico ao alternar para a camada interna (doravante denominado stub do inglês via stub)

- diafonia (conversas cruzadas em inglês);

- interferência em barramentos de força.

Vamos considerar com mais detalhes as causas desses efeitos e métodos para sua eliminação.

Fator 1. Impedância de onda p / o

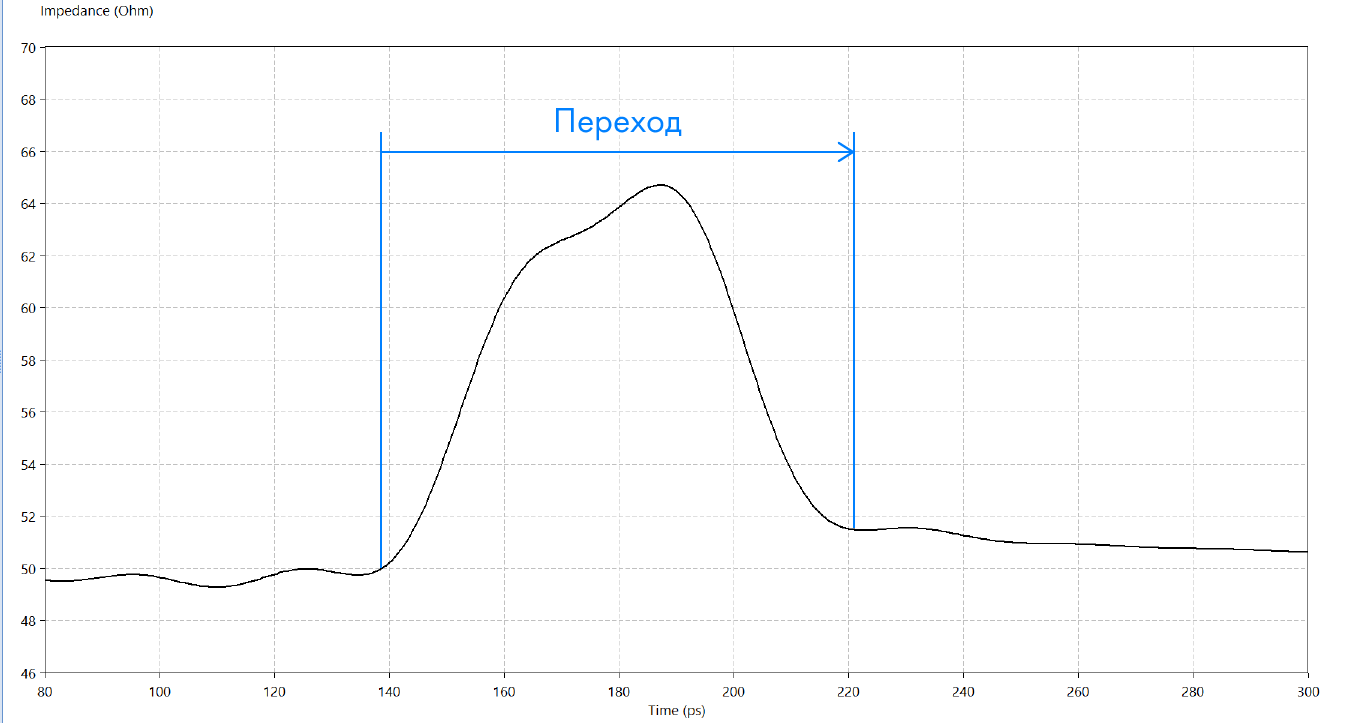

Em uma placa idealmente projetada, a impedância não muda ao longo do caminho, inclusive ao mudar para outra camada. Na realidade, geralmente se parece com isso:

Figura 1. Mudança na impedância de onda após a transição para outra camada.

Figura 1. Mudança na impedância de onda após a transição para outra camada.Quanto melhores as resistências das ondas, menor será o reflexo do sinal. Como influenciar isso?

Considere a estrutura de p / o no quadro [1].

Figura 2. Estrutura p / o no quadro.

Figura 2. Estrutura p / o no quadro.Alterando os elementos de P / O, alteramos a resistência da onda da transição. Nosso objetivo é combinar a impedância da estrutura de transição com a impedância dos condutores para minimizar as reflexões. Vamos considerar como a impedância muda quando os elementos da estrutura de P / O mudam.

Fator 2. Indutância e capacitância espúrias

Os condutores em uma placa de circuito impresso podem ser fabricados com uma resistência a ondas em uma ampla faixa, mas na maioria das vezes é de 50 Ohms. Por um lado, isso se deve à continuidade histórica: a impedância de 50 ohm foi padronizada para cabos coaxiais como um compromisso entre o nível de carga do driver e a perda de energia do sinal. Por outro lado, um condutor de 50 Ohm é fácil de fabricar em uma placa padrão.

Para o desenvolvedor, é importante não tanto o valor específico da resistência das ondas quanto sua constância em toda a linha de transmissão.

Para fazer uma linha de transmissão com um valor fixo de impedância de onda, o desenvolvedor seleciona a largura da faixa e a distância da camada de referência, ou seja, altera a capacidade linear e a indutância da linha de transmissão para um

determinado valor.

Em p / o, o componente indutivo é bastante significativo. Em uma primeira aproximação, devemos, dentro de uma estrutura razoável, minimizar a indutância perdida o máximo possível e, em seguida, alterar os parâmetros de P / O para obter uma

dada capacitância e, portanto, impedância.

Uma diminuição excessiva na capacitância de uma meia onda causará um aumento local na impedância e, como conseqüência, reflexos do sinal.

Fator 3. Via stub

O que acontece quando um sinal passa através de um stub through hole?

Figura 3. Orifício de transição com ponta, ressonância no comprimento de onda.

Figura 3. Orifício de transição com ponta, ressonância no comprimento de onda.No nosso exemplo, o sinal se propaga de cima para baixo a partir da camada superior. Tendo atingido a camada de sinal interna, o sinal é separado: parte se move ao longo do caminho na camada interna e parte continua a se mover pelas vias, depois é refletida na camada inferior. Depois que o sinal refletido atinge a camada interna, ele é separado novamente, a parte se move ao longo do caminho e a parte retorna à fonte.

O sinal refletido será somado com o original e distorcido, o que será expresso no estreitamento da janela no diagrama ocular e um aumento no nível de perda de inserção (Perda de inserção de eng.).

No pior dos casos, o segmento TD será igual a ¼ do comprimento de onda do sinal, então o sinal refletido alcançará o caminho na camada interna com um atraso de metade do período, sobrepondo o sinal original na fase antifásica.

Ao analisar a integridade, recomenda-se considerar a largura de banda com uma largura de 5 frequências Nyquist. Uma boa aproximação seria considerada esboço aceitável, dando uma ressonância em 7 harmônicos e acima [2].

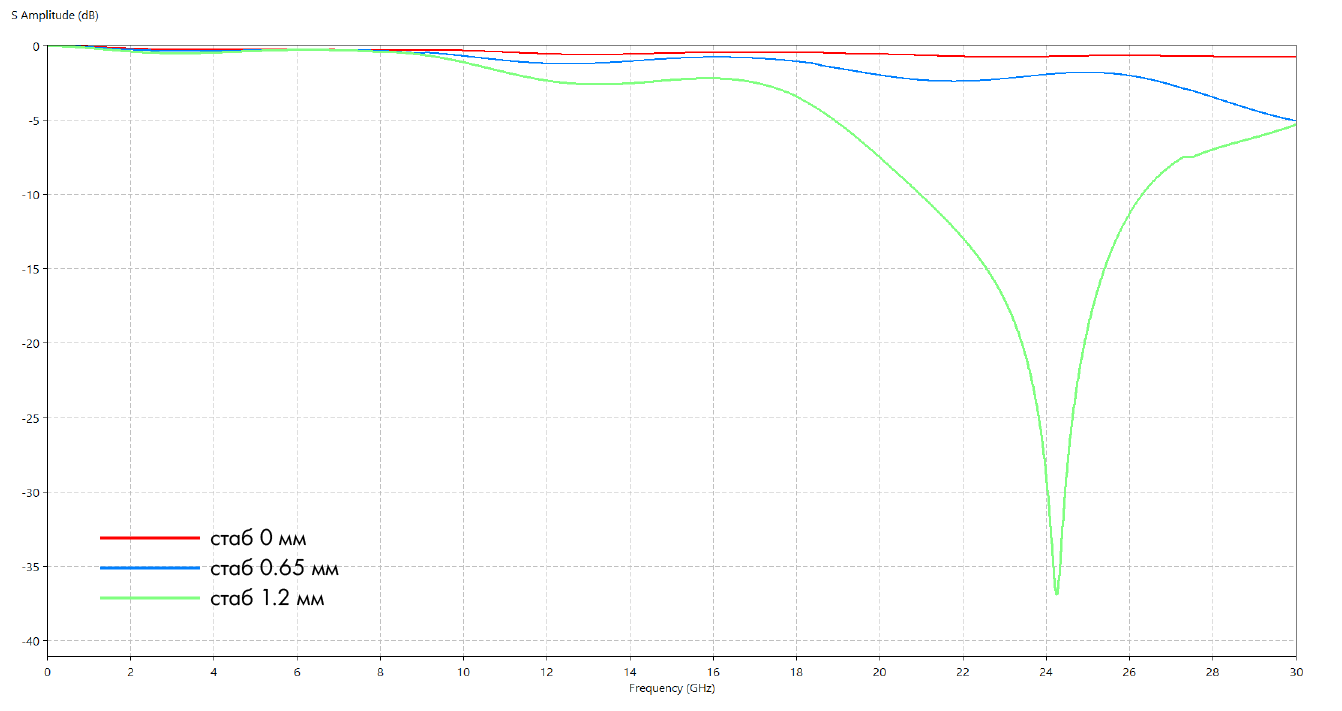

Figura 4. Gráfico do nível de perda de inserção para p / o com tocos 0, 0,65, 1,2 mm.

Figura 4. Gráfico do nível de perda de inserção para p / o com tocos 0, 0,65, 1,2 mm.A Figura 4 mostra uma enorme ressonância em frequências em torno de 24 GHz. Podemos concluir que, se nosso sinal operar com uma frequência de 2-3 GHz, podemos dar ao luxo de não eliminar o esboço, porque dentro de 7 harmônicos "tudo está calmo".

Você pode fazer uma avaliação rápida da criticidade do esboço na

calculadora Polar :

Figura 5. Imagem de polarinstruments.com . Um comprimento de ponta de 2,5 mm é aceitável para sinais com tempos de subida superiores a 500 ps.

Figura 5. Imagem de polarinstruments.com . Um comprimento de ponta de 2,5 mm é aceitável para sinais com tempos de subida superiores a 500 ps.As fórmulas fornecidas em [2] fornecem um resultado um pouco mais preciso. Eles levam em consideração a geometria da peça e permitem calcular a correção da constante dielétrica do dielétrico ao longo do eixo Z.

Você pode eliminar o stub usando a operação “backdrilling” (Backdrilling em inglês) ou usando micro-transições (vias cegas e enterradas em inglês). A escolha depende dos recursos do projeto. A perfuração reversa é mais fácil e mais barata. Após a fabricação da placa, com uma broca de diâmetro maior, a ponta é perfurada a uma profundidade predeterminada. O desenvolvedor deve definir um recuo adicional da topologia na zona de perfuração e também está disponível para o fabricante especificar os requisitos de perfuração na documentação do projeto. Os modernos sistemas CAD suportam essa funcionalidade.

As micro junções destinam-se principalmente a placas de alta densidade (inglês HDI), mas em alguns casos elas podem ser usadas nivelando o alto custo de se recusar a perfurar e reduzindo o número de camadas na placa. Ao projetar placas HDI, lembre-se de algumas coisas:

- cada novo tipo de folha de pagamento aumenta o custo do conselho;

- Para a perfuração a laser, são utilizados pré-impregnados otimizados especiais, cujas propriedades podem variar;

- a metalização de furos cegos aumenta a espessura do cobre nas camadas internas.

É altamente recomendável que a estrutura da placa seja previamente acordada com o fabricante.

Fator 4. Diafonia

Diafonia - transmissão de sinal indesejada de uma linha para a seguinte. Essa transferência ocorre porque dois condutores estreitamente espaçados possuem acoplamento capacitivo e indutivo.

A natureza da diafonia dos condutores de sinal ep / o é um pouco diferente.

O sinal não possui uma camada de referência no n / a, as correntes de retorno fluem ao longo do n / a adjacente, formando um loop grande. Crosstalk de sinais no n / a devido ao componente indutivo.

O maior efeito na minimização da diafonia pode ser alcançado aumentando a distância entre p / o. No entanto, muitas vezes o topologista não tem muito espaço.

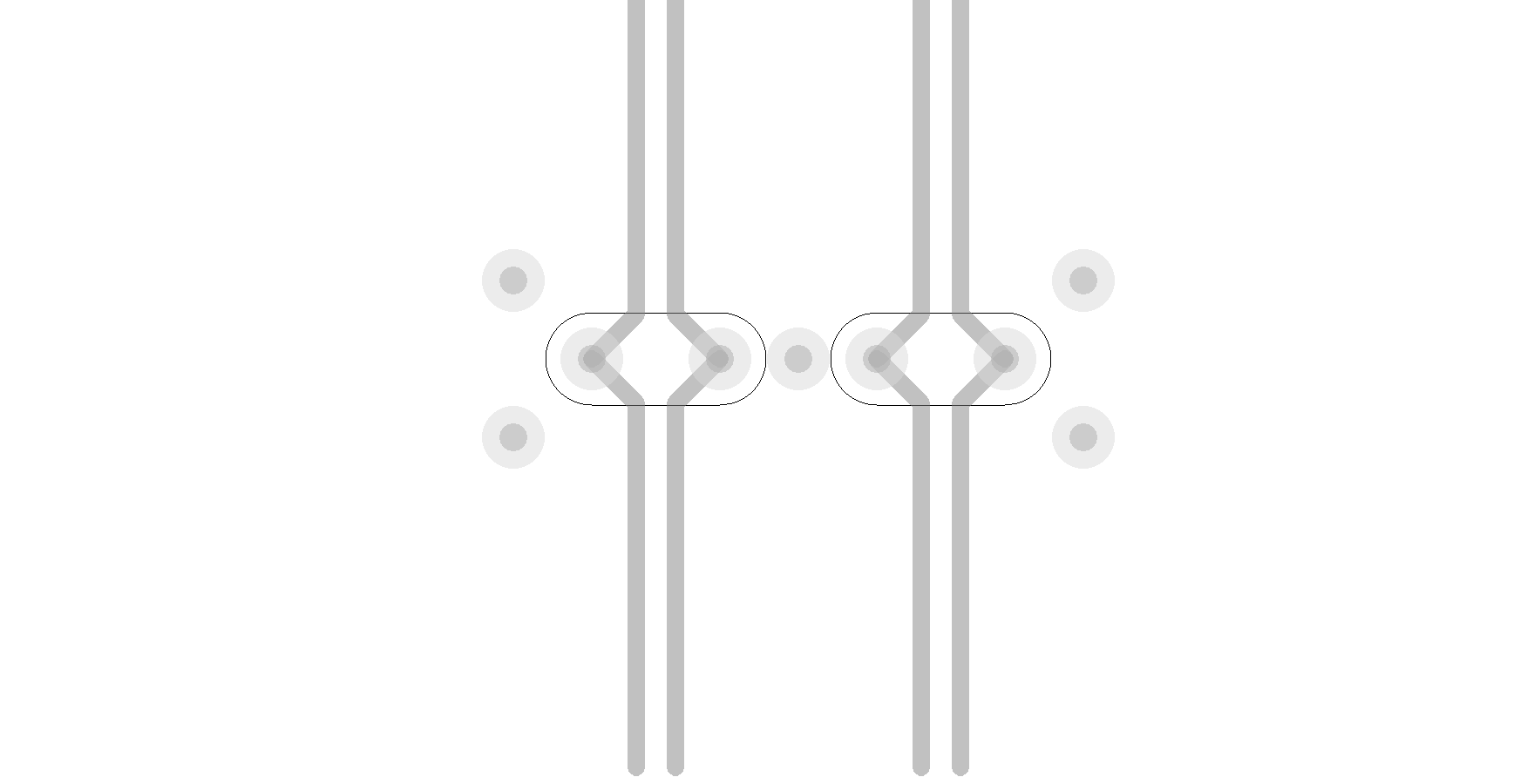

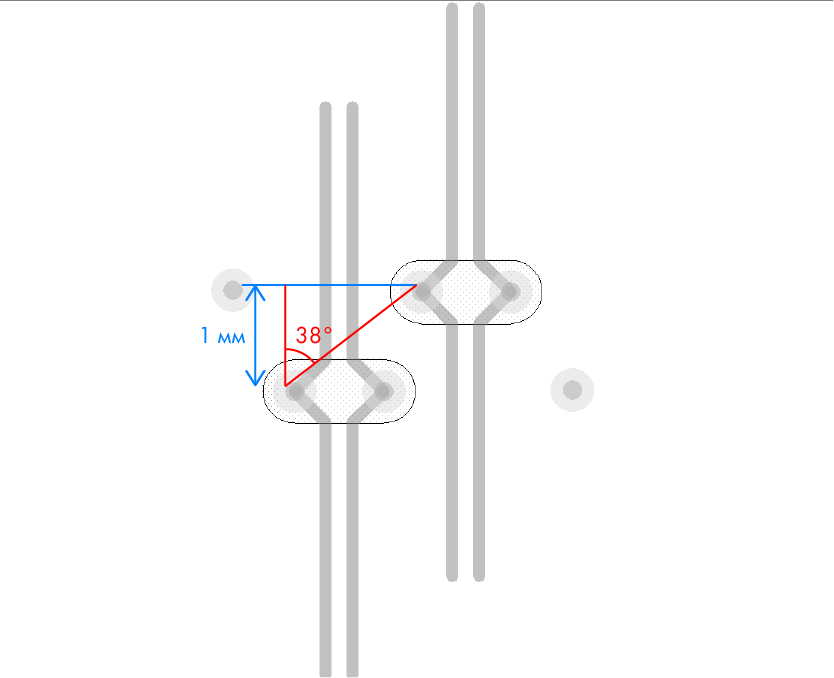

A convergência de p / o no par diferencial não apenas reduz a área ocupada, mas também tem um efeito positivo na imunidade ao ruído [3].

Uma maneira comum de minimizar a interferência entre o sinal adjacente p / o é colocar um p / o de proteção entre eles. Com este método, será necessário conduzir sinais em incrementos de cerca de 2 mm (Figura 6). Se não houver espaço suficiente, você pode usar uma etapa menor com um deslocamento (padrão inglês escalonado), como na Figura 7. Usando a simulação, você pode selecionar o ângulo ideal de deslocamento [4].

Figura 6. Minimizando diafonia usando meio-fio de blindagem.

Figura 6. Minimizando diafonia usando meio-fio de blindagem. Figura 7. Minimizando diafonia usando um deslocamento diagonal do “tabuleiro de damas”.

Figura 7. Minimizando diafonia usando um deslocamento diagonal do “tabuleiro de damas”.A diafonia também pode ser reduzida por métodos exóticos, por exemplo, por um longo esboço (devido ao deslocamento da balança indutivo-capacitiva p / o) [5]. Além disso, a interferência pode ser reduzida na fase de projeto do alojamento do microcircuito [6].

Fator 5. Interferência do Barramento de Potência

Além dos circuitos de sinal adjacentes, a qualidade do sinal pode ser afetada pela interferência de camadas internas.

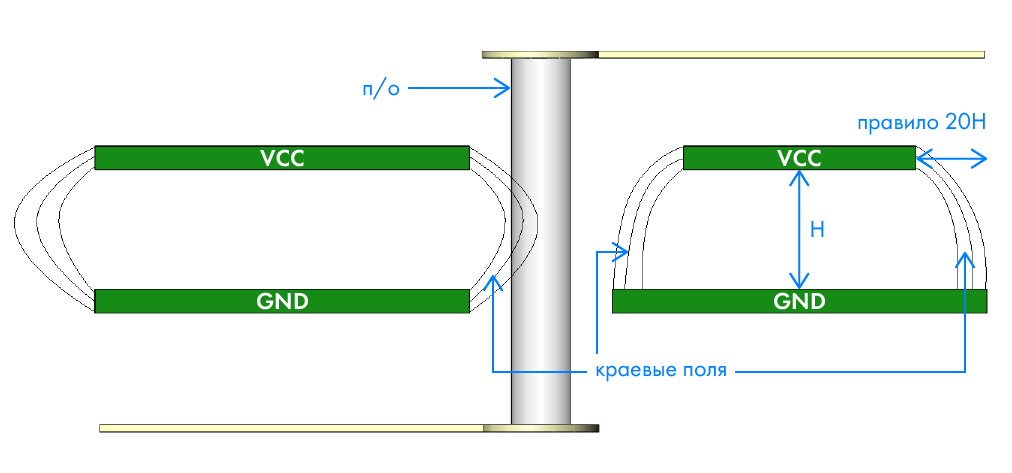

Grandes correntes podem fluir através dos locais de teste de alimentos. Devido ao aumento da indutância nas bordas dos polígonos, as correntes fluidas formam campos de borda (campos de franjas inglesas) ao longo de todos os limites do polígono, incluindo recortes. Os campos de borda são uma fonte de radiação eletromagnética (emissão emitida pelo Edge) no espaço. Para reduzir a emissão de radiação eletromagnética, é aplicada a regra 20H (Figura 8), que consiste em restringir a área de fornecimento de energia em relação à área do solo.

Figura 8. Campos de borda e a regra 20H.

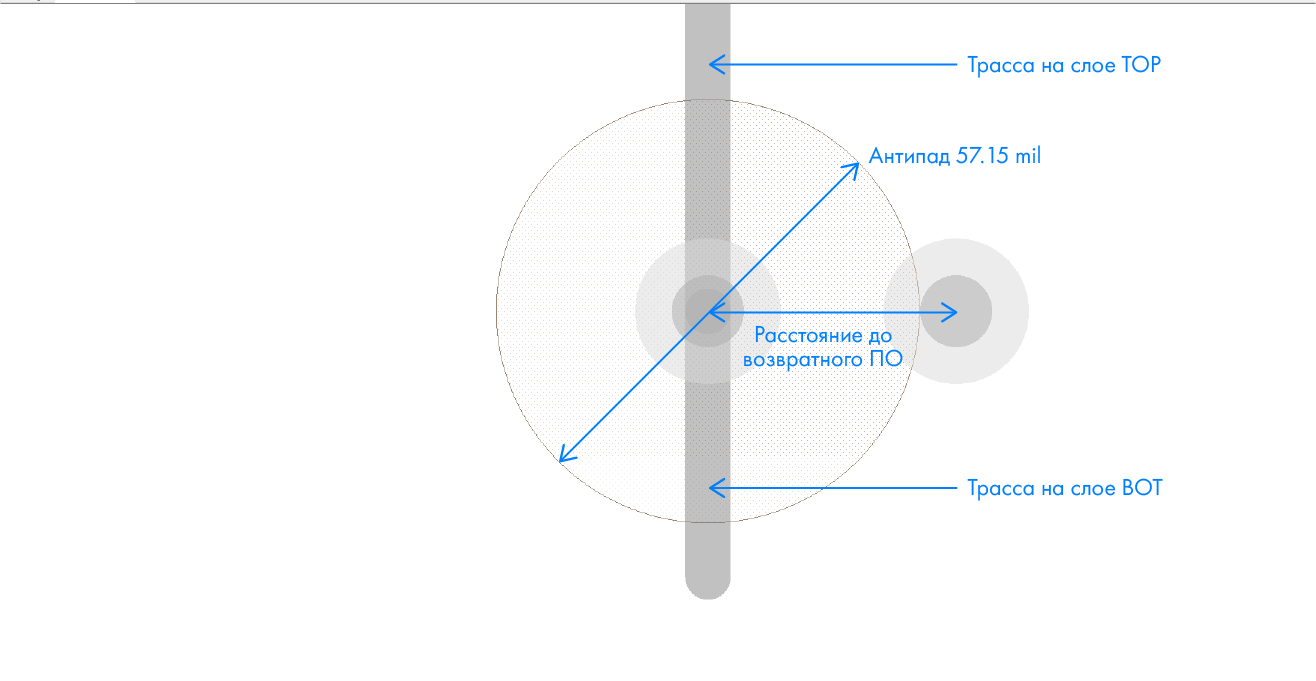

Figura 8. Campos de borda e a regra 20H.Para proteger o P / O da interferência, se possível, é necessário aumentar o antipad nas faixas de alimentos. A regra 20H para p / o é difícil de fornecer, e desnecessariamente, um anti-queda com um diâmetro de cerca de 2 mm é geralmente recomendado (Figura 9).

Figura 9. Anti-queda aprimorada nas camadas de alimentos

Figura 9. Anti-queda aprimorada nas camadas de alimentosCálculo da impedância de vias únicas

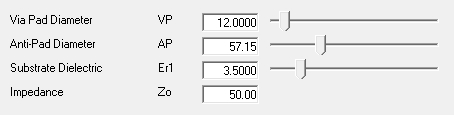

Com base no conhecimento sobre o efeito dos elementos de P / O na impedância, podemos projetar nosso P / O ideal. Um ótimo começo é calcular a impedância na calculadora.

Engenheiros de

design de PCBs como calculadoras como o

Saturn PCB Design Toolkit e o

Polar Instruments Si9000e . Ambos permitem calcular rapidamente a impedância de uma única peça.

O resultado obtido nessas calculadoras é muito diferente um do outro. Isso se deve ao fato de essas ferramentas terem uma abordagem diferente.

Polar calcula a impedância em um plano bidimensional, onde a linha de fonte de alimentação cruza a faixa de potência. Fórmulas de cálculo não são fornecidas. Foi estabelecido experimentalmente que o cálculo é feito de acordo com a fórmula de impedância do cabo coaxial:

Figura 10. Imagem de polarinstruments.com

Figura 10. Imagem de polarinstruments.comA ilustração mostra um valor bastante baixo da constante dielétrica Er1, em comparação com o padrão. Isto é devido à heterogeneidade da estrutura dielétrica: consiste em resina (Er 3.2) e filamentos de fibra de vidro (Er 6.1) e, portanto, possui uma constante dielétrica média de cerca de 4,1. Este valor pode variar bastante localmente. Assim, a resina prevalece perto da subsuperfície, portanto, a constante dielétrica é recalculada para baixo [7].

O PCB de Saturno calcula a impedância pela fórmula:

Quando o comprimento p / o muda, os valores de indutância e capacitância mudam desproporcionalmente, a impedância muda. Impedância exatamente do mesmo comprimento de 1,6 mm, o PCB Saturno calcula 128 Ohm! (Figura 11)

Figura 11. Cálculo do software no Saturn PCB Design Toolkit.

Figura 11. Cálculo do software no Saturn PCB Design Toolkit.Surge imediatamente a pergunta: em quem acreditar?

Simulamos em um solucionador tridimensional de campos eletromagnéticos (inglês 3D Solver) como ele ficará em uma placa real de 8 camadas com 1,6 mm de espessura (Figura 12)

Figura 12. A estrutura da transição entre as camadas com um furo para a corrente de retorno.

Figura 12. A estrutura da transição entre as camadas com um furo para a corrente de retorno.No nosso caso, a impedância é de cerca de 70 ohms. Ao aproximar o retorno p / o, você pode obter uma diminuição de outros 5 ohms. Tendo “tocado” com o tamanho do antipad, é possível ajustar com precisão a impedância ao valor-alvo (Figura 13).

Figura 13. A impedância do circuito com meia onda no diagrama de tempo.

Figura 13. A impedância do circuito com meia onda no diagrama de tempo.No domínio da frequência, os "melhores" parâmetros são expressos em um valor mais baixo do coeficiente de reflexão da entrada (Figura 14).

Figura 14. Parâmetros de p / o único no domínio da frequência.

Figura 14. Parâmetros de p / o único no domínio da frequência.Cálculo Polar estava mais próximo do resultado. Talvez, para obter um resultado adequado no PCB de Saturno, sejam necessárias correções. Se alguém tiver uma experiência positiva no cálculo da impedância em Saturno, compartilhe nos comentários!

Cálculo da impedância de vias diferenciais

O cálculo do diferencial de P / O é semelhante ao único, exceto que agora não temos uma calculadora: as ferramentas acima não consideram o diferencial de P / O. Além disso, agora podemos alterar adicionalmente a etapa de P / O no diferencial. casal.

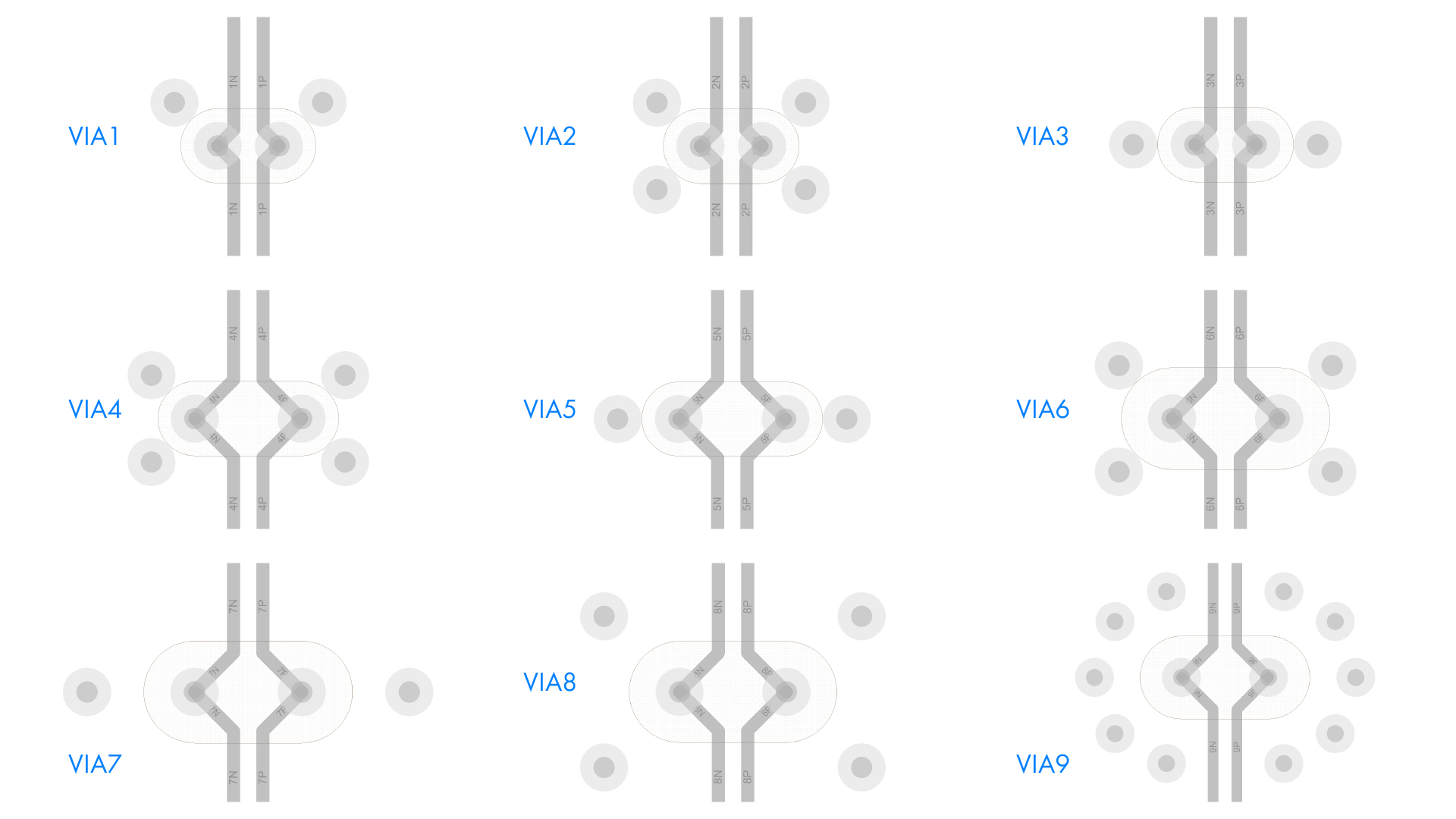

Pegue a mesma estrutura: uma placa de 8 camadas com 1,6 mm de espessura. Considere 9 configurações do software (Figura 15).

Os primeiros 3 p / o têm folgas de 0,125 mm e diferem apenas na localização dos furos para a corrente de retorno. Todos os P / O com 4 em diante têm um passo de 1 mm. O P / o de 6 em diante tem um anti-gota aumentado (0,250 mm) e se distingue pelo recuo dos furos para a corrente de retorno.

Figura 15. vias.

Figura 15. vias.Considere o gráfico de impedância (Figura 16).

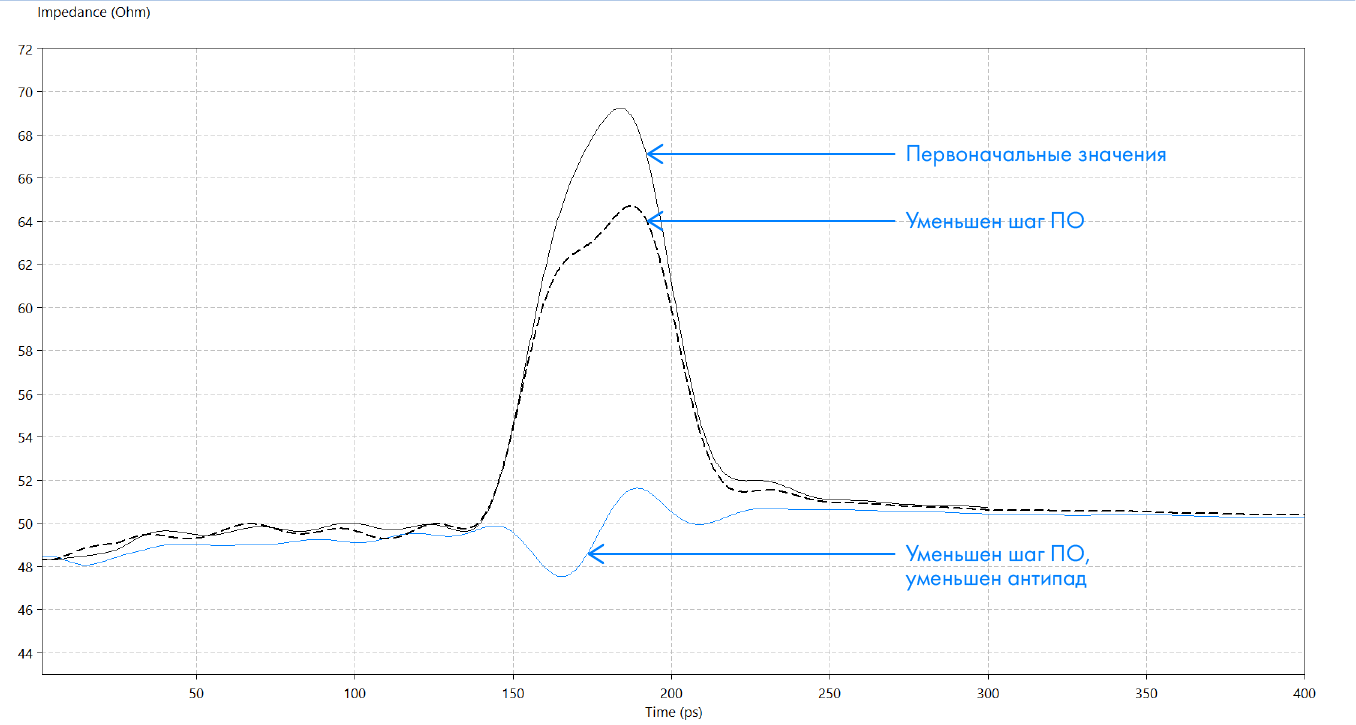

Figura 16. Impedância p / o no domínio do tempo.

Figura 16. Impedância p / o no domínio do tempo.No gráfico, a “corcunda” é claramente visível, o que corresponde à seção vertical da meia concha - o “vidro” (via inglesa).

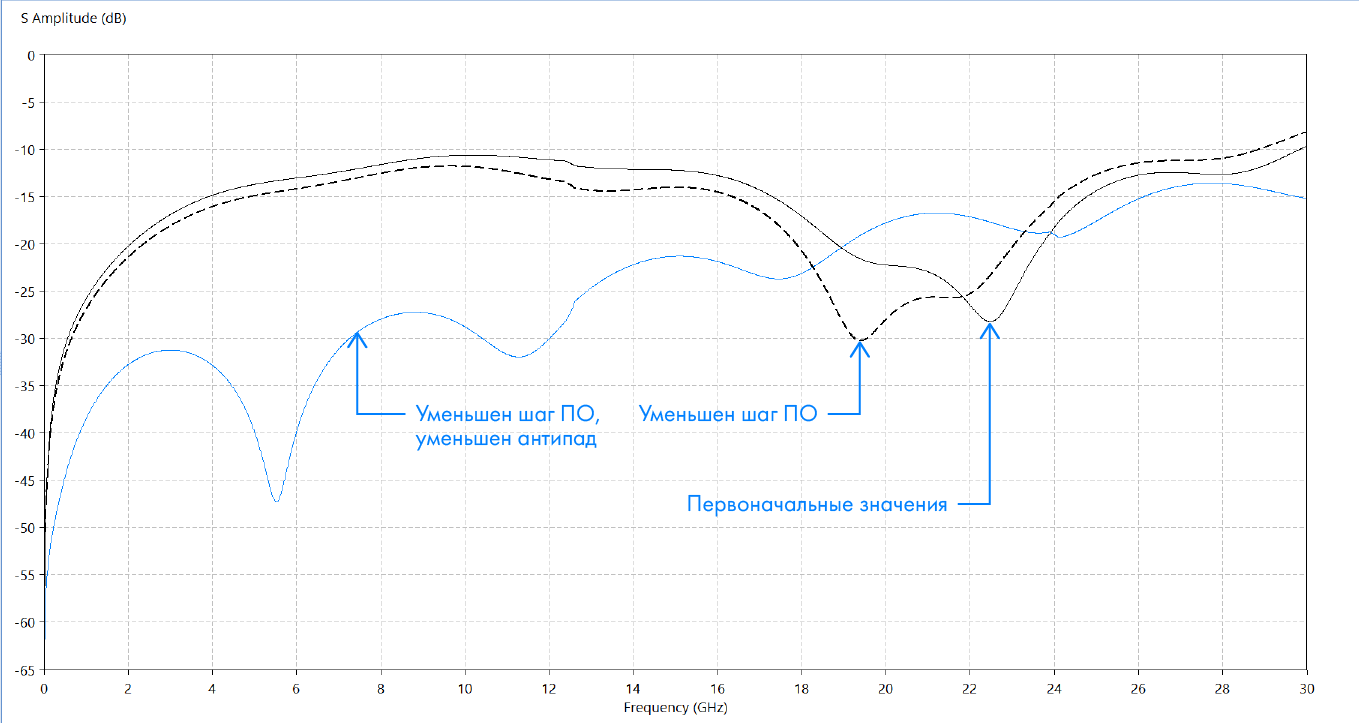

Tendo examinado a dependência da frequência do coeficiente de reflexão VIA1-3 (Figura 17), vemos que, apesar do bom desempenho na frequência alvo de 6 GHz, há ressonância nas frequências mais baixas. É preferível melhorar a via7-9 e, se não der certo, a via4-5 para reduzir o "hump" devido à mudança dos gráficos para a direita.

Figura 17. O coeficiente de reflexão da entrada p / o.

Figura 17. O coeficiente de reflexão da entrada p / o.Reduza a anti-gota no VIA9 para obter intervalos de 0,125 mm. Para o VIA4, reduzimos o passo de P / O para 0,75 mm e consideramos o resultado obtido (Figura 18).

Figura 18. Comparação da impedância do p / o modificado.

Figura 18. Comparação da impedância do p / o modificado.No domínio da frequência, é visível um deslocamento do gráfico do coeficiente de reflexão da entrada para a direita (Figura 19).

Figura 19. Comparação do coeficiente de reflexão do software modificado.

Figura 19. Comparação do coeficiente de reflexão do software modificado.Recomendações finais

Vias em placas de circuito impresso é uma estrutura complexa e heterogênea. Para o cálculo correto dos parâmetros, são necessários solucionadores 3D caros, competências e custos de tempo significativos.

Se não for possível evitar o uso de transições de sinais críticos para outras camadas, é necessário, antes de tudo, avaliar o grau de influência das inomogeneidades resultantes na integridade dos sinais. Se a heterogeneidade for eletricamente curta (o tempo de atraso é menor que 1/6 da frente), o esboço ressoa em frequências fora da banda passante - não há sentido em perder tempo e dinheiro com a otimização.

Em uma primeira aproximação, é conveniente usar estruturas prontas de folhas de dados ou quadros anteriores, mas lembre-se dos recursos do projeto atual.

As calculadoras permitem avaliar rapidamente os parâmetros do software, mas eles usam modelos altamente simplificados que afetam negativamente o resultado.

Referências- Chin, T. Pares diferenciais: quatro coisas que você precisa saber sobre vias. Recuperado da Comunidade TI E2E: https://e2e.ti.com/blogs_/b/analogwire/archive/2015/06/10/differential-pairs-four-things-you-need-to-know-about-vias#

- Simonovich, B. Via Stubs Demystified. Obtido em Design Notes de Bert Simonovich: https://blog.lamsimenterprises.com/2017/03/08/via-stubs-demystified/

- Desmistificando Vias no Design de PCB de Alta Velocidade. Recuperado da Keysight Technology: https://www.keysight.com

- K. Aihara, J. Buan, A. Nagao, T. Takada e CC Huang, "Minimizando diafonia diferencial de vias para transmissão de dados em alta velocidade", em Proc. 14º Eleito. Executar. Elétron Pacotes e sistemas, Portland, OR, outubro 2014.

- CM Nieh e J. Park, "Cancelamento de diafonia de extremidade remota usando Via Stub para canal de memória DDR4", em Proc. 63ª Conferência de Componentes e Tecnologia Eletrônica, Las Vegas, NV, maio de 2013, pp. 2035-2040.

- H. Kanno, H. Ogura e K. Takahashi, “Pacote de polímeros de cristal líquido montável em superfície com indutância de fio de compensação de transição vertical até a faixa V”, em IEEE MTT-S Int. Microondas Symp. Dig., Filadélfia, PA, junho de 2003, pp. 1159-1162.

- Via Cálculo de impedância Pad / Anti-Pad. Obtido em instrumentos Polar https://www.polarinstruments.com/support/si/AP8178.html