Atualmente, há mais de um tipo de memória, cada um dos quais é usado para uma tarefa específica. Eles lidam muito bem com suas tarefas, mas existem várias deficiências que não tornam possível chamar universalmente nenhuma dessas opções de memória. Se adicionarmos aqui o problema do crescimento colossal de dados em todo o mundo e a sede da humanidade pela conservação de energia, será necessário criar algo completamente novo. Hoje nos encontraremos com um estudo no qual os cientistas introduziram um novo tipo de memória que combina as vantagens da memória flash e DRAM. Quais “vantagens” essa inovação possui, quais tecnologias foram usadas para criá-la e quais são as perspectivas? Aprendemos sobre isso no relatório do grupo de pesquisa. Vamos lá

Base de estudo

Existem muitos tipos de memória, e todos eles foram criados para uma tarefa específica: SRAM (memória estática de acesso aleatório) para cache, DRAM (memória dinâmica de acesso aleatório) para memória ativa, memória flash para armazenamento de dados etc. No entanto, como esperado, cada um dos tipos de memória acima tem suas próprias falhas pessoais.

Por exemplo, memória flash, que é uma coleção de transistores MOS (semicondutor de óxido de metal) com uma porta flutuante (FG) para armazenar carga. Os dados são apresentados em uma modalidade como a quantidade de carga mantida no FG, que é isolada por camadas de óxido.

A desvantagem, segundo os cientistas, é que, para gravar e apagar, é necessária uma tensão suficientemente alta para o controle por um obturador de controle (CG), geralmente cerca de ± 20 V

2 . Esse processo é lento e o mecanismo de falha induzido por uma oscilação de energia leva a uma redução na vida útil do dispositivo.

Apesar disso, há uma vantagem impressionante - os dados são lidos verificando a condutividade do canal, o que requer muito pouca voltagem. Devido a isso, os dados permanecem intactos, o que é chamado de leitura não destrutiva.

A DRAM, por sua vez, é muito mais rápida que a memória flash, e é por isso que é usada para processos de computação ativos, por assim dizer. A desvantagem da DRAM é que os dados são perdidos das células quando são lidos. Além disso, ocorrem vazamentos de carga nos capacitores usados para armazenar dados.

SRAM também é um tipo de memória bastante rápido e os dados não são tão perdidos quanto na DRAM. No entanto, como regra, são utilizados 6 transistores por célula, ou seja, você precisa de muita área no chip.

Tendo apresentado as deficiências descritas acima dos tipos clássicos de memória, os cientistas enfatizam a importância de encontrar uma opção alternativa ou híbrida que estará livre de tais problemas, combinando todas as vantagens de seus antecessores.

Neste trabalho, os pesquisadores apresentam à atenção deles a visão de um novo tipo de memória - um novo dispositivo de memória de baixa voltagem, semicondutor, com base em carga e não volátil, de forma compacta, operando em temperatura ambiente. Os pesquisadores apelidaram seus filhos de "memória universal" (simples, mas de bom gosto).

O dispositivo é uma memória com um portão flutuante, criado com base nas heteroestruturas InAs / AlSb / GaSb, em que o InAs é usado como um portão flutuante e como um canal sem transições.

Os cientistas forneceram resultados de simulação e testes reais para um protótipo de célula única.

Resultados da pesquisa

Imagem Nº 1

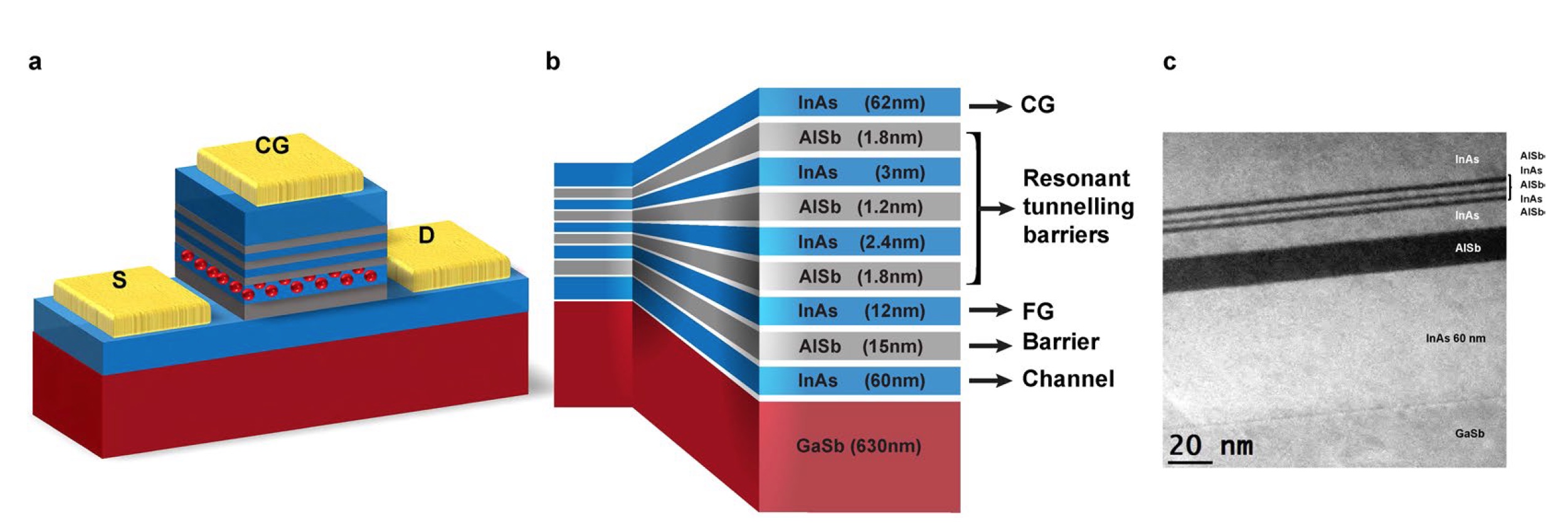

Imagem Nº 1A imagem acima mostra uma vista esquemática de um dispositivo e uma imagem de um PREM (microscópio eletrônico de transmissão).

Como no caso da memória flash, neste dispositivo a carga é armazenada em FG, mas ao mesmo tempo não existem barreiras de óxido. Em vez disso, foi utilizada uma mudança na banda de condução na chamada família de semicondutores 6.1-Å. Ou seja, o dispositivo subjacente à célula de memória é mais como um transistor de alta mobilidade eletrônica (HEMT) do que um transistor MOS. InAs forma um canal que não contém transições. No entanto, o n-doping foi utilizado para compensar o doping não intencional de fundo e manter as vagas de Ga no GaSb subjacente. Ambas as tarefas formam naturalmente camadas do tipo p.

junção pn * é a área de contato de dois semicondutores com diferentes tipos de condutividade - p (orifício) en (eletrônico).

Imagem No. 2

Imagem No. 2O gráfico

2a mostra o alinhamento simulado das bandas de energia, bem como a densidade de elétrons e buracos nas camadas na ausência de viés. Os dados teóricos, juntamente com a simulação, demonstram que a banda de condução InAs está abaixo da banda de valência GaSb na interface InAs e GaSb. E isso leva à transferência de elétrons da camada GaSb para a camada InAs, após o que os furos permanecem no GaSb.

O buraco * é uma ligação de valência não preenchida, manifestando-se como uma carga positiva igual à carga de um elétron.

Os elétrons / orifícios acumulados são visíveis na interface entre InAs e GaSb, mas os elétrons no canal InAs não estão conectados à interface InAs / GaSb e sua densidade é observada em todos os InAs. A condutividade de todo o canal é dominada por elétrons nos InAs, que terão maior mobilidade e maior densidade do que os orifícios no GaSb.

O FG interno da camada InAs é isolado do canal InAs por uma barreira AlSb (15 nm). Ao mesmo tempo,

poços quânticos duplos

* InAs e três barreiras AlSb atuam como uma barreira de tunelamento ressonante entre FG e CG InAs com n-doping.

Poço quântico * - limita o movimento de partículas na dimensão bidimensional (em vez de tridimensional), por causa da qual elas só podem se mover em uma camada plana.

Portanto, no dispositivo em estudo, os elétrons armazenados no FG da camada InAs são isolados por uma lacuna anomalamente grande na banda de condução com AlSb. Isso significa que você pode obter um sistema de limitação de carga, que terá um tempo de armazenamento em temperatura ambiente igual a 1014 anos.

O aspecto mais importante da operação do dispositivo em estudo é o fato de que dois poços quânticos (QW1 e QW2) na barreira de tunelamento tripla ressonante têm espessuras diferentes, ou seja, ocorrem estados limitados com energias diferentes (

2a ). Como o QW2 é mais fino que o QW1, o único nível de energia disponível para elétrons no QW2 tem energia mais alta que o equivalente no QW1. Além disso, o estado no QW1 possui uma energia significativamente maior do que o estado na região vizinha do CG. Isso evita o tunelamento direto de elétrons entre CG e FG, e a barreira de transferência de elétrons de CG para FG (ou vice-versa) é determinada por um deslocamento da banda de condução InAs / AlSb em 2,1 eV, ou seja, a carga não flui para / de FG.

Os estados de terra e de excitação primária no portão flutuante (FG) estão localizados bem abaixo dos estados de energia em ambos os QWs. Portanto, quando nenhuma tensão é aplicada, os elétrons são bloqueados dentro do FG, ou seja, a barreira tripla de tunelamento ressonante torna-se insuperável para elétrons de / para FG. Assim, a não volatilidade é alcançada.

Se uma tensão insignificante for aplicada à porta de controle (CG), é possível ajustar o acoplamento dos estados de energia dentro da barreira de tunelamento ressonante, o que permitirá que os elétrons passem livremente (

2b ) ou (

2c ) da porta flutuante.

Durante os experimentos, todas as operações de leitura, gravação e exclusão foram realizadas em várias células (tamanho do obturador 10 x 10 μm) em uma caixa escura protegida contra eletrostática à temperatura ambiente. Todas as operações, incluindo gravação e apagamento, foram realizadas em um deslocamento de ≤ 2,6 V, que é aproximadamente uma ordem de magnitude inferior ao necessário para a operação completa com uma célula de memória flash, enfatizam os pesquisadores. O apagamento foi realizado deslocando a porta de controle (V

E CG-S ) em +2,5 ou +2,6 V entre o CG e a fonte, o que levou ao estado "0".

A Figura

2b mostra um alinhamento simulado de bandas de energia obtidas com uma tensão de apagamento de +2,6 V. Nessas circunstâncias, o nível calculado de energia eletrônica em QW1 é mais baixo que o nível em QW2, enquanto ambos estão abaixo do primeiro estado excitado e estão próximos do nível de energia estado fundamental no FG. O resultado é um apagamento, isto é, um fluxo de elétrons de FG para CG seguido de depleção de FG. O mesmo princípio funciona para a operação de gravação: V

W CG-S = -V

E CG-S para aumentar a carga em FG (estado “1”).

O gráfico

2c é uma zona de energia simulada quando o deslocamento da porta de controle é usado para o registro de dados: V

W CG-S = -2,6 V. Nesse caso, os níveis de energia em QW1 e QW2 praticamente coincidem, o que leva a um forte acoplamento desses estados, tunelamento e fluxo ressonantes. elétrons do CG ao FG.

Devido ao acoplamento capacitivo, a condutividade do canal depende da quantidade de carga armazenada no FG; portanto, os dados são lidos medindo a corrente da porta-fonte em uma tensão fixa da porta-fonte.

Aumento da cobrança em FG, ou seja, o estado "1" reduz a carga no canal, o que leva a uma diminuição de sua condutividade. No caso do estado "0", ocorre o processo inverso. Os dados podem ser lidos sem viés para o CG, mas a voltagem é necessária para a seleção individual de dispositivos em uma matriz de células. Além disso, a tensão deve gerar um campo elétrico através da barreira de tunelamento ressonante, o que permitirá transferir a carga de / para FG. Para realizar essas tarefas, apenas ~ 2,5 V. é necessário.

Recursos de memória universal

Durante os testes práticos, a leitura foi realizada com deslocamento de zero por CG e V

SD = 1,0 V. No entanto, segundo os cientistas, foi possível aplicar menos tensão para uma leitura bem-sucedida.

Imagem No. 3

Imagem No. 3A Figura

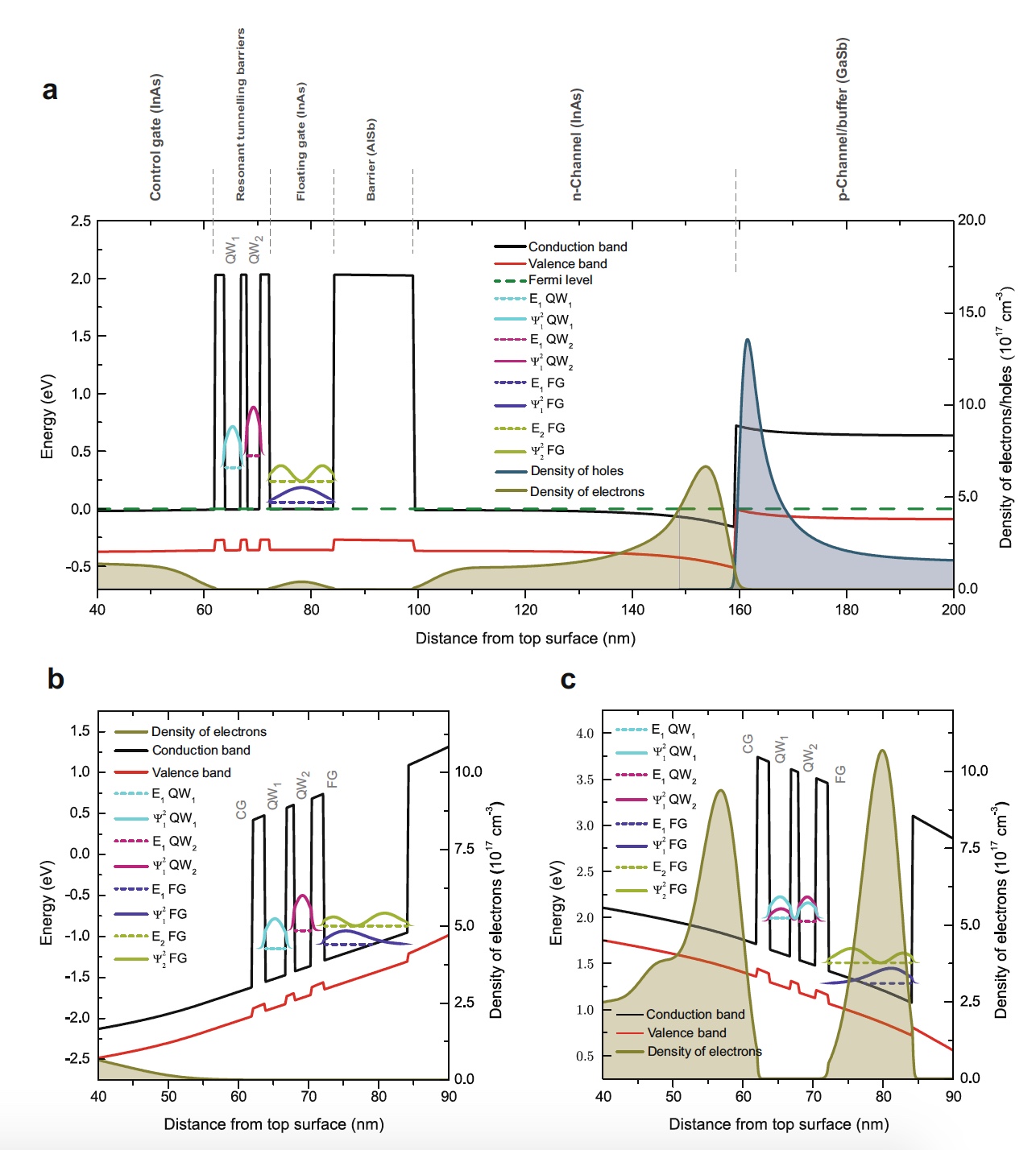

3a mostra o processo de apagar-ler-escrever-ler. A principal característica da sequência é a operação de leitura após cada etapa de exclusão ou gravação.

A Figura

3b mostra uma sequência mais complicada na qual, após cada operação de apagar e gravar, não há uma operação de leitura, mas várias. Dessa maneira, os pesquisadores demonstram que a operação de leitura é não destrutiva.

Entre o estado "0" e "1", há uma clara diferença em todas as seqüências. No entanto, em

3b há sinais de uma mudança ascendente simétrica no I

SD à medida que o número de operações aumenta. Embora a razão para esse comportamento não seja clara, os cientistas pretendem explorar esse aspecto em outros trabalhos. Mas em

3a isso não é observado, uma vez que a tensão para apagar / gravar é um pouco menor.

Depois de várias centenas de operações de gravação e apagamento, bem como muitas operações de leitura durante vários testes práticos, os cientistas não encontraram nenhum sinal de dano ao dispositivo.

Uma característica importante de todos os tipos de memória, baseados no armazenamento de carga, é a energia de comutação determinada pela energia de carga do capacitor.

A semelhança dos princípios fundamentais da tecnologia de memória flash e a memória universal em estudo sugere uma comparação desses dois tipos de memória. Se assumirmos que os dois dispositivos desses dois tipos têm a mesma capacidade e o mesmo tamanho de obturador, a energia de comutação da memória universal será 64 vezes menor que a da memória flash. Esses números surpreendentes também mostram a superioridade da memória universal sobre a DRAM.

De acordo com estimativas teóricas, a capacitância CG-FG é da ordem de 10

-12 F para um dispositivo medindo 10 x 10 μm, e a energia de comutação é de aproximadamente 2 x

10-12 J. A redução do tamanho físico do dispositivo reduz drasticamente a energia de comutação para 10

-17 J para um dispositivo de tamanho 20 nm, e isso é 100 vezes menor que para DRAM e 1000 vezes menor que para memória flash. E isso, de acordo com as afirmações ousadas dos pesquisadores, são características muito únicas.

A imagem

3c mostra algumas operações de apagar e gravar de

3b , onde as diferenças entre o estado "0" e "1" são visíveis: medições consecutivas de leitura após o apagamento fornecem I

SD ligeiramente menor para o estado "0". A situação oposta é observada com medições sequenciais de leitura após a gravação, ou melhor, o I

SD é um pouco maior.

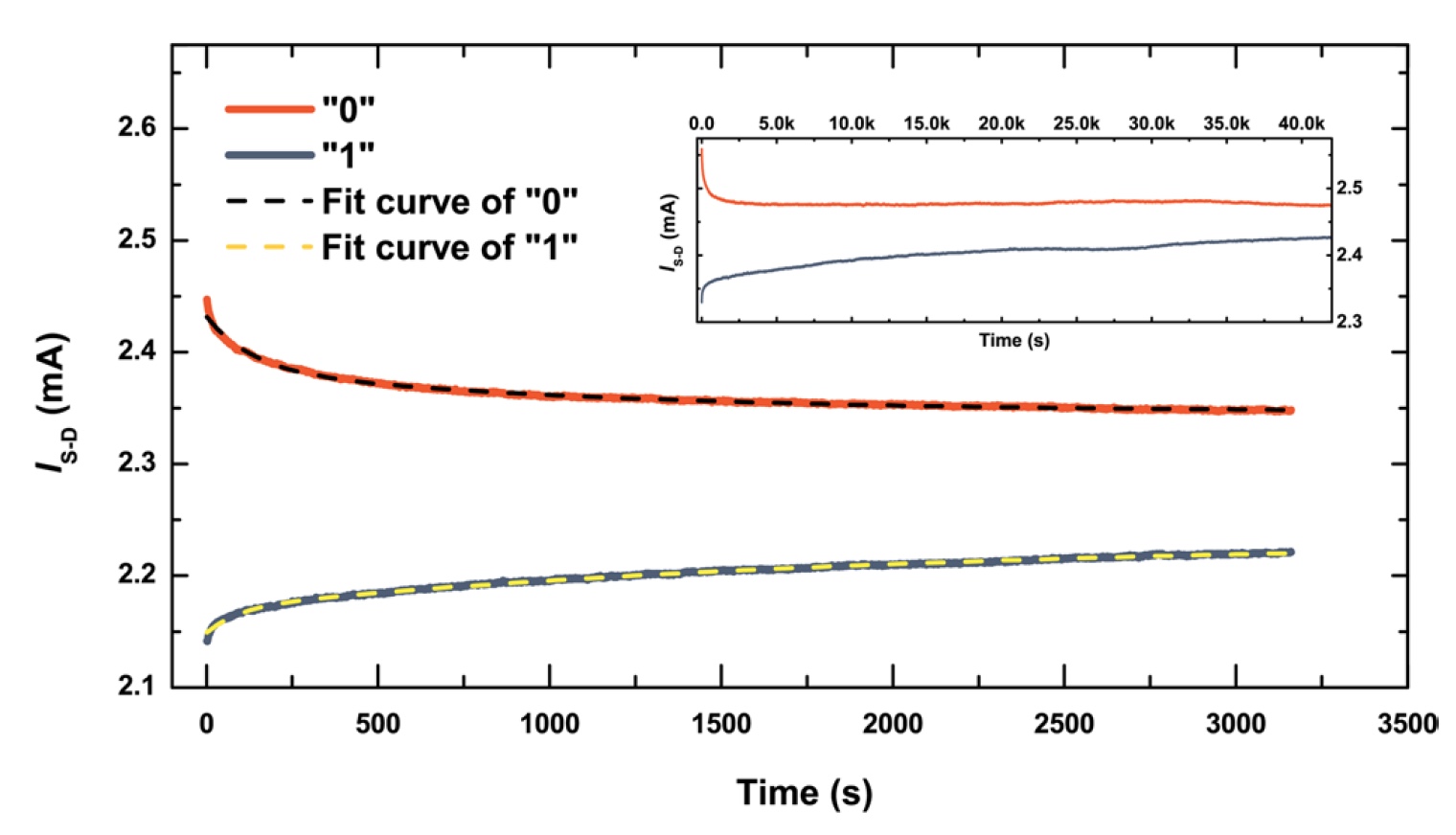

Os cientistas atribuem esse efeito à variabilidade (volatilidade) dos dados. Para estudar isso, os cientistas realizaram uma sequência de operações de leitura por um longo período de tempo para cada estado de memória (imagem nº 4).

Imagem No. 4

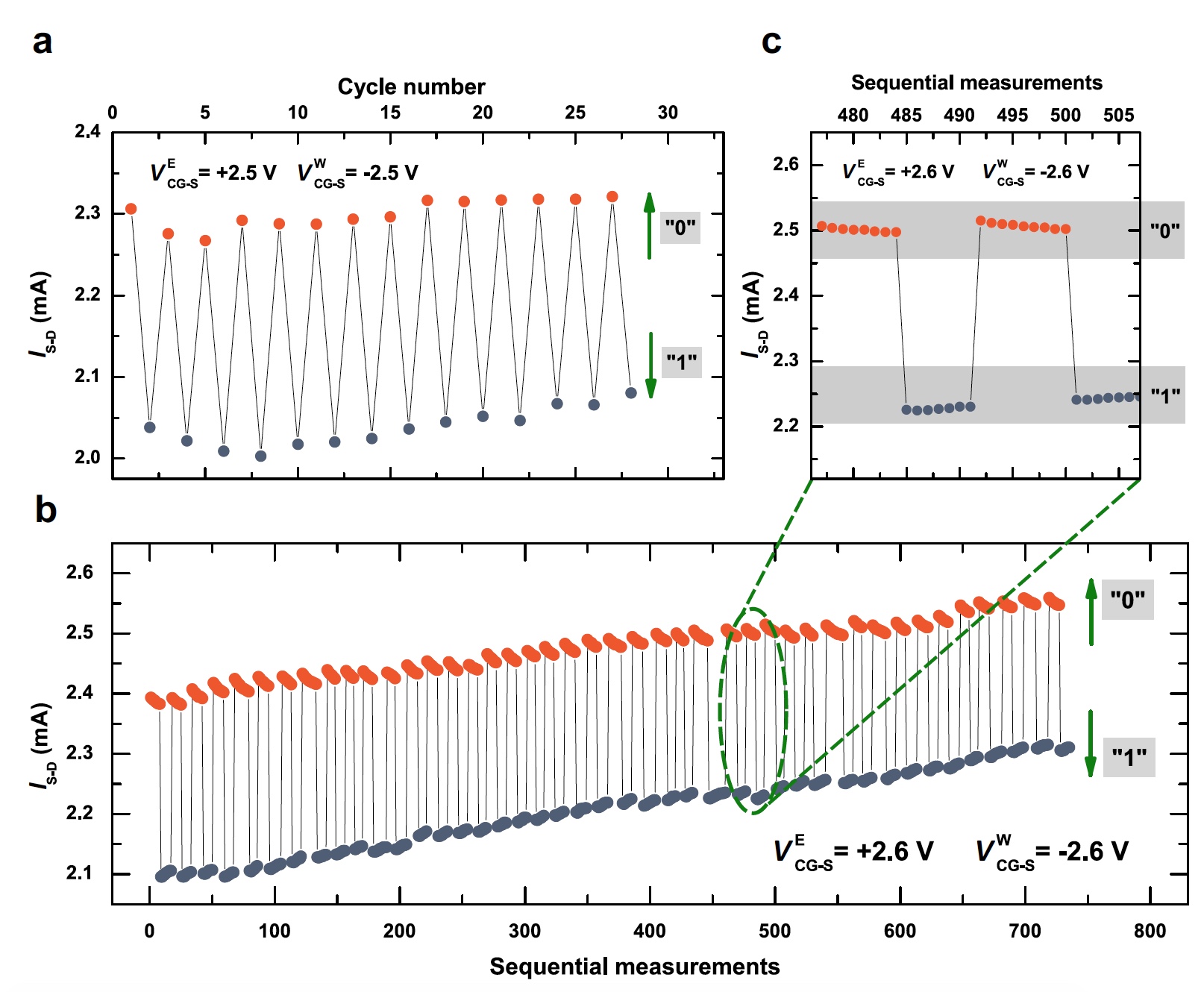

Imagem No. 4Ambos os estados "0" e "1" mostraram uma rápida deterioração inicial, consistente com o que é visto por

3s . Mas, depois disso, ocorrem mudanças muito mais lentas, de modo que, durante todo o tempo de observação, os estados correspondentes "0" e "1" são claramente distinguíveis.

Também foi realizado outro experimento (inserção na imagem nº 4), que mostra a saturação limitante da atenuação exponencial e os estados distinguíveis “0” e “1” no tempo.

A existência de dupla atenuação exponencial significa que vários mecanismos estão subjacentes à degradação de estados de uma só vez. Entre as opções possíveis, os cientistas distinguem o tunelamento através de estados defeituosos nas barreiras de AlSb, a excitação térmica de elétrons através da estreita faixa de banda InAs e a recombinação com orifícios gerados termicamente.

A avaliação da capacitância do dispositivo e da tensão aplicada para gravação / apagamento indica que aproximadamente 107 elétrons são transferidos de / para o portão flutuante durante a operação de gravação e apagamento. Isso é bastante, mas praticamente nenhuma influência negativa é observada.

Para um conhecimento mais detalhado das nuances do estudo, recomendo que você analise o

relatório do grupo de pesquisa .

Epílogo

Os cientistas conseguiram não apenas desenvolver um novo tipo de memória, mas também realizar primeiros testes práticos bem-sucedidos de um dispositivo não volátil e baseado em carga, de tamanho compacto à temperatura ambiente. Os cientistas também conseguiram combinar comutação de não-volatilidade e baixa voltagem pelas propriedades da mecânica quântica de uma barreira de tunelamento ressonante triplo assimétrico. Os pesquisadores dizem que seu dispositivo pode ser dimensionado sem perder sua dignidade.

Os tempos estão mudando, assim como as tecnologias. A memória flash, SRAM e DRAM há muito tempo ocupam uma posição dominante entre os dispositivos de memória, mas isso pode mudar se o desenvolvimento da memória universal continuar com o mesmo sucesso que neste estudo. Essa tecnologia reduzirá bastante o consumo de energia dos dispositivos equipados com ela, além de prolongar sua vida útil e aumentar a produtividade.

Estudos futuros planejados pelos autores mostrarão como a memória é revolucionária, tão orgulhosamente chamada de universal pelos cientistas.

Obrigado pela atenção, continuem curiosos e tenham uma boa semana de trabalho, pessoal!

Obrigado por ficar conosco. Você gosta dos nossos artigos? Deseja ver materiais mais interessantes? Ajude-nos fazendo um pedido ou recomendando a seus amigos, um

desconto de 30% para os usuários da Habr em um análogo exclusivo de servidores básicos que inventamos para você: Toda a verdade sobre o VPS (KVM) E5-2650 v4 (6 núcleos) 10GB DDR4 240GB SSD 1Gbps de US $ 20 ou como dividir o servidor? (as opções estão disponíveis com RAID1 e RAID10, até 24 núcleos e até 40GB DDR4).

Dell R730xd 2 vezes mais barato? Somente temos

2 TVs Intel TetraDeca-Core Xeon 2x E5-2697v3 2.6GHz 14C 64GB DDR4 4x960GB SSD 1Gbps 100 TV a partir de US $ 199 na Holanda! Dell R420 - 2x E5-2430 2.2Ghz 6C 128GB DDR3 2x960GB SSD 1Gbps 100TB - a partir de US $ 99! Leia sobre

Como criar um prédio de infraestrutura. classe usando servidores Dell R730xd E5-2650 v4 custando 9.000 euros por um centavo?