Decidi escrever esta nota em Habré em russo e em inglês, a fim de distribuir um link para ela em fóruns e grupos em inglês e em russo. O texto em russo não é uma tradução para o inglês e vice-versa - acabei de escrever uma nota duas vezes (odeio traduzir). Aqueles que querem criticar meu inglês são imediatamente enviados para o final do post, onde ficarão chocados com o meu sotaque em um vídeo de longas horas. Vejo minha ênfase não como um bug, mas como um recurso. Todos sabemos que muitos americanos acham, por exemplo, um sotaque britânico nasofaríngeo atraente. É hora de dar o mesmo status a um sotaque russo severo. Para fazer isso, o maior número possível de russos precisa fazer discursos em vários eventos internacionais. Nossa senha é "mi mi Falar a partir de maio Hart".

Mas primeiro sobre a exposição.

Milhões de consumidores de aparelhos de todo o mundo estão assistindo ao Consumer Electronics Show (CES), que acontece em janeiro em Las Vegas. Eles, que nunca souberam o que é um gatilho D, argumentam que quatro gigahertz é melhor que três nos processadores mais recentes da AMD e da Qualcomm. Mas há uma exposição focada não nos consumidores, mas nos desenvolvedores de eletrônicos. Essa exposição é chamada de Design Automation Conference (DAC) e, em alguns anos, também acontece em Las Vegas, mas não em dezembro, mas em junho.

Milhões de amantes de gadgets assistem todos os anos ao Consumer Electronics Show (CES), que acontece em Las Vegas em janeiro. Essas pessoas, que nunca aprenderam a função de um flip-flop D e como o tempo estático é calculado, discutem as frequências gigahertz depois de ler os artigos mais recentes da revista Wired que consideram uma publicação técnica. No entanto, há outra conferência, não para os consumidores, mas para os criadores de eletrônicos. Essa conferência é chamada de Design Automation Conference (DAC) e também ocorre em Las Vegas, embora não todos os anos, e não em janeiro, mas em junho.

A indústria de Automação de Projeto Eletrônico (EDA) produz software para designers de hardware. A EDA é controlada por três grandes empresas: Synopsys, Cadence e Mentor Graphics (agora parte da Siemens). A Synopsys e a Cadence têm um conjunto completo de produtos, necessários para projetar e simular um chip digital em vários níveis. O fluxo de projeto, chamado RTL2GDSII, começa na especificação e codifica o comportamento do ciclo do circuito na linguagem de descrição de hardware (Verilog ou VHDL), prossegue com a síntese dessa descrição em um gráfico de elementos lógicos (netlist) e continua a colocar a netlist em um físico planta do chip e fios de roteamento no chip para conectar as células padrão, os blocos de construção dos ASICs (circuitos integrados específicos da aplicação).

Três grandes empresas dominam o setor de automação de projetos eletrônicos: Synopsys, Cadence e Mentor Graphics (que a Siemens comprou há alguns anos). A Synopsys e a Cadence criaram um software que cobre toda a rota de projeto do RTL2GDSII. Descrevi brevemente essa rota em meu

artigo anterior do DAC, há quatro anos:

Nos últimos 25 a 30 anos, o design do microcircuito é mais frequentemente escrito na linguagem da descrição do equipamento Verilog (na Europa e entre os militares - VHDL), após o qual um programa especial (síntese lógica) transforma o design em um gráfico de fios e primitivas lógicas, outro programa (análise estática do tempo) informa ao projetista se ele se encaixa no orçamento de velocidade e o terceiro programa (local e rota) estabelece esse design no local do chip.

Quando o projeto passa por todas as etapas: codificação em um verbo, depuração, verificação, síntese, análise de tempo estático, planejamento de piso, lugar-e-rota, extração de parasitas, etc. - o arquivo GDSII é enviado para a fábrica e a fábrica assa chips. As fábricas mais famosas deste tipo são de propriedade da Taiwan Semiconductor Manufacturing Company ou TSMC.

John Sanguinetti, um guru da Verilog desde os anos 80. John foi o fundador de uma empresa chamada Simulação Cronológica que, nos anos 90, criou o VCS, um simulador de código compilado da Verilog. Este simulador agora é propriedade da Synopsys. O VCS é usado pela maioria das grandes empresas eletrônicas. A VCS trouxe para a Synopsys bilhões de dólares em receita.

Ao lado do showroom está John Sanguinetti, um dos primeiros gurus do verílogo dos anos 80 e fundador da Simulação cronológica. Essa empresa deu ao mundo o rápido simulador VCS (Verilog Compiled Code Simulator), que agora é propriedade da Synopsys. Este simulador é usado pela maioria dos principais desenvolvedores de chips. O VCS traz à Synopsys bilhões de dólares:

A Mentor Graphics agora faz parte da Siemens, a terceira maior empresa de EDA. Ao contrário de Synopsys e Cadence, o Mentor Graphics não possui uma linha completa de ferramentas RTL2GDSII. Seus dois fluxos de receita mais reconhecidos vêm do Caliber, um conjunto de ferramentas de verificação de projeto físico, e do Veloce, um emulador de hardware. O calibre inclui, por exemplo, uma ferramenta que verifica as regras de desenho geométrico (largura, espaçamento, compartimento) nos "projetos" finais do chip. O Veloce usa chips do tipo FPGA que

simulam os designs do Verilog muito rapidamente.

A Mentor Graphics, a terceira maior empresa do setor de EDA, no final de 2016 passou a fazer parte da Siemens. Ao contrário de Synopsis e Keydens, o Mentor não possui toda a cadeia de programas que cobre a rota RTL2GDSII. Duas fontes principais de receita para o Mentor são o pacote de software Caliber, que faz verificações na fase final do design do microchip, e o emulador Veloce (pronuncia-se Velochi). Um exemplo de verificação no Calibre é a distância mínima entre as faixas do chip,

para que não haja efeitos de antena .

UPD: corrigido com base no comentário de amartology : A antena geralmente é sobre outra. Ocorre quando uma faixa se torna tão grande que começa a funcionar como uma antena, recebendo um sinal na frequência das oscilações do plasma para gravação durante a produção.E o emulador Veloce usa ASICs em formato FPGA para

simular rapidamente emulações de circuitos descritos no nível lógico, ou seja, no veril.

Além dos projetos Caliber e Veloce altamente rentáveis, a Mentor sempre teve um grande número de outros projetos, produtos, serviços, treinamentos e programas educacionais. Por exemplo, o Mentor está cultivando o campo da verificação funcional, uma parte extremamente importante do fluxo de trabalho do design digital.

Além de projetos altamente lucrativos, como Caliber e Veloce, a Mentor possui muitos outros projetos, produtos, serviços, projetos de pesquisa e programas educacionais. Por exemplo, na Mentor, eles estão envolvidos na verificação funcional, uma parte crítica do processo de produção:

Várias pequenas empresas, incluindo Doulos, Willamette HDL e Sunburst Design, vendem treinamento de verificação de hardware para grandes e médias empresas eletrônicas. Esse nicho existe porque as universidades não ensinam adequadamente a arte da verificação funcional e não adotam novas tecnologias, como SystemVerilog, UVM, verificação formal usando afirmações simultâneas, estímulo portátil etc. em seu currículo por décadas. Até Stanford não o tem em seu currículo, tanto quanto eu sei, ao conversar com seus graduados.

A verificação funcional alimenta várias pequenas empresas que vendem treinamentos SystemVerilog e UVM para grandes corporações a preços refrescantemente altos, como alguns milhares de dólares por pessoa. Estes incluem Doulos, Willamette HDL, Sunburst Design e outros:

Outra pequena empresa chamada Verific. Eles têm apenas um punhado de pessoas, mas são muito bem-sucedidos em seu nicho. A Verific vende os analisadores SystemVerilog adotados por importantes empresas de EDA, grandes e pequenas.

Aqui está outra empresa pequena, de poucas pessoas, mas com muito sucesso, chamada Verific. Ela vende o analisador de Verilog, usado por muitas empresas de EDA:

O fundador da Verific dá uma entrevista a um site popular da EDA chamado EDA Cafe. Existem vários outros sites populares da EDA, incluindo o deepchip.com de John Cooley, mas desta vez não encontrei John Cooley no piso do CAD.

Aqui está o fundador da Verific, dando uma entrevista ao EDA Cafe, um site popular do setor:

Agora vamos falar sobre FPGA.

Agora vamos falar sobre FPGAs, eles são PPVM (eles vão me corrigir agora), eles são FPGA.

O que é, também descrevi brevemente no meu

artigo anterior do DAC, há quatro anos:

Na versão mais simples, um FPGA consiste em uma matriz de células homogêneas, cada uma das quais pode ser transformada em função usando multiplexadores conectados aos bits da memória de configuração. Uma célula pode se tornar uma porta AND com quatro entradas e uma saída, outra - um registro de bit único etc. Carregamos uma sequência de bits da memória na memória de configuração - e o circuito eletrônico fornecido é formado no FPGA, que pode ser um processador, controlador de exibição etc.

FPGAs / FPGAs não são processadores, “programando” FPGAs (preenchendo a memória de configuração FPGA), você cria um circuito eletrônico (hardware), enquanto que ao programar um processador (hardware fixo), você escorrega uma cadeia de instruções seqüenciais de programa escritas para ele (software).

Dois maiores produtores de FPGA são Xilinx e Altera, agora parte da Intel.

As duas maiores empresas que produzem FPGAs são Xilinx e Altera, agora parte da Intel:

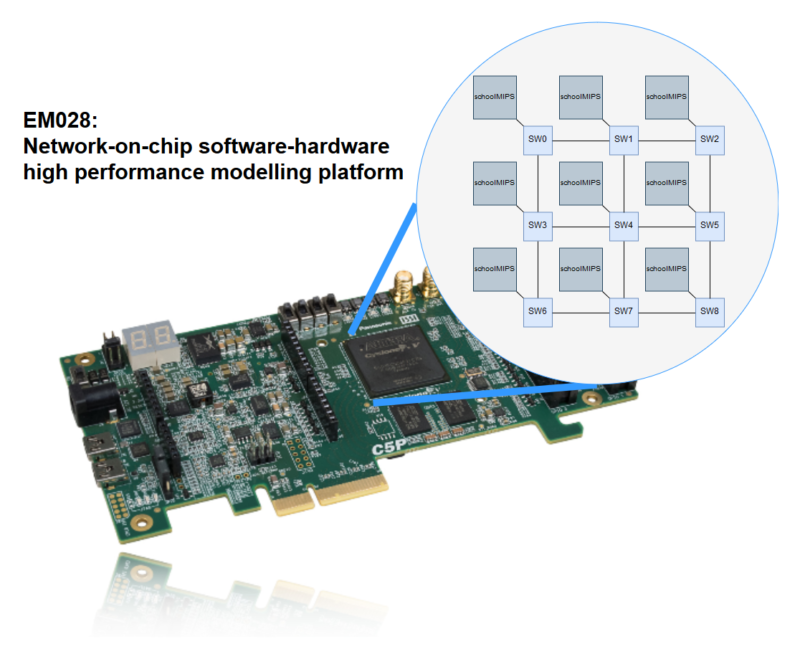

Nesta semana, a Intel obtém votos para a primeira rodada do concurso Innovate FPGA. Uma das entradas russas usa uma malha de minúsculos núcleos de processador schoolMIPS.

O schoolMIPS implementa um subconjunto da arquitetura MIPS. Existe em várias variantes, incluindo ciclo único sem memória de dados (a mais simples), uma versão com interrupções, uma versão em pipeline, etc:

A propósito, nesta semana a Intel está votando no concurso Innovate FPGA, no qual

equipes russas também participam. Um projeto é o

protótipo do sistema de multiprocessamento baseado em NoC . Esta é uma rede de protótipo em um chip com um grande número de nós baseados em processadores por Stanislav Zhelnio

sparf (baseado no livro de Harris & Harris “Síntese digital e arquitetura de computadores”)

https://github.com/MIPSfpga/schoolMIPS . Faz aluno de 4 anos no MIEM NRU HSE:

O mundo dos FPGAs não se limita ao Xilinx e Altera / Intel. Existem vários fornecedores muito menores, como Lattice e Microsemi / Actel, e até mesmo pequenas empresas que não projetam os chips finais licenciam o design de blocos de células FPGA para empresas ASIC. Uma aplicação útil seria criar um coprocessador reconfigurável conectado a um núcleo fixo de CPU de alta frequência. Outra aplicação é a segurança: algumas empresas desejam ocultar seus segredos em uma lógica reconfigurável em vez de mostrar o layout de sua lógica fixa a um pesquisador motivado com microscópio eletrônico e muito tempo.

Mas há menos players no mundo do FPGA, por exemplo, aqui estão duas empresas que licenciam o design de blocos FPGA que podem ser incorporados em circuitos fixos de várias execuções para oferecer flexibilidade.

Todo DAC tem vários fornecedores de placas FPGA. Não os fornecedores de conselhos de estudantes baratos, como Digilent e Terasic, que começam a partir de US $ 55, mas os conselhos de FPGA para prototipagem ASIC que podem custar US $ 30.000, US $ 100.000 ou mais.

O DAC é tradicionalmente frequentado por fabricantes de placas FPGA. Eles não vendem cartões de estudante baratos por US $ 55 dólares, mas placas FPGA sérias por US $ 55 _ mil dólares e mais. O cliente deles não é aluno, mas uma equipe de desenvolvimento ASIC severa que usa placas grandes para prototipagem.

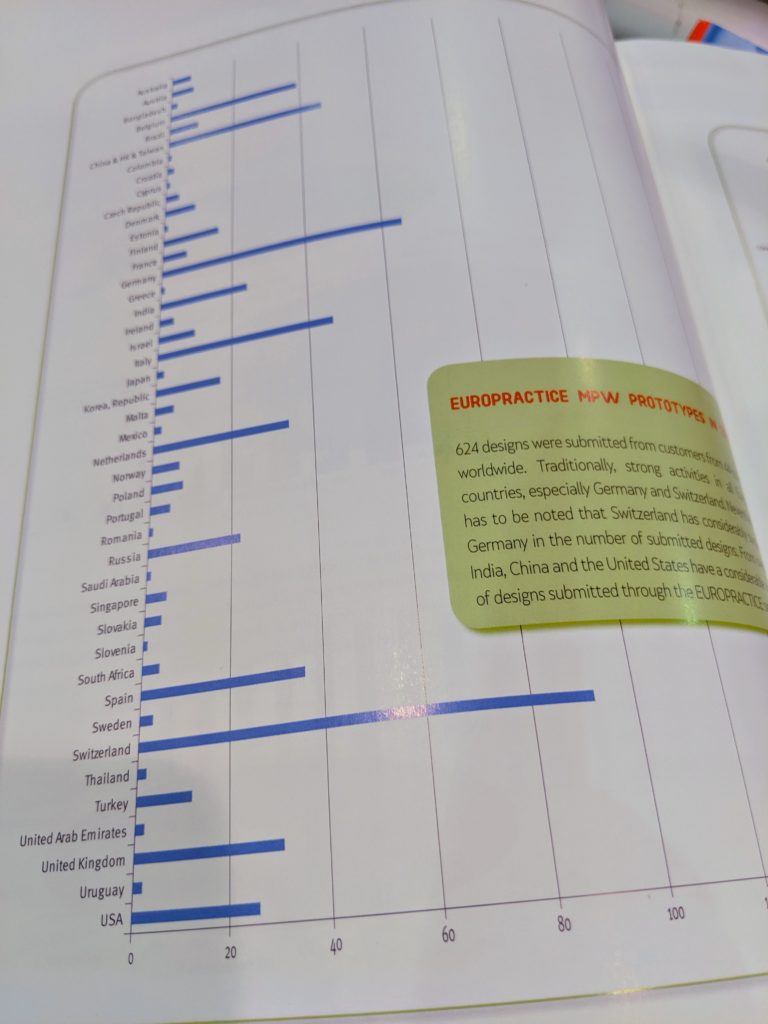

E se um pesquisador fizesse alguma prova de conceito usando FPGA e agora quis fabricar seu próprio ASIC? Uma ordem comercial típica para fabricar um ASIC geralmente requer o pagamento inicial de ~ US $ 300.000 a ~ US $ 3.000.000, dependendo da tecnologia do processo. No entanto, existem empresas especializadas, Europractice na Europa e MOSIS nos EUA, que vendem serviços de “shuttle” de pequena quantidade ou serviços de wafer de múltiplos projetos (MPW), começando com apenas US $ 3000 para a tecnologia de 180 nm ou apenas dezenas de dólares para algo moderno, como 28nm.

Mas e se um estudante ou uma empresa dura quisesse fazer um ASIC real em uma fábrica e houvesse pouco ou pouco dinheiro? Ou, se não estiver arrependido, é um chip de teste ou um lote muito pequeno? Para fazer isso, na América existe uma empresa MOSIS e na Europa - Europractice. Alguns milhares de dólares - e você tem em suas mãos o chip que projetou para tecnologias como 180 nanômetros. Algumas dezenas de milhares - e você tem em suas mãos o seu chip com tecnologia mais recente, por exemplo, 28 nanômetros, como o quinto iPhone. Observo que, para a produção comercial em massa, o pagamento inicial à fábrica é de centenas de milhares de dólares em tecnologias antigas a dois ou três milhões em novas.

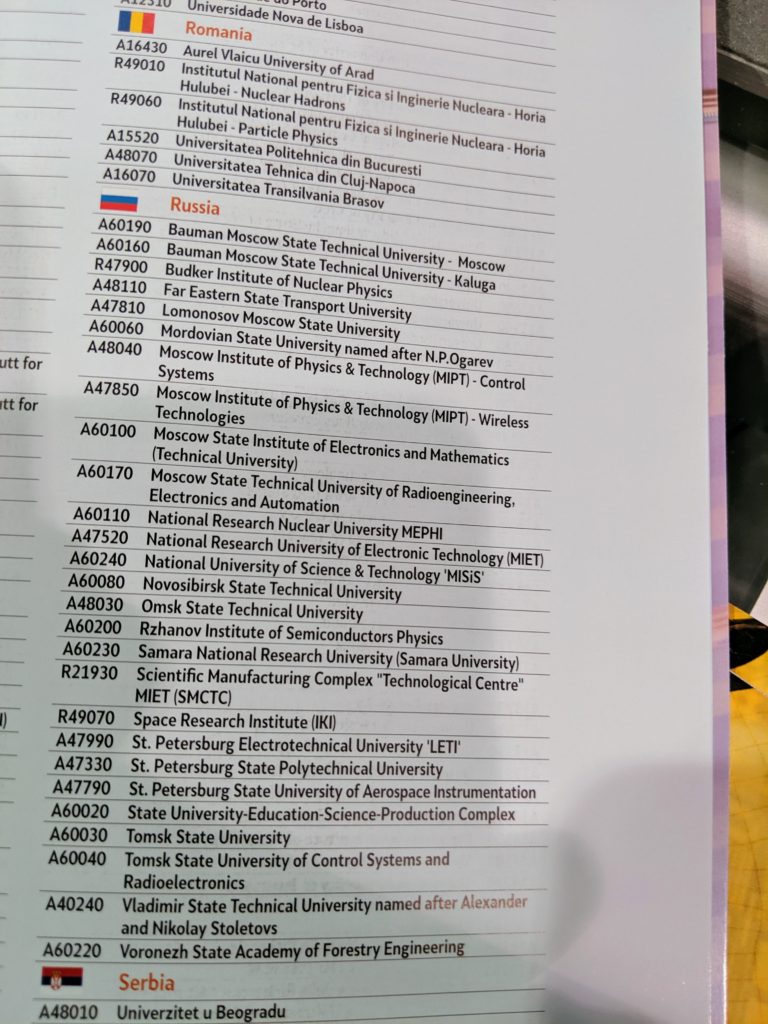

É interessante que a Europractice tenha clientes na Rússia, mesmo em Omsk. Admita quem cria os ASICs em Omsk.

A Europractice possui várias empresas russas, incluindo alguém em Omsk:

Existem empresas com modelos de negócios que são um tanto misteriosos para mim. Por exemplo, eu não entendo como essa empresa abaixo pode sobreviver em um nicho de plug-in do Eclipse. Eu acho que eles obtêm mais receita vendendo alguns serviços de consultoria.

Existem empresas sobre as quais eu não entendo como elas ganham. Por exemplo, este está vendendo um plug-in do Eclipse muito nicho. Certamente eles não vivem dele, mas de algum tipo de consultoria.

Outra empresa de nicho com modelo de negócios não óbvio. Eles traduzem uma descrição de registros visíveis por software em lógica de cola Verilog e outros arquivos de interface. Eu acho que essa empresa pode ter algum grande cliente do tipo Cisco que ficou viciado em sua tecnologia há muito tempo e os paga desde então.

Outra empresa de nicho com um modelo de negócios não óbvio. Eles traduzem a descrição dos registros disponíveis para o programador em arquivos de verificação e de interface. Eles provavelmente têm algum cliente importante, como a Cisco, que há muitos anos se apaixonou por sua ferramenta e, desde então, paga desde que é chato contratar um cliente para gerenciar seu engenheiro.

Um cavalheiro melancólico da Huawei descreveu suas realizações em chips de rede. A Huawei obviamente depende das ferramentas da EDA dos EUA, ainda mais do que no mercado Android e nos núcleos de CPU do ARM. Eles custam dinheiro e o número de especialistas técnicos necessários para desenvolver um equivalente ao compilador Synopsys IC é muito maior, na minha opinião, do que os recursos necessários para projetar um concorrente de ponta para os núcleos ARM.

Um representante da Huawei também se sentou na exposição com uma expressão de tristeza no rosto. Observo que se o governo dos EUA forçar as empresas da EDA a proibir os chineses, a situação chinesa será muito pior do que é agora, já que é tecnicamente mais difícil clonar o Synopsys IC Compiler do que os núcleos de processadores ARM e Android Market.

Todo DAC desde 1998 tinha pelo menos uma empresa desenvolvendo outro compilador C-para-Verilog. Em 1998, era

minha própria startup . Este ano é outra pessoa:

Desde 1998, existe pelo menos uma empresa no DAC que compila C em Verilog. Em 1998, essa empresa era minha própria startup. Este ano outra pessoa:

Esse cavalheiro ganha a vida vendendo soluções que combatem o chamado "Zakladki" (um termo russo, um plural de "Zakladka"). Expliquei a ele o significado do termo e ele concordou que é isso que ele vende.

Aqui está um companheiro que faz com que os analisadores vivos sejam favoritos nos processadores:

Trouxe ao DAC minha filha estudante para que ela veja como o pai ganha a vida:

Trouxe minha filha para Las Vegas para que ela pudesse ver como as pessoas ganham dinheiro no duro mundo industrial da indústria eletrônica e percebi que os dólares do papai não cresciam nas árvores:

Festa após a exposição:

Na festa após a exposição:

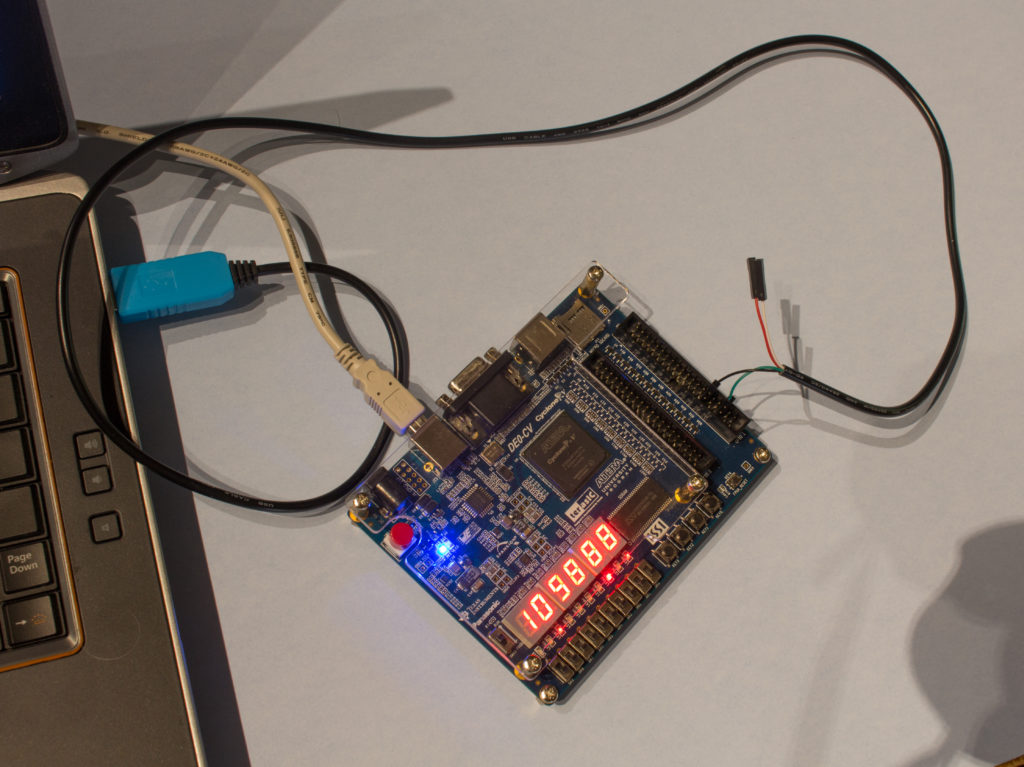

Após a exposição, fiz o MIPS Open Developer Day, juntamente com meus colegas da Wave Comnputing. Temos várias pessoas de algumas das empresas acima mencionadas + meus amigos russos da

VivEng , um serviço de design de sinais mistos do Vale do Silício da Califórnia que também tinha alguns clientes em Zelenograd, um vale do silício russo. Primeiro fizemos uma

apresentação e , em seguida, os participantes fizeram alguns exercícios nas placas Digilent Nexys4 DDR e Terasic DE10-Lite FPGA.

Então, juntamente com meus colegas, conduzi o seminário MIPS Open. Estiveram presentes camaradas de algumas das empresas descritas, incluindo aquelas que licenciam ferramentas FPGA e EDA incorporadas, vendem serviços para produção, realizam treinamento de verificação e também fabricam chips como tal. E também meus velhos amigos da empresa russa

VivEng . Meus colegas e eu mostramos

esses slides , após os quais os participantes experimentaram exemplos sobre FPGAs Digilent Nexys4 DDR e Terasic DE10-Lite.

Para repetir os resultados, você pode baixar e combinar dois pacotes:

Se você deseja reproduzir os resultados, faça o seguinte:

- Acesse https://www.mipsopen.com/mips-open-components/mips-open-fpga-getting-started-guide .

- Faça o download do pacote MIPSfpga 2.0 padrão.

- Acesse https://github.com/MIPSfpga/mipsfpga-plus .

- git clone github.com/MIPSfpga/mipsfpga-plus.git

- Copie os arquivos RTL principais do pacote MIPS Open FPGA para o subdiretório principal do pacote MIPSfpga + - consulte as instruções em https://github.com/MIPSfpga/mipsfpga-plus/tree/master/core

O Intel FPGA Quartus Prime Lite Edition ou o Xilinx Vivado, bem como o Codescape GCC Bare Metal Toolchain devem estar instalados no seu computador. Depois disso, você pode seguir as instruções dos slides:

Você precisa ter o Intel FPGA Quartus Prime Lite Edition ou o Xilinx Vivado instalado em seu sistema, bem como o Codescape GCC Bare Metal Toolchain. Depois disso, você pode seguir as instruções dos slides:

- cd your_git_directory / boards / board_directory (por exemplo de10_lite ou nexys4_ddr)

- faça toda a carga

- Pressione reset (ou KEY 0 em algumas placas) para redefinir o processador.

- O programa codificado padrão deve começar a funcionar.

- cd your_git_directory / programs / 00_counter (ou outro programa)

- criar programa srecord uart

- Se o computador usar uma conexão serial diferente de ttyUSB0 (o padrão), então:

- criar programa srecord uart UART = 1 (ou 2, 3, etc)

- O programa carregado via USB para UART está em execução.

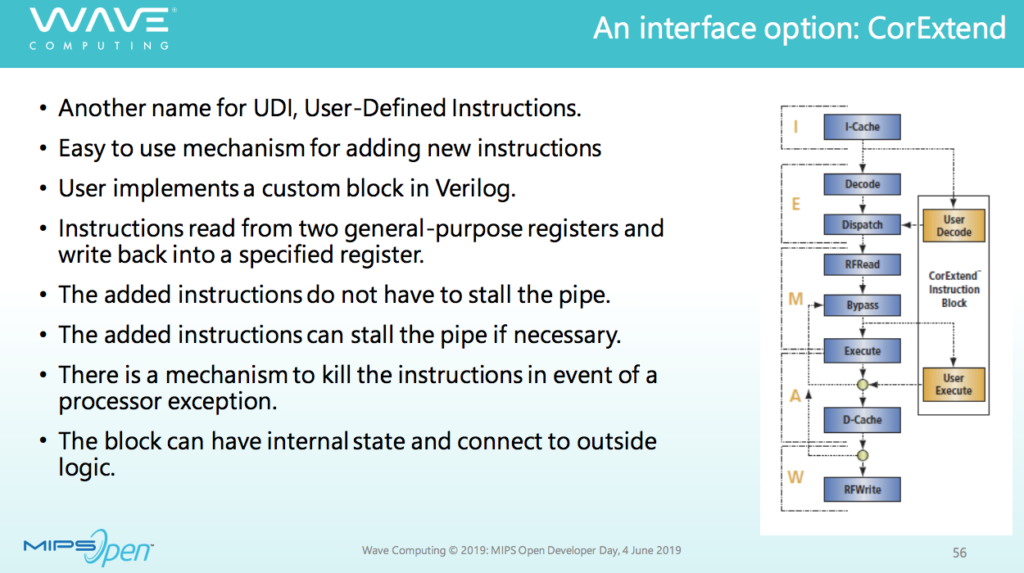

Na apresentação, mostrei como incorporar um bloco no processador que decodifica e executa instruções adicionais ao sistema principal de comandos que podem ser determinados pelo projetista do sistema em um chip. O bloco pode ser sintetizado e tornar-se parte do microcircuito ou ser configurado no FPGA / FPGA.

Instruções adicionais se movem ao longo do pipeline do processador, juntamente com as principais. Eles recebem dados de registradores gerais visíveis ao programador e podem retornar o resultado ao registrador. Essas instruções também podem salvar algum estado no coprocessador. Eles podem ser eliminados por exceções se ocorrer uma exceção, por exemplo, no pipeline após esta instrução:

A apresentação tem uma explicação detalhada, como adicionar instruções dos processadores definidos pelo usuário ao núcleo da CPU MIPS microAptiv UP e sintetizá-lo juntamente com algumas SoC simples para placa FPGA:

Trecho de código de hardware Verilog do texto de exemplo. Este código implementa, no nível de transferência de registros (RTL), uma instrução especializada para calcular uma rede neural convolucional:

Um fragmento de um módulo CorExtend personalizado que implementa uma Instrução Definida pelo Usuário (UDI) para um caso especial de computação em rede neural:

Amanhã vou para a Rússia para ajudar em outro seminário, não para profissionais de eletrônica e EDA, mas para crianças interessadas em explorar carreiras em design microeletrônico digital. Para esta viagem, criei um simples videoprocessador 2D integrado ao núcleo MIPS Open FPGA, bem como um exemplo de jogo apenas de hardware (sem CPU ou software) para VGA. As crianças gostam de jogos e eu vou usar o design de jogos para ensinar a eles o básico da metodologia RTL:

E na próxima segunda-feira

, 8 de julho, ensinarei o básico do desenvolvimento de circuitos digitais para crianças em idade escolar em Zelenograd .

Para ele, escrevi exemplos da implementação de gráficos simples de sprites no FPGA. Um circuito sintetizado a partir do verílogo desenha sprites em uma tela VGA.

Aqui está um exemplo de trabalho em um hardware limpo (

códigos-fonte no github ). Uma variante do combate naval, onde um satélite torpedo vermelho procura uma cruz azul inimiga:

E aqui está um exemplo de uma combinação de hardware e software - uma saudação de sprites.

Peça de hardware e

parte de software :

Sim, e prometi fazer meus discursos em Las Vegas. Aqui está uma peça:

Vista da Las Vegas Strip quando escurecer, mas ainda não há multidões:

E a vista da rua na faixa, quando já é noite, mas ainda não há multidões:

Durante dois dias em Las Vegas, não tive chance de jogar, por isso joguei com US $ 1 quando nosso avião de volta a San Jose estava embarcando no aeroporto de Las Vegas:

Por todo esse tempo, nunca toquei em Las Vegas, porque andei pela exposição e conversei sobre tópicos eletrônicos, depois realizei um seminário. Mas, ao embarcar no avião, notei, perdeu um dólar: