Processos de fabricação intermediários, diferentes tipos de transistores e muitas outras opções adicionam incerteza ao processo de fabricação de eletrônicos.

Os fabricantes de eletrônicos estão se preparando para a próxima onda de processos de fabricação de ponta, mas seus clientes serão confundidos com várias opções confusas - seja para desenvolver chips usando a tecnologia de processo de 5 nm, esperar 3 nm ou escolher algo entre eles.

O caminho para 5 nm é bem definido, diferentemente de 3 nm. Depois disso, o cenário fica confuso, pois as fábricas adicionam processos intermediários de fabricação, como 6 nm e 4 nm. Mudar para qualquer um desses processos técnicos é muito caro e os benefícios nem sempre são óbvios.

Outro motivo de preocupação é a redução da base de fabricação. No caso dos processos técnicos mais avançados, a escolha dos fabricantes é pequena. Havia vários fabricantes líderes no setor, mas com o tempo essa área diminuiu devido a um aumento acentuado no custo e uma diminuição na base de usuários. Em geral, quanto menos fabricantes, menos opções de tecnologia e preço.

Hoje, a Samsung e a TSMC são os

únicos dois fabricantes que trabalham com processos tecnológicos de 7 nm ou menos, embora isso possa mudar. A Intel e a empresa chinesa SMIC estão desenvolvendo processos avançados de fabricação. A Intel, que não é o maior player no campo da produção comercial, está enfrentando problemas com o desenvolvimento da tecnologia de processo de 10 nm. E não está claro se o SMIC será capaz de fornecer 7 nm, pois esse tópico ainda está em fase de pesquisa e desenvolvimento (o mesmo ocorre com a Intel com a tecnologia de processo de 10 nm).

Quanto aos processos de fabricação mais avançados, a Samsung e a TSMC trabalham com 7 nm usando transistores finFET, e ambos os fabricantes continuarão com os 5 nm. Diferentemente dos transistores planares tradicionais, os finFETs são estruturas tridimensionais com melhor desempenho e menos vazamentos.

Então, a 3 nm, a Samsung passará do finFET para a nova arquitetura de transistor nanométrico FET, que é um desenvolvimento da tecnologia finFET. A TSMC ainda não revelou seus planos para 3 nm, deixando muitos clientes no limbo. O TSMC, de acordo com fontes, pesa uma variedade de opções, incluindo nanocamadas, nanofios e finFETs forçados. Intel, TSMC e outros também estão trabalhando em novas formas de empacotamento avançado como possíveis opções para redução de escala.

No entanto, a 3 nm, o tamanho da tecnologia do transistor pode ir em direções diferentes. O finFET ainda pode ser reproduzido, mas essa tecnologia precisa de alguns avanços. Aparentemente, o setor terá que se preparar para a transição para a nova arquitetura da tecnologia de processo de 3 nm e a próxima tecnologia de processo intermediária a 2 nm, a julgar pelos planos de desenvolvimento de uma organização que trabalha nessa área.

"5 nm ainda são finFET", disse Naoto Horiguchi, diretor de programa da Imec. - Digamos que a 3 nm entraremos em um período de transição do finFET para outras arquiteturas. Acreditamos que serão nanocamadas. ”

Os FETs da Nanolayer estão relacionados à arquitetura dos transistores gate-all-around (GAA). E essa não é a única opção. “O setor é muito conservador. Seus participantes tentarão espremer tudo, desde o finFET até o limite ”, disse Horiguchi. - No processo de fabricação de 3 nm, temos a oportunidade de usar o finFET. Mas precisaremos fazer várias inovações no finFET, melhorá-las em geral. ”

Os fabricantes de chips permanecerão na tecnologia de processo de 7 nm, migrarão para 5 nm, 3 nm ou para o intermediário? 7 nm fornece desempenho suficiente para quase todas as aplicações, portanto esse processo permanecerá por muito tempo. Lá fora, existem várias opções de alto desempenho, e todas elas custam mais. E veremos se essas tecnologias têm tempo para aparecer a tempo.

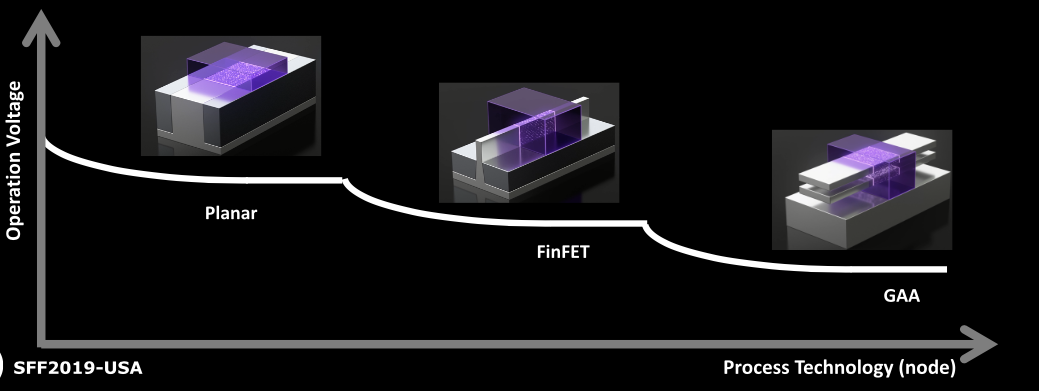

A tensão operacional de vários processos de fabricação é de transistores planares, finFET e FAN de nanocamada.

A tensão operacional de vários processos de fabricação é de transistores planares, finFET e FAN de nanocamada.Ruína de produção

O chip consiste em muitos transistores atuando como comutadores. Por muitas décadas, o progresso dos circuitos integrados foi consistente com a lei de Moore, segundo a qual a densidade de transistores em um dispositivo duplica em um período de 18 a 24 meses.

Em ritmo semelhante, os fabricantes introduziram novos processos tecnológicos com maior densidade de transistores, o que permitiu à indústria reduzir o custo de chips em termos de número de transistores. Em cada processo de fabricação, os fabricantes aumentaram as especificações do transistor em 0,7 vezes, permitindo que a indústria aumentasse a produtividade em 40% com o mesmo consumo de energia e uma redução dupla na área.

A indústria de circuitos integrados seguiu essa fórmula e floresceu. Desde a década de 1980, abriu o caminho para PCs rápidos a preços com desconto.

Em 2001, já havia pelo menos 18 fabricantes com fábricas onde podiam fabricar chips a 130 nm, o que na época era um processo técnico avançado, de acordo com o IBS. Além disso, vários outros novos fabricantes apareceram, fabricando chips sob medida nas fábricas de outras pessoas. Além disso, a fabricação de chips era praticada em laboratórios que os desenvolveram, mas não possuíam produção própria.

No final da década, os custos de produção e processos de fabricação aumentaram. Incapaz de lidar com o aumento de preço, muitos fabricantes de chips mudaram para o modelo fab lite. Eles produziram alguns chips em casa e os demais foram terceirizados.

Com o tempo, menos fabricantes de chips fabricaram dispositivos avançados em suas próprias instalações. Alguns se livraram completamente da produção ou deixaram esse negócio.

No entanto, nos anos 2000, apareceu um modelo de negócios de oficinas de silício. Os workshops ficaram para trás da Intel e de outras empresas de tecnologia, mas deram às empresas de design acesso a vários processos.

A próxima grande mudança ocorreu no estágio de 20 nm, quando os transistores planares tradicionais atingiram uma parede e encontraram

um efeito de canal curto . Em resposta, a Intel mudou para a próxima geração de tecnologia de transistor, finFET, a 22 nm em 2011. Workshops trocados para finFET a 16/14 nm.

O FinFET tem várias vantagens sobre os transistores planares. “Nesse esquema, o transistor inteiro se estende verticalmente, de modo que o canal se eleva acima do substrato e a válvula envolve três lados da aleta. O aumento da área de contato da válvula permite um melhor controle da corrente de fuga ”, escrevem Matt Kogorno e Toshihiko Miyashita da Applied Materials. Kogorno é o diretor de gerenciamento global de produtos e Miyashita é o principal tecnólogo.

O FinFET também é um dispositivo mais complexo, é mais difícil produzi-lo e dimensioná-lo para cada processo técnico subsequente. Como resultado, o custo de P&D subiu para o céu. Portanto, agora o ritmo de uma mudança de processo completa aumentou de 18 meses para 2,5 anos ou mais.

Os preços dos circuitos integrados também continuam subindo. O custo do desenvolvimento de um dispositivo plano em 28 nm varia de US $ 10 milhões a US $ 35 milhões, segundo o Gartner. Para comparação, o custo de projetar um sistema de chip único (SoC) a 7 nm varia de US $ 120 milhões a US $ 420 milhões.

"O custo do desenvolvimento é altamente dependente da complexidade do SoC", disse Samuel Wen, analista da Gartner. - Dois terços vão para o desenvolvimento do chip. O resto é o desenvolvimento de submarinos, o custo das máscaras e a melhoria da produção. Com o tempo, o custo do design também cai. ”

No entanto, as tendências de preços mudaram o cenário do mundo dos circuitos integrados. Com o tempo, menos empresas podem pagar pelo design de chips para os processos de fabricação mais avançados. Muitos deles contam com oficinas para problemas de produção.

Uma diminuição no número de clientes, juntamente com um aumento no custo de produção, influenciaram o cenário das oficinas produzindo chips avançados. Por exemplo, restam cinco fabricantes / oficinas no mercado de 16/14 nm: GlobalFoundries, Intel, Samsung, TSMC e UMC. O SMIC também trabalha com o finFET em uma tecnologia de processo de 14 nm.

E às 7 nm, outra transição aconteceu. Os processos tecnológicos e o custo de produção continuaram a crescer, e o retorno do investimento já estava em questão. Como resultado, a GlobalFoundries e a UMC no ano passado pararam de tentar desenvolver uma tecnologia de processo de 7 nm. Ambas as empresas continuam a operar no mercado de 16/14 nm.

Tentando desenvolver ainda mais, a Samsung e o TSMC correm a toda velocidade para a curva de 7 nm e além. Após vários atrasos, a Intel planeja lançar a produção a 10 nm em meados de 2019 e a 7 gm - até 2021. Enquanto isso, o SMIC não promete prazos.

Mas nem todos os clientes da oficina exigem processos de fabricação avançados. Existe um mercado próspero para chips de 28 nm. "Tudo depende das características do produto", disse Ven da Gartner. - Alguns produtos exigem desempenho máximo. Os desenvolvedores ainda podem usar processos técnicos desatualizados. E os chips para aplicativos que não exigem alto desempenho podem viver nos processos de fabricação N-1 e N-2. ”

Outros o ecoam. “Quantas empresas podem comprar o silício mais recente hoje do ponto de vista econômico? O número deles está diminuindo. Em mercados que exigem desempenho extremamente alto, essa necessidade sempre será. Mas na cadeia de suprimentos, em termos de volumes, uma ruptura se forma no meio. Os clientes mais exigentes exigem processos tecnológicos às 7, 5 e possivelmente um dia a 3 nm. Mas todo mundo desacelerou um pouco ”, disse Walter Eun, vice-presidente de gerenciamento de negócios da UMC.

Mas, em certos casos, são necessários os chips mais avançados - servidores e smartphones. Há também um mar de novas startups relacionadas aos chips de IA. Muitas empresas projetam chips para aprendizado de máquina e aprendizado profundo.

“Ninguém argumenta que a necessidade de contar algo 10 vezes mais rápido do que hoje sempre será comercialmente útil e competitiva, mesmo em mercados não técnicos. Todas essas realizações únicas da tecnologia de aprendizado profundo são evidências disso. Literalmente, não há fim para pedidos de energia cada vez maior do computador ”, disse Aki Fujimura, diretor da D2S.

"As demandas por poder computacional sofreram várias mudanças importantes - no início, era a GPU e depois - aprendizado profundo", disse Fujimura. - O aprendizado profundo é uma tecnologia massiva para encontrar padrões adequados, e o treinamento de redes neurais é a tarefa de otimização consistente. Agora que o mundo criou um mecanismo para processar uma enorme quantidade de dados e transformá-los em informações úteis na forma de um programa capaz de conclusões lógicas, o número de cálculos necessários aumenta com a quantidade de dados disponíveis. E como a quantidade de dados em todas as áreas está crescendo exponencialmente, é garantido que os requisitos para o poder da computação aumentem significativamente, pelo menos no campo do aprendizado profundo. ”

Ainda não está claro se os chips de AI requerem processos técnicos de 5 nm ou mais, mas definitivamente existem requisitos para um aumento no poder de computação. Mas a migração para esses processos tecnológicos não se torna um processo mais fácil ou mais barato.

5 nm vs 3 nm

Enquanto isso, no início de 2018, a TSMC alcançou outro marco, tornando-se o primeiro fabricante no mundo a usar a tecnologia de processo de 7 nm. A Samsung mais tarde se juntou à corrida de 7 nm. O processo de fabricação de chips a 7 nm é baseado principalmente no finFET e consiste em fabricar chips com uma etapa de porta de 56 a 57 nm e uma etapa mínima de colocação de condutores de metal [passo do metal] a 40 nm, de acordo com informações da IC Knowledge e TEL.

Na primeira versão de 7 nm, o TSMC usou

litografia de imersão de 193 nm e padronização múltipla. Este ano, a TSMC promete lançar uma nova versão de 7 nm usando litografia ultravioleta extrema (EUV). O EUV simplifica as etapas do processo, mas é uma tecnologia cara e possui seu próprio conjunto de dificuldades.

A TSMC está preparando sua nova tecnologia de processo de 5 nm para lançamento no primeiro semestre de 2020. A nova tecnologia da TSMC a 5 nm será 15% mais rápida que 7 nm e consumirá 30% menos energia. A segunda versão da tecnologia de processo de 5 nm, lançada no próximo ano, será 7% mais rápida. Ambas as versões usarão EUV.

O TSMC já está recebendo pedidos a 5 nm. "Grandes pedidos são esperados da Apple, HiSilicon e Qualcomm", disse Handel Jones, diretor do IBS. "O volume de substratos será de 40.000 a 60.000 por mês até o quarto trimestre de 2020".

A velocidade de transição a 5 nm para o TSMC é inferior a 7 nm. Em primeiro lugar, o 5nm é um processo completamente novo, com ferramentas e patentes atualizadas da EDA. Além disso, é mais caro. Em média, o custo do desenvolvimento de um dispositivo a 5 nm varia de US $ 210 milhões a US $ 680 milhões, segundo o Gartner.

Alguns fabricantes de chips querem se afastar dos 7nm sem gastar tanto dinheiro quanto 5nm. Portanto, a TSMC introduziu recentemente uma nova tecnologia de processo de 6 nm, mais barata, mas com alguns compromissos.

"Os números N6 e N5 não parecem ser diferentes, mas na verdade a diferença é grande", disse S. S. Wei, diretor da TSMC na última reunião. - No N5, em comparação com o N7, a densidade lógica é aumentada em 80%. N6 comparado ao N7 apenas 18%. Como você pode ver, há uma grande diferença entre a densidade lógica e a eficiência dos transistores. Como resultado, o consumo geral de energia do chip N5 é menor. Há muitos benefícios em mudar para o N5. Mas o N5 é um processo técnico completo e leva tempo para os clientes desenvolverem novos produtos para ele. A beleza do N6 é que, se eles já têm um projeto no N7, terão que gastar muito pouco esforço. Eles podem atualizar para o N6 e obter certos benefícios. E, dependendo das características do produto e do mercado, os clientes decidirão o que fazer. ”

Enquanto isso, a Samsung lançou 5 nm, que aparecerão no primeiro semestre de 2020. Comparada aos 7 nm, a nova tecnologia de processo de 5 nm da Samsung no finFET oferece até 25% de compactação lógica e 20% menos consumo de energia ou 10% mais velocidade.

A Samsung também introduziu uma nova tecnologia de processo de 6 nm, oferecendo aos clientes outra opção. "6nm tem a vantagem de escalabilidade com 7nm e reutilização de propriedade intelectual", disse Ryan Lee, vice-presidente de marketing de workshops da Samsung. E os planos da Samsung já têm o desenvolvimento da tecnologia de processo de 4 nm finFET. Até o momento, praticamente não há informações abertas sobre essa tecnologia.

Após 5 nm, vários processos de fabricação completos custam 3 nm. Mas 3 nm não é para os fracos. O custo do desenvolvimento de um dispositivo para a tecnologia de processo de 3 nm varia de US $ 500 milhões a US $ 1,5 bilhão, de acordo com o IBS. O custo do processo de desenvolvimento varia de US $ 4 bilhões a US $ 5 bilhões e a produção - de US $ 15 a US $ 20. "O custo dos transistores de 3 nm deve ser 20 a 25% superior a 5 nm da mesma disponibilidade", disse Jones da IBS. "Podemos esperar um aumento de 15% na eficiência e uma redução de 25% no consumo de energia em comparação com o finFET de 5 nm."

A Samsung é a única empresa a anunciar planos para desenvolver uma tecnologia de processo de 3 nm. Para isso, a oficina mudará para a arquitetura de transistores circulares, nanocamadas. A TSMC ainda não divulgou planos, motivo pelo qual alguns acreditam que a empresa está atrasada. "Com 3nm, a Samsung tem grande probabilidade de entrar em produção em volume em 2021", disse Jones. "O TSMC acelera o desenvolvimento, tentando acompanhar a Samsung."

A 3 nm, o TSMC examina FETs de nanocamada, FETs de nanofios e até finFETs. Uma das maneiras de expandir a tecnologia finFET é usar materiais de alta mobilidade nos canais, principalmente na Alemanha. Os dispositivos finFET atuais usam silício ou silício-germânio (SiGe) nos canais. Ao aumentar a mistura de germânio, você pode aumentar a mobilidade do canal - ou seja, a velocidade de passagem dos elétrons pelo dispositivo. E aqui o problema é o gerenciamento de defeitos.

Estender a tecnologia finFET faz sentido. O finFET a 3 nm fornece um caminho de transição a partir de 5 nm. No entanto, existem problemas. Teoricamente, a tecnologia finFET chega a um beco sem saída quando a largura da aleta atinge 5 nm, o que está próximo do estado atual. "Hoje usamos duas nadadeiras para NMOS e três para PMOS em uma célula padrão", disse Horiguchi, do Imec. - Um dos aspectos importantes de 3 nm é que precisamos mudar para uma arquitetura de aleta única para projetos de células padrão. Uma única barbatana deve funcionar bem o suficiente. Para expandir a tecnologia finFET para N3, precisamos de uma tecnologia especial para melhorar o poder de uma única aleta e reduzir fenômenos espúrios de segundo plano. ”

Além da alta mobilidade do finFET, a próxima opção é o GAA. Em 2017, a Samsung introduziu o Multi Bridge Channel FET (MBCFET) para 3 nm. MBCFET - Nanolayer FET. O teste da MBCFET da Samsung estará disponível em 2020.

Os chips de nanocamada têm vantagens sobre o finFET. No finFET, o obturador se curva em torno da aleta de três lados. Nas nanocamadas, o obturador está localizado em quatro lados da aleta, o que dá mais controle sobre a corrente.

Comparados a 5 nm, os FETs de nanocamada da Samsung fornecem até 45% de aumento na eficiência da área lógica e uma redução de 50% no consumo de energia ou um aumento de 35% na velocidade. “A estrutura do finFET tem suas próprias limitações de escalabilidade, uma vez que a tensão de alimentação não pode ser reduzida abaixo de 0,75 V. Nossa inovação com o uso de nanocamadas reduz a tensão a valores inferiores a 0,7 V”, disse Samsung Samsung.

Existem vários tipos de tecnologias GAA, incluindo FET de nanocamada e FET de nanofios. O GAA em si é o próximo passo após o finFET. Nesse sistema, o finFET está localizado de lado e depois dividido em partes horizontais. Peças formam canais. O material do obturador envolve cada camada.Comparado ao FET de nanofios, esse circuito possui canais mais amplos, ou seja, maior produtividade e corrente de excitação. "As nanocamadas têm larguras mais efetivas", disse Imec Horiguchi. "Nanofios se saem muito melhor com eletrostática." Mas sua seção transversal é muito pequena. Isso não dará vantagens em termos de largura efetiva do canal ".As arquiteturas GAA têm vários problemas. Geralmente eles dão um aumento extremamente pequeno em comparação com o finFET a 5 nm. Fazer chips usando essa tecnologia é bastante difícil."A próxima geração de GAA a 3 nm e abaixo adiciona outro nível de complexidade à fabricação", disse Richard Gotshaw, vice-presidente e diretor técnico da Lam Research . - À primeira vista, parece uma modificação no finFET. No entanto, os requisitos estão aumentando e a complexidade dessa arquitetura GAA é significativamente maior que o finFET. ”No processo de produção de chips de nanocamada, o primeiro passo é a colocação de finas camadas alternadas de SiGe e silício no substrato. “Temos uma pilha de silício, silício-germânio, silício. Chamamos isso de superlattice ”, disse Namsun Kim, diretor de engenharia da Applied Materials, em uma entrevista recente. "Com conteúdo de germânio, você precisa fornecer uma boa camada de isolamento".No mínimo, o pacote deve consistir em três camadas de SiGe e três de silício. Em seguida, pequenas estruturas de folha são aplicadas ao pacote. Depois disso, é formado o isolamento com ranhuras e, em seguida, divisores internos.Em seguida, as camadas de SiGe são removidas do superlático, deixando as camadas de silício com um espaço vazio entre elas. Cada camada de silício forma a base da folha ou canal no dispositivo. Então você precisa aplicar um material com uma constante dielétrica alta para criar um obturador. “Existe uma distância mínima entre os nanofios. Muito pequeno O problema é colocar metal com espessura de trabalho lá ”, disse Kim.O setor trabalhou ao longo dos anos para criar a tecnologia GAA, mas ainda existem alguns problemas. "Um dos principais é a capacitância parasitária", disse Kim. - Se você me perguntar quais são os principais problemas da tecnologia GAA, existem dois deles. Divisores internos e isolamento de substrato ".O que vem a seguir?

Quanto tempo é suficiente a tecnologia GAA ou as nanocamadas? “As nanocamadas sobreviverão às duas ou três da próxima tecnologia de processo. As oficinas podem produzir nanocamadas no N3. A próxima geração é certa. E depois disso, talvez você precise alterar a integração de nano-camadas ou arquitetura. Mas ainda será a arquitetura de nanocamada ”, disse Horiguchi, do Imec.O setor está explorando maneiras de melhorar as tecnologias GAA e finFET em processos avançados de fabricação. Atualmente, os dispositivos GAA oferecem uma pequena vantagem sobre o finFET. Por exemplo, o passo do obturador do chip anterior da nano-camada Imec era de 42 nm e o passo mínimo dos condutores de metal era de 21 nm. Em comparação, os finFETs a 5 nm podem ter um passo de gate de 48 nm e um passo mínimo de condutores de metal de 28 nm.Em laboratório, a Imec demonstrou a escalabilidade de um dispositivo semicondutor do tipo p com uma pilha dupla de GAA e germânio no canal. Usando um circuito sem extensão, a Imec desenvolveu um nanofio com um comprimento de porta de cerca de 25 nm. Pode ser adaptado para nanocamadas. Como na versão anterior, o tamanho do fio é 9 nm.O germânio pode desempenhar um papel na continuação do uso do finFET fora da tecnologia de processo de 5 nm. O Imec mostrou o Ge nFinFET com Gmsat / SSsat e PBTI recordes. Eles foram alcançados melhorando a substituição de material dielétrico alto.Também veremos se a tecnologia finFET pode ser expandida para 3 nm. Também não está claro se os chips de nanocamada aparecerão a tempo. Existem muitas incertezas e incertezas nesse cenário em mudança e não há cronograma para esclarecer a situação.