Localizado a bordo da espaçonave Apollo, o

computador de controle (Apollo Guidance Computer, AGC) ajudou o navio a chegar à lua e a pousar em sua superfície. O software AGC foi fisicamente tecido em uma memória

principal do núcleo de memória somente leitura [memória da corda principal]. Ken Shirrif e pessoas afins estão reconstruindo o AGC (foto abaixo), que não tem memória suficiente nos núcleos, em vez de quais caixas de simulador dessa memória estão instaladas. Essas caixas foram usadas durante o desenvolvimento do programa e os testes de solo, para que os engenheiros não precisassem piscar constantemente na memória. O simulador não possui documentação, então eu [o autor da entrada do blog / aprox. transl.] realizou sua análise de engenharia, montou a interface e, usando o simulador, lançamos programas em nosso AGC. No entanto, no processo, encontramos algumas dificuldades.

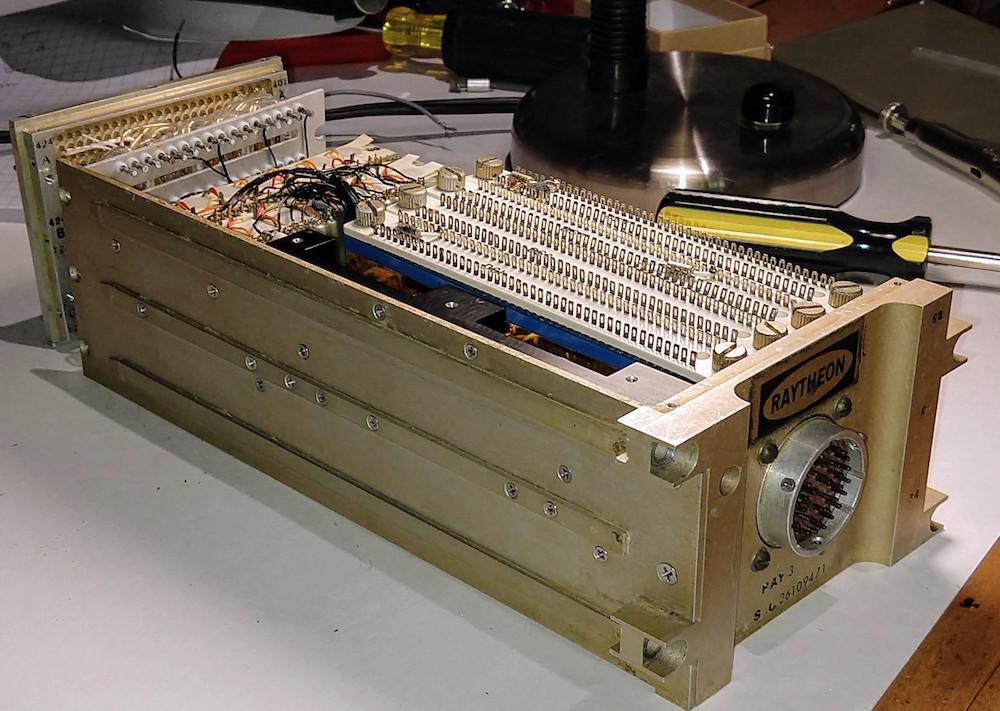

Computador AGC com a tampa removida. Você pode ver a placa-mãe com vários fios. Nos locais de memória, as caixas de simulação são visíveis. As placas de interface em primeiro plano são modernas.

Computador AGC com a tampa removida. Você pode ver a placa-mãe com vários fios. Nos locais de memória, as caixas de simulação são visíveis. As placas de interface em primeiro plano são modernas.Memória em vários núcleos costurados

O AGC tinha seis módulos de memória em vários núcleos costurados, cada um deles armazenando apenas 6 quilos de informações (cerca de 12 Kb). Os módulos de memória eram um pouco como cartuchos de ROM para um videogame e mantinham o software em uma forma constante, mas apagável. Os programas foram gravados tecendo fios através de núcleos magnéticos. O fio que passava pelo núcleo denotava o bit 1 e o bypass, o denotava o bit 0. Ao tecer 192 fios através ou ao redor do núcleo, era possível armazenar 192 bits, o que proporcionava uma densidade muito maior do que a memória regravável nos núcleos magnéticos, que armazenavam um bit por núcleo.

Memória em múltiplos núcleos costurados (Bloco I) com AGC

Memória em múltiplos núcleos costurados (Bloco I) com AGCCriar essa memória foi um processo minucioso que levou oito semanas e custou US $ 15.000 por módulo. Mulheres experientes passaram os fios manualmente, exibindo os núcleos um após o outro com uma agulha oca através da qual o fio era enfiado (foto abaixo). Eles foram auxiliados por um sistema automático que leu o programa a partir da fita perfurada e colocou um orifício acima da matriz de núcleos. O tecelão passou a agulha pelo orifício, conduzindo o fio sempre que necessário. Depois disso, a memória foi montada no módulo, juntamente com centenas de resistores e diodos, e preenchida com epóxi para garantir a confiabilidade no vôo.

Uma mulher pisca uma memória permanente, introduzindo um programa nela

Uma mulher pisca uma memória permanente, introduzindo um programa nelaSimulador de memória em núcleos costurados repetidamente

O processo de piscar de memória levou muito tempo e dinheiro; portanto, foi necessária uma alternativa durante os testes e o desenvolvimento. Em vez de núcleos costurados, a NASA usou seus simuladores, permitindo que o AGC baixasse dados de um sistema externo. Nosso AGC foi usado para testes no solo, por isso não tinha núcleos costurados, mas possuía seu simulador. Consiste em duas caixas conectadas aos conectores para núcleos costurados e cada caixa ocupa três slots de memória. Eles podem ser vistos no lado esquerdo do AGC na foto abaixo e possuem conectores militares redondos para conexão com um computador externo.

As caixas do simulador são instaladas no lado esquerdo do AGC, em vez dos módulos de memória real.

As caixas do simulador são instaladas no lado esquerdo do AGC, em vez dos módulos de memória real.Embora tenhamos documentação detalhada para o AGC, não foi possível encontrar a documentação para o simulador. Eu tive que aplicar a análise de engenharia, seguindo todos os esquemas e percebendo o que as caixas fazem. O estudo externo deles dá pouco. Em um lado de cada caixa, há um conector MIL-Spec para conexão com um sistema externo. Por outro lado, existem três grupos de 96 pinos conectados ao AGC. Cada grupo de contatos substitui um módulo de memória nos núcleos.

A abertura das caixas mostrou técnicas de montagem não padronizadas. Parcialmente nos contornos, foi utilizado um método estruturalmente semelhante ao

cordwood - os componentes foram

montados verticalmente com orifícios no bloco de metal. Nos dois lados da unidade, os contatos foram soldados aos fios. Outros circuitos nas caixas usavam circuitos integrados padrão (TTL 7400). Mas, diferentemente das modernas placas de circuito impresso, os chips eram montados dentro de módulos plásticos chamados “dipstik” [

Dipstik, eng. - sonda ] e foram enrolados com fios.

Layout do Cordwood

O layout “cordwood” foi usado ativamente no AGC para criar circuitos analógicos e também está presente nos simuladores de memória (veja a foto abaixo). Os círculos brancos no centro são as extremidades dos resistores e diodos montados verticalmente no módulo e com os contatos soldados nos dois lados. Os componentes estão bem compactados, como toras, e é por isso que esse layout é chamado de cordwood. Os transformadores de pulso estão localizados em grandes círculos cinzentos. Existem os mesmos do outro lado do módulo e os fios laranja, amarelo, vermelho e marrom saem dos orifícios. Fios pretos conectam o circuito do cordwood à lógica digital. Na parte superior da foto, você pode ver os pinos nos quais os diodos e os resistores estão montados, juntamente com a conexão com os contatos conectados ao AGC.

O principal objetivo do layout do cordwood é fornecer isolamento elétrico entre os circuitos AGC e as caixas do simulador de memória. Nos circuitos modernos, os optoisoladores executam essa função, mas os simuladores usavam pequenos transformadores de pulso. Como cada caixa recebe sinais projetados para três módulos de memória diferentes, muitos diodos combinam três sinais em um. Os resistores controlam a corrente que passa pelos transformadores de pulso.

Foi difícil entender a estrutura dos circuitos analógicos de cordwood. Em primeiro lugar, o componente não é visível, pois está integrado no módulo. Eu tive que usar um multímetro para entender onde eles estão. Em segundo lugar, como os contatos aparecem nos dois lados no layout do cordwood, passei muito tempo revirando a caixa em busca dos contatos certos. Por fim, não consegui encontrar uma maneira conveniente de desenhar um diagrama de layout de um cordão que não gerasse um labirinto de linhas.

Lógica digital e vareta de nível

O Dipstik foi um plug-in introduzido em 1968 para facilitar a prototipagem de circuitos integrados. Ele substituiu as placas de circuito impresso por um sistema de embalagem de dupla densidade.

A idéia estava no bloco de plástico do conector com a conexão dos contatos do invólucro na parte inferior para conectar o circuito. Os circuitos integrados foram montados em um suporte inserido no bloco de conectores. O suporte na parte superior tinha orelhas de solda para a instalação de componentes adicionais, como desacoplamento de capacitores. A foto abaixo mostra os módulos da vareta com um suporte puxado para fora. Cada titular abrigava 5 IPs. Os contatos do IC foram colocados entre os contatos do suporte e os contatos do bloco de conectores. Essa ideia parecia boa, mas no final não era confiável. Deepstick foi um projeto com falha.

A foto abaixo mostra os contatos conectados com a ajuda do enrolamento de arame na parte inferior das varetas. Foi extremamente difícil para mim rastreá-los, era impossível passar por cada postagem no mar de fios azuis idênticos. Eu tive que tocar tudo com um multímetro. Pude desenhar um diagrama esquemático e pensar no que ele faz. No total, cerca de 50 CIs foram usados no simulador.

A julgar pela rotulagem dos componentes, as caixas do simulador foram montadas em 1971. E, apesar de apenas alguns anos se passaram desde o design do AGC, as tecnologias nos simuladores já parecem mais avançadas, o que ilustra o rápido progresso da PI desde meados da década de 1960 até o início da década de 1970. O AGC foi montado com base em circuitos integrados simples, cada um dos quais contém duas portas NOR e lógica de resistor-transistor primitivo integrado (RTL). Nas caixas do simulador, já existem chips da série 7400 mais complexos, contendo mais de dez elementos na lógica transistor-transistor (TTL). Diferentemente dos ICs planos obsoletos no AGC, as caixas simuladoras usam chips no pacote DIP (pacote duplo em linha duplo), e esses casos ainda estão em uso.

Resultados da análise de engenharia

Depois de rastrear todos os contornos, percebi como o simulador funciona e desenhei os

diagramas . De fato, uma caixa decodifica o endereço do qual o acesso está sendo acessado e a segunda envia os dados necessários para o AGC (chamarei de “caixa de endereço” e “caixa de dados”).

A caixa de endereço recebe os sinais e os converte em binários. A tarefa não é simples, porque os sinais vêm na forma de pulsos de alta corrente e tensão de 14 V, projetados para alternar núcleos. Além disso, esses pulsos são separados no tempo, pois alguns trocam o núcleo em uma direção, enquanto outros voltam. Por fim, os pulsos enviados aos núcleos contêm não apenas um endereço, mas também um sinal para selecionar um dos 6 módulos e para selecionar um dos 12 threads no módulo.

A caixa de endereço usa conversores de pulso, convertendo pulsos de 14 V em sinais TTL. Ele contém um monte de lógica AND-OR para converter sinais em endereços binários (e isso não é trivial, já que cada módulo contém 6 quiloslovol, não é uma potência de dois, são necessárias muitas manipulações bit a bit). Os chinelos bloqueiam um endereço quando um estiver disponível. Finalmente, o circuito RC do multivibrador controla o tempo, determinando, com base em vários sinais, a disponibilidade do endereço e quando enviar o resultado ao AGC.

A caixa de dados é mais simples. Ele recebe 16 bits de dados de um sistema externo e envia sinais para amplificadores AGC, simulando sinais de milivolt do núcleo. Esses sinais são gerados por conversores de pulso. A caixa de endereço e a caixa de dados se comunicam através dos fios do backplane do AGC.

As caixas se comunicam com um sistema externo usando sinais diferenciais para eliminar o ruído de cabos longos. As caixas contêm reguladores LM109 de 5 V que fornecem TTLs. Uma caixa recebe um controlador de domínio não regulamentado através de um conector externo e envia um controlador de domínio não regulamentado para outro através de um backplane AGC (o que, para mim, é bastante estranho).

BeagleBone como uma interface

Tendo lidado com o trabalho do simulador, foi necessário criar uma interface capaz de fornecer dados do programa para o simulador. Eu usei o

BeagleBone , um pequeno computador de placa única baseado em Linux. A vantagem do BeagleBone é que ele possui microcontroladores rápidos que podem responder em tempo real às solicitações de memória do AGC.

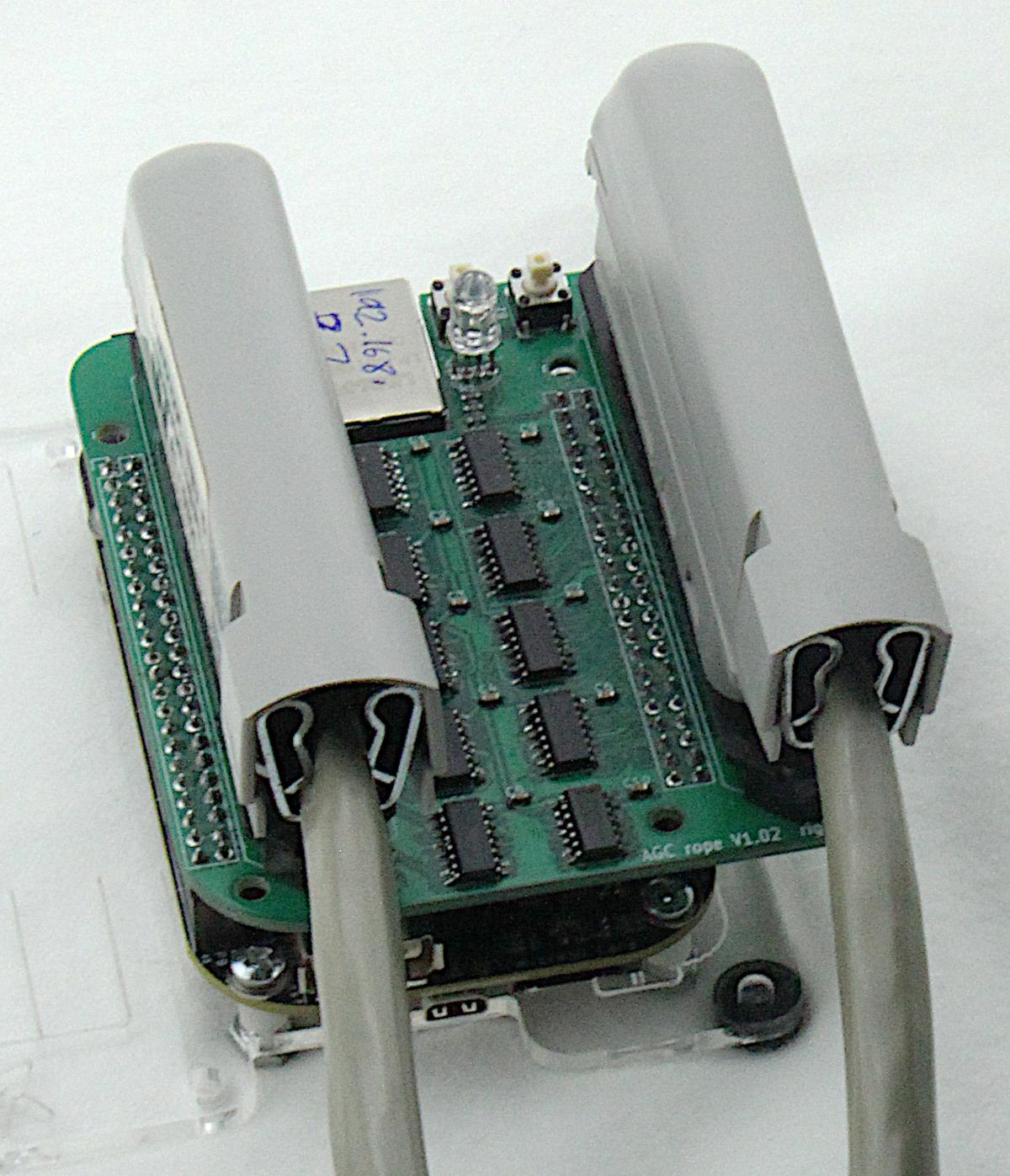

A interface é a placa presa no BeagleBone. Cada um dos dois cabos vai para o seu simulador de caixas.

A interface é a placa presa no BeagleBone. Cada um dos dois cabos vai para o seu simulador de caixas.Eu projetei uma placa de interface para conectar a um BeagleBone. É bem simples: os

receptores diferenciais lineares

AM26C32 que convertem os sinais diferenciais do simulador em sinais lógicos de 3,3 V para o BeagleBone e os drivers lineares diferenciais

AM26C31 para enviar sinais ao simulador.

Projetei o conselho no KiCad e encomendei a produção da

PCBWay , patrocinadora da restauração da AGC.

Eu escrevi um programa que roda em um microcontrolador BeagleBone, PRU. Esta é, em essência, uma máquina de estado, aguardando o endereço da caixa do simulador, aguardando o sinal de temporização, lendo a palavra da RAM do BeagleBone e enviando a palavra para o simulador. Postei o programa no

Github .

Problemas com o simulador

Os simuladores de memória em núcleos costurados repetidamente não foram montados de acordo com os padrões de computador de controle da Apollo e, como resultado, tive que demorar muito para depurá-los. Muitas conexões foram interrompidas, elas tiveram que ser soldadas novamente (não sei se elas se rompiam de tempos em tempos ou quando eu entendi o esquema de trabalho). Também encontramos um curto-circuito em uma vareta e um IC com defeito.

A maioria de todos os problemas ocorreu com varetas, pois muitos contatos se intercalavam entre varetas e IP. O problema era que os contatos do CI estavam localizados na forma de um sanduíche entre os contatos no suporte da vareta e o bloco em que foram inseridos. Os dipsticks plásticos dobram para fora, e é por isso que os contatos periodicamente não funcionam. Tendo dobrado as pernas do IP na forma da letra S, Mark conseguiu fornecer-lhes contato de ambos os lados, pelo menos por um tempo. Porém, depois de algumas horas, as pernas macias do CI dobraram para trás, os contatos começaram a funcionar mal novamente, por isso não tivemos uma solução a longo prazo para esse problema.

O problema mais interessante foi a

corrida de dois sinais do AGC, que deveriam parar simultaneamente. Eles alimentaram as duas extremidades da bobina do conversor de pulsos, que não deveria dar um sinal. No entanto, um sinal ficou atrás do outro, o que levou ao aparecimento de um impulso espúrio. Infelizmente, a lógica digital na caixa do simulador era assíncrona, esse impulso bloqueou o bit errado do endereço nos chinelos e, como resultado, ocorreu o acesso ao local errado na memória. Como resultado, rastreamos esse problema e instalamos capacitores adicionais que filtram o pulso. Infelizmente, pegamos capacitores muito grandes e, em outros casos, o sinal foi atrasado demais, o que levou ao aparecimento de outros erros. Em seguida, colocamos capacitores menores e finalmente conseguimos executar com êxito os programas no AGC usando simuladores de memória de núcleo antigos.

Conclusão

O computador de controle Apollo de bordo usa memória em vários núcleos costurados. Como seria impraticável refazer constantemente essa memória durante o desenvolvimento, foram utilizados simuladores. Fiz uma análise de engenharia do simulador e criei uma interface para sua operação usando o BeagleBone. Lançamos com sucesso os programas AGC por meio dessa interface. No entanto, o simulador de memória acabou sendo problemático e não confiável.

A @CuriousMarc fez um vídeo detalhando nosso trabalho com o simulador de memória: