Por fim, um

livro sobre o SystemVerilog foi lançado na Rússia

em um nível superior ao dos iniciantes . O livro descreve as tecnologias e técnicas solicitadas para entrevistas na NVidia, Intel, AMD, Apple e outras empresas eletrônicas: o uso de afirmações simultâneas e cobertura funcional, que agora exigem não apenas engenheiros de verificação, mas também designers de chips; o algoritmo do simulador com ciclos delta; explicação sã da análise de tempo estático; diagramas de comunicação de unidades de hardware através de filas de hardware; a implementação dessas comunicações usando máquinas de estados finitos com caminhos de dados, etc.

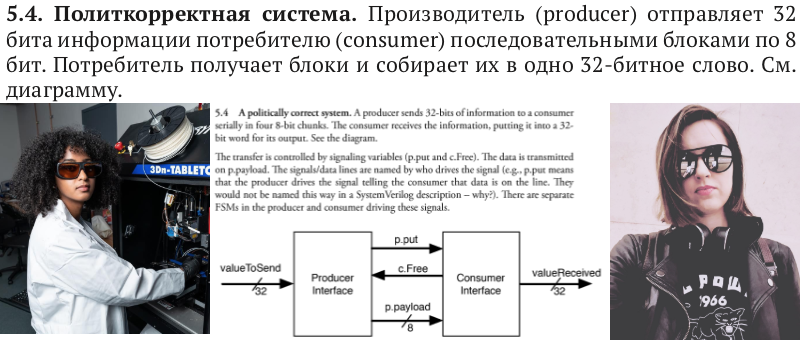

No capítulo sobre este último, o leitor russo pode ficar intrigado com a menção de um "sistema politicamente correto". O que isso significa? Provavelmente, isso é uma alusão ao

incidente ocorrido no condado de Los Angeles em 2003. As autoridades de Los Angeles pediram aos fabricantes, fornecedores e prestadores de serviço que parassem de usar os termos "mestre / escravo" para equipamentos de informática, pois um dos funcionários do condado era lembrado do passado dos escravos.

Agora, os autores da literatura técnica estão evitando os termos mestre / escravo. Os engenheiros afro-americanos também trabalham na América moderna (por exemplo, Sofia Mvokani, dos Camarões - na foto à esquerda), e o uso de termos antigos parece arcaico, como os termos “pan / slave” na literatura técnica ucraniana pareceriam em vez do “lead / lead” aceito ( “Líder / escravo” russo).

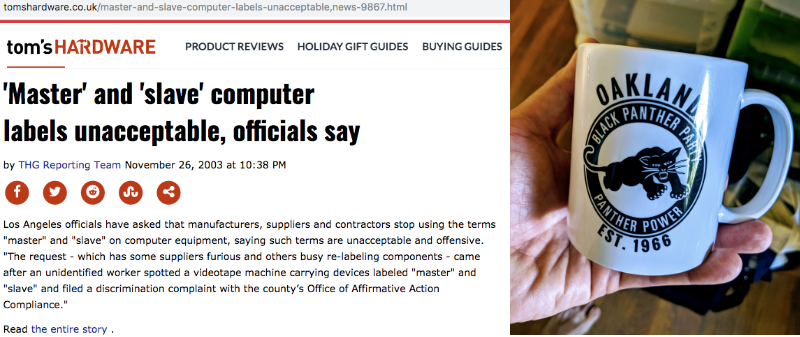

Não é a primeira vez que o tema da luta dos afro-americanos pelos direitos civis aparece na educação eletrônica russa. Por exemplo, Tatyana Volkova, uma renomada especialista em educação em eletrônica, veste uma camiseta com o emblema de "Panteras Negras", o movimento da Califórnia, que ao mesmo tempo considerou insuficiente o protesto pacífico e participou de protestos armados.

A imagem completa do emblema sob a pele de Tatyana Alexandrovna está oculta, mas principalmente vou falar sobre ciclos delta e máquinas de estado:

Abaixo está uma captura de tela do artigo sobre mestre / escravo e o prometido emblema Pantera Negra, após o qual passamos ao livro como tal.

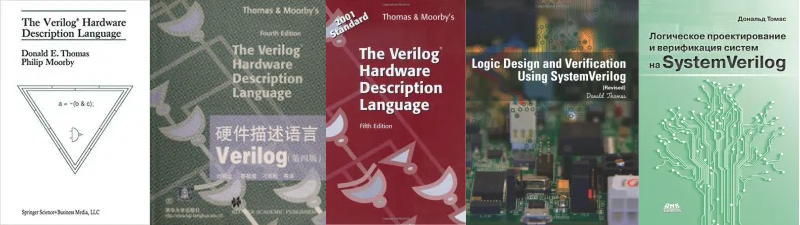

Antes de tudo, Donald Thomas, autor do livro

“Design Lógico e Verificação de Sistemas no SystemVerilog” (2019 em russo pela DMK-Press, 2016 em inglês) é o mesmo Donald Thomas, que é coautor de Philip Murbi e escreveu um livro em 1991 O Verilog Hardware Description Language de Donald Thomas e Philip Moorby. Então, em 1991, muitas empresas de eletrônicos ainda projetavam microchips à moda antiga, desenhando-os com o mouse na tela; as tecnologias de síntese lógica acabam de sair do laboratório para produção; as linguagens de descrição de hardware foram consideradas destinadas a escrever modelos e testes, e não códigos-fonte para a criação de circuitos finais; além do VHDL e do Verilog fechados naquela época, havia muitas linguagens pequenas e proprietárias, como Abel, CUPL, PALASM; e Intel e MIPS tinham linguagens de descrição de hardware internas.

Nesse ambiente, foi lançado o livro de Thomas e Murbi, que se tornou o mesmo para os projetistas de circuitos digitais dos anos 90, como o livro de Kernigan-Richie para os programadores de C e os livros de Bjarni Straustrup para os programadores de C ++. O livro sobreviveu a cinco edições - de 1991 a 2002, mas para a era dos iPhones era claramente insuficiente. E em 2016, Donald Thomas decidiu acompanhar e lançar um novo livro, no qual descreveu as principais inovações na linguagem e metodologia ao longo de 25 anos. Nos 25 anos em que a Verilog se tornou uma base comum para toda a indústria, foram escritos esquemas para tudo, desde os notórios iPhones e computadores de controle em Tesla até helicópteros militares russos.

A seguir, destacarei meus comentários com texto azul para separá-los das figuras do livro.

Mesmo antes do texto principal do livro, existe o pré-capítulo "Contexto: Design no nível das transferências de registros", para que um programador, aluno de escola ou, digamos, um amante de exercícios com placas de prototipagem, tire este livro da prateleira e entenda imediatamente o que está sendo dito e como ele pode usá-lo. Diz:Os sistemas digitais estão sendo produzidos com bilhões de transistores em um chip. Um amador, é claro, pode desenhar várias portas lógicas e conectá-las aos fios como uma especificação (para implementação em uma placa de ensaio), mas para projetos comerciais essa é uma história antiga ... Os sistemas modernos são especificados em linguagens de descrição de hardware, como o SystemVerilog.

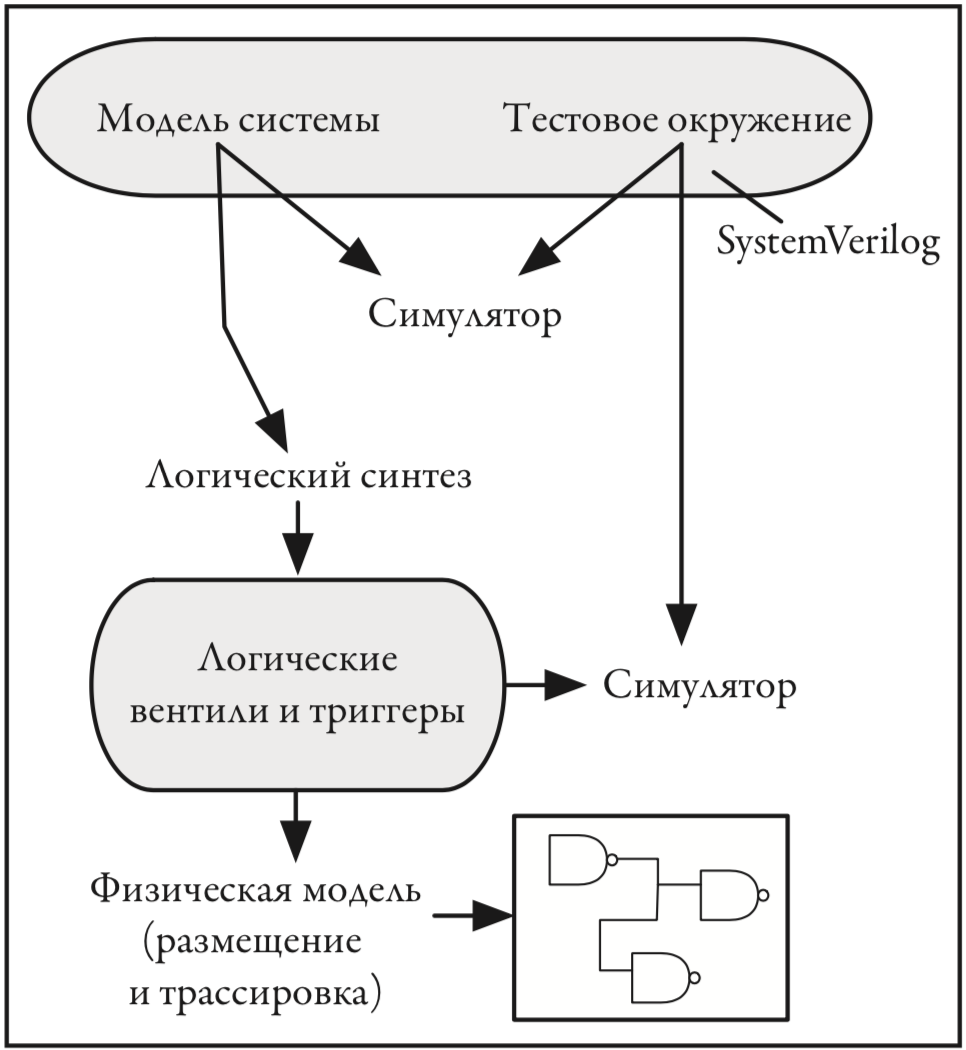

Ao mesmo tempo, aqui está uma figura tão simplificada para ilustrar como o texto no verbo se transforma em trilhas e transistores do microcircuito na fábrica:

A primeira palavra no livro após o prefácio é "simulador". Para entender as linguagens de descrição de hardware, você precisa estar ciente de que o subconjunto sintetizado do verílogo não é uma linguagem de programação, mas uma linguagem para descrever circuitos elétricos. Como, digamos, HTML não é uma linguagem de programação, mas uma linguagem para descrever páginas da web. Enquanto uma linguagem de programação deve ser compilada em uma cadeia de instruções do processador, uma linguagem de descrição de hardware deve ser convertida (em particular) em ferro de processador, como tal. Nesse caso, antes de passar para o ferro, o código na linguagem de descrição de hardware precisa ser verificado, para qual finalidade um intérprete especializado, chamado simulador, serve.

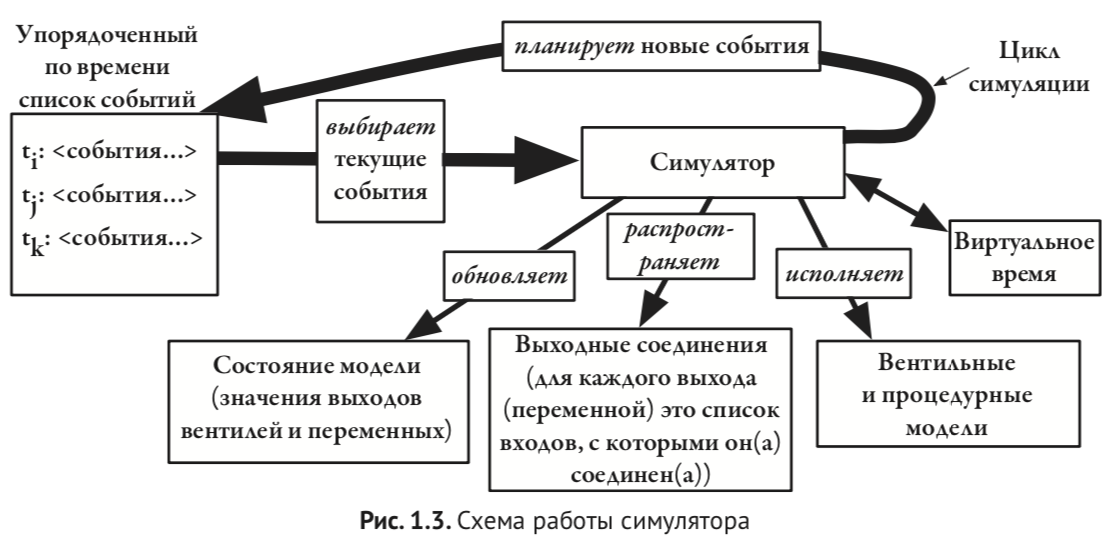

No início do livro, Donald Thomas mostra uma imagem simplificada do simulador e, no final do livro, esclarece e complementa:

O simulador possui filas de eventos e tempo simulado:

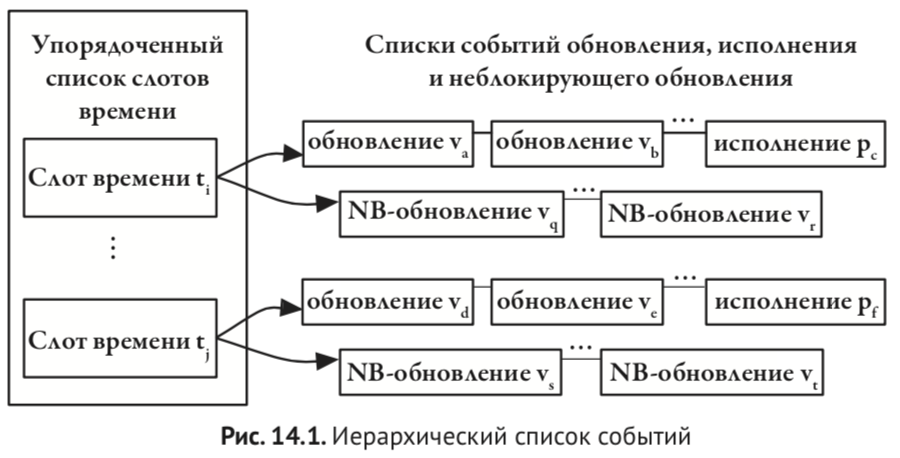

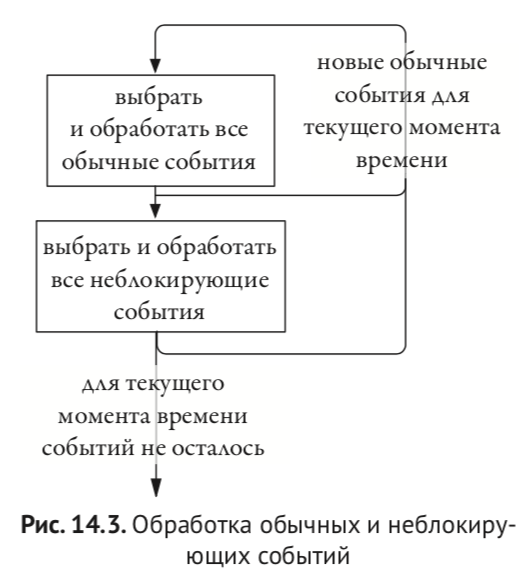

Um evento pode dar origem a um novo evento, tanto no momento atual da simulação (no ciclo delta atual) quanto no tempo futuro. No ciclo delta atual, todos os eventos gerados pelas chamadas atribuições de bloqueio são processados primeiro e, em seguida, os eventos gerados pelas atribuições sem bloqueio são processados. Isso é necessário para a simulação correta da semântica paralela da propagação de sinais elétricos no ferro:

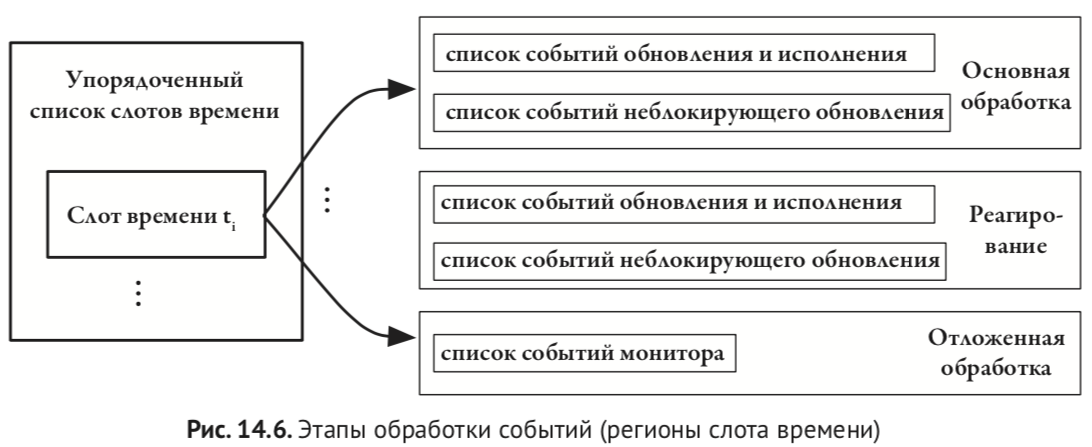

Além do subconjunto sintetizado do verílogo, há também um subconjunto não sintetizado. Pretende-se descrever o ambiente de teste e os testes, e agora pode ser considerado como um tipo de linguagem de programação. Para eventos e monitores do ambiente de teste, etapas adicionais do simulador são introduzidas:

O conhecimento exato do algoritmo do simulador é muito útil para evitar uma variedade de erros associados à chamada corrida (condição da corrida). Quando intervenho engenheiros, sempre peço que dêem um exemplo de condição de corrida em Verilog. Além disso, se para os jovens engenheiros de RTL Design e Design Verification, esse conhecimento é muito desejável, mas nem todos os aspectos são 100% necessários, ou seja, profissões nas quais o dinheiro é pago diretamente por esse conhecimento. Estou falando de programadores que trabalham nas equipes Synopsys VCS, Cadence IES e Mentor ModelSim.

Synopsys e Cadence são duas empresas localizadas na Califórnia a 15 minutos de carro uma da outra. Eles empregam apenas alguns milhares de pessoas, mas controlam o desenvolvimento de microcircuitos em todo o mundo - na Intel, Apple, Samsung, Huawei, mesmo em institutos secretos russos que fabricam chips para equipamentos militares.

Se os camaradas Putin, Rogozin e Vekselberg realmente querem introduzir a substituição de importações na Rússia, eles poderiam financiar o desenvolvimento do analógico russo Synopsys VCS (para simular o verílogo), do Synopsys Design Compiler (para a síntese lógica do verilogo) e do Synopsys IC Compiler (para a colocação física dos resultados da síntese lógica) ) Provavelmente existem vários milhares de programadores matematicamente experientes na Rússia.

Embora as licenças para esses produtos de software sejam bastante fáceis de serem quebradas, é difícil usá-las sem suporte. Se a Huawei estiver desconectada da Synopsys e da Cadence, elas terão, em certo sentido, pior do que quando desconectadas do Android e até dos núcleos ARM.

Sim, então aqui está o algoritmo refinado no final do livro de Donald Thomas. Se você não aprender de cor, é inútil intervir nos grupos de simulação da Synopsys, Cadence, Siemens / Mentor, Xilinx, e eles solicitarão que você o desenhe no quadro e sugira como otimizar um caso específico:

Após esclarecer a simulação no início do livro, Donald Thomas descreve a linguagem SystemVerilog como tal. Essa linguagem surgiu como o superconjunto Verilog em 2002, como resultado da fusão das linguagens Verilog-2001, Vera e Superlog, e com a adição de idéias da PSL (Property Specification Language), que foram transformadas em SystemVerilog Assertions (SVA).

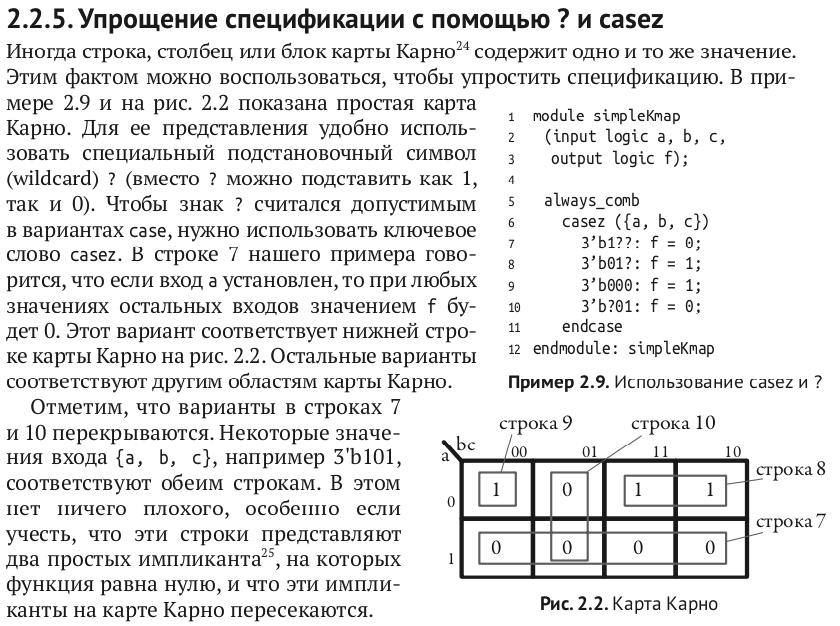

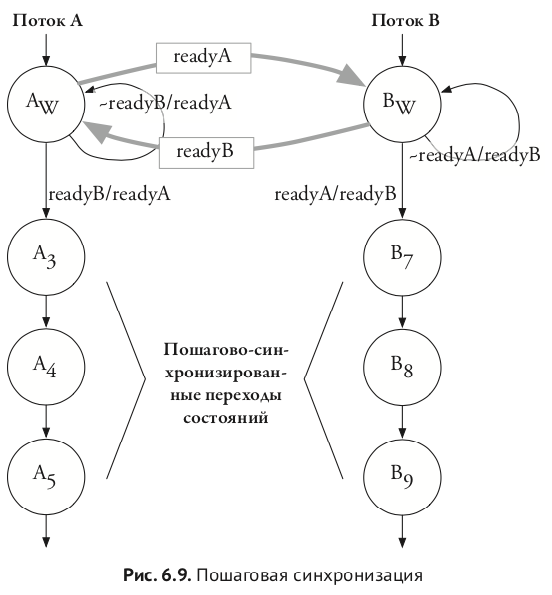

Donald Thomas acredita que você já aprendeu o básico do design digital em algum lugar e, portanto, tece no tecido narrativo várias peças conhecidas, como os cartões Carnot. Os mapas de Carnot foram utilizados para o design manual de circuitos na década de 1960, após o qual esse método foi substituído pela otimização automática da lógica, usando o algoritmo Quine-McClusky e o otimizador automático de lógica Espresso. Portanto, os cartões Carnot estão presentes em todos os livros didáticos da universidade sobre o design da lógica digital, mas parecem pairar no ar. E aqui Donald Thomas anexa os mapas de Carnot à vida de um designer em um verilo do século XXI:

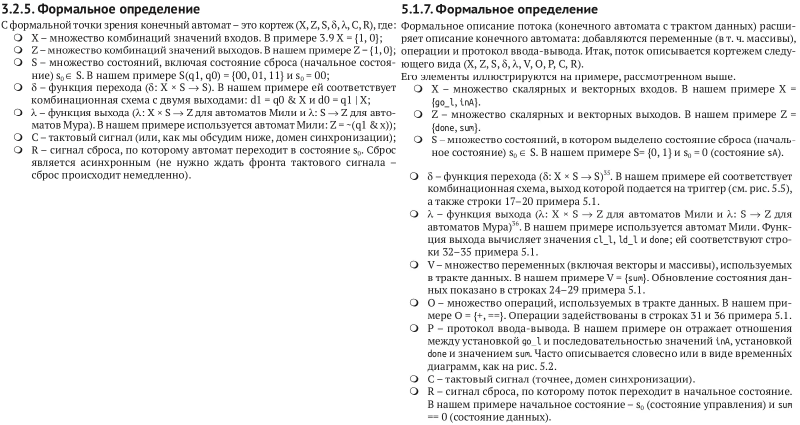

Além disso, Donald Thomas escreve sobre máquinas de estados finitos e fornece 1) uma definição matemática estrita; 2) diagramas; 3) código; 4) após o qual começa a expandi-las para máquinas de estados finitos com um caminho de dados - fluxos de hardware; 5) após o qual esses fluxos começam a interagir com ele, de acordo com protocolos simples "politicamente corretos" (veja acima) e usando filas de hardware.

Aqui está o código para um autômato simples com um caminho de dados que Thomas cita como primeiro exemplo:

Em seguida, Thomas tem um capítulo sobre análise de tempo estático. Nada de especial, mas mais limpo do que em muitos sites populares da Índia, "Como passar pela entrevista do VLSI". E também mais completamente do que em alguns livros sobre veril, que tediosamente mastigam a sintaxe da linguagem, mas realmente não mostram como usá-la.

Por que precisamos de análise de tempo estático? Em hardware real, em contraste com a ilusão de que o processador mostra ao programador, cada cálculo passa por um intervalo de tempo em que todo o lixo está nos fios - não apenas zeros e uns claramente calculados, mas também quaisquer falhas aleatórias, ou seja, falhas e geralmente valores não digitais na zona proibida. Por exemplo, se você tiver todas as tensões acima de 0,7 volts consideradas como uma unidade digital e todas as tensões abaixo de 0,3 volts como um zero digital, poderão aparecer 0,4 volts no fio.

No final, todos os sinais no circuito seguem seu próprio caminho e a situação se acalma, mas esse "no final" deve ser menor que o ciclo do sinal do relógio (relógio). Este ciclo é inversamente proporcional à frequência na qual o circuito opera (gigahertz, megahertz).

Se o resultado estabelecido de cálculos ou operações lógicas não cair no gatilho D (elemento mínimo de memória) no momento da abertura (intervalo em torno da mudança de um sinal), o estado do circuito se tornará lixo - o satélite ou o reator explodirá, o iPhone irá parar de atender as chamadas. Todo o projetista de equipamentos precisa conhecer não menos ironicamente que a lógica.

Por que a análise é estática? Nos anos 80, foi dinâmico - os atrasos foram esclarecidos por meio de simulação. Isso acabou não sendo confiável para circuitos com centenas de milhares, milhões e bilhões de transistores, e agora todos os atrasos são calculados estaticamente, com base na análise dos caminhos dos sinais após a síntese.

O sinal de clock também pode chegar a diferentes partes do chip com algum atraso, o que adiciona outra incerteza a essa cozinha que precisa ser eliminada (felizmente, não manualmente, mas com a ajuda de programas de árvore de síntese de clock e outros métodos):

No capítulo sobre fluxos, Thomas discute várias opções básicas de como máquinas de estados operacionais paralelos com caminhos de dados podem trocar informações, incluindo o uso de buffers e filas. Assim como no próprio projeto / circuito, no nível das transferências de registros, no modelo comportamental ou no ambiente de teste do circuito. Ao ler Thomas, é bom escrever e depurar exemplos para todos os casos dos protocolos descritos por ele. O fato é que eles gostam de escrever código sobre esses tópicos (uma pequena máquina de controle de estados finitos, fluxo de dados entre dois módulos, caminhos de dados em pipeline ou apenas codificar para uma fila de hardware) em um quadro negro ou em um computador durante uma entrevista de segundo nível em empresas eletrônicas. Se você puder escrever um exemplo para qualquer uma das combinações descritas por Thomas em 20 minutos com um código de 30 a 50 linhas, causará uma boa impressão. Difícil de aprender - fácil na batalha.

O ambiente de teste para roteadores (Fig. 8.3) com filas para várias portas é um exemplo popular usado para explicar as metodologias de verificação. Provavelmente porque algumas dessas metodologias foram inventadas pela Cisco e outras empresas que projetam chips para hardware de rede.

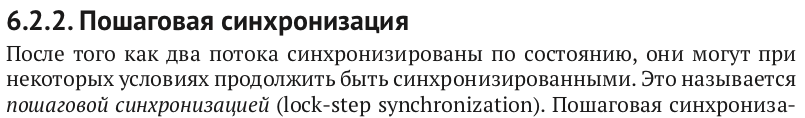

No capítulo 6.2.2. Thomas descreve uma das opções para a interação de threads - sincronização passo a passo (Lock-step). Uma das aplicações de bloqueio é o sistema de alta confiabilidade, por exemplo, em eletrônicos automotivos. Um caso especial: dois processadores podem executar o mesmo programa com um atraso de vários ciclos e, durante essa execução, um circuito especial pode verificar se eles têm os mesmos resultados.

Thomas estava claramente preocupado com a confiabilidade, pois além do bloqueio, ele cita o uso do CRC, um código ciclicamente redundante para detectar erros na transferência de dados. Ao mesmo tempo, Thomas explica como calcular o CRC usando o LFSR, um registro de troca de feedback linear. Isso e outro precisam ser capazes de um jovem engenheiro. Essa é a vantagem do livro de Thomas - embora nem sempre seja profundo, ele aborda muitos tópicos e mostra onde cavar:

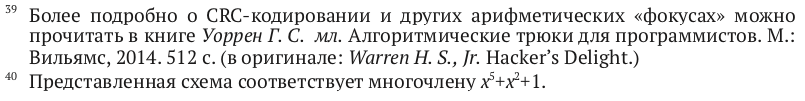

Ao descrever a CRC, Thomas se refere a um livro muito interessante e incompreendido na Rússia por Hacker's Delight :

Donald Thomas, em seu novo livro, aborda três tecnologias que não estavam no livro antigo:

- Geração automática de transações pseudo-aleatórias com regras restritas (transações aleatórias restritas / solucionadores de restrições).

- Contabilizando a cobertura de cenários interessantes que surgem durante o bombardeio de um projeto por transações aleatórias limitadas, cobertura funcional.

- A linguagem das declarações da lógica temporal (asserções simultâneas) e seu uso na simulação e na prova automática das propriedades do projeto usando programas formais de verificação.

Essas três tecnologias entraram no setor de maneira positiva apenas no século 21, mas entraram com firmeza. No início, todos eles eram usados para criar ambientes de teste por engenheiros de verificação, mas agora o conhecimento da cobertura funcional e da Linguagem de asserção temporal (SystemVerilog Assertions - SVA) também exige designers. Thomas tem um certo mínimo que o ajudará a não ser cortado em uma entrevista por telefone, mas, para o trabalho real, você precisa saber muito mais. Além disso, não apenas a linguagem das declarações temporais como tal, mas também a prática de depurar com sua ajuda as máquinas de estados finitos paralelos geradas pelo simulador para cada declaração, bem como o uso de programas formais de verificação. A verificação formal baseada em asserção nos últimos anos foi fortemente implementada na Apple, AMD e outras empresas desse tipo.

Tenho um amigo que baixou

este livro sobre a linguagem das declarações temporais e o estudou todas as férias de Ano Novo, em vez de uma viagem ao Havaí com meninas. A partir daqui, você pode entender como as SystemVerilog Assertions (SVA) são importantes para a carreira e a indústria. É verdade que, para completar, devo mencionar que ele é filho de emigrantes de Taiwan, e eles têm uma atitude mais severa em relação a essas coisas do que os russos.

Eis como Thomas lida com a geração de transações pseudo-aleatórias (uma transação com campos de margem e sua restrição usando a construção de restrição):

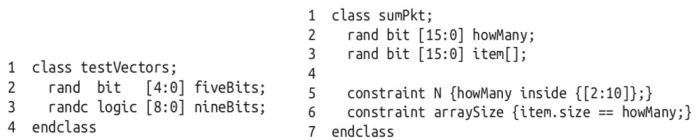

E aqui está como Thomas se relaciona à cobertura funcional - grupo de cobertura / ponto de cobertura / bandejas, levando em consideração combinações de várias coberturas variáveis (cruzadas), usando bandejas curinga, intervalos de valores e cobertura de transição em máquinas de estado:

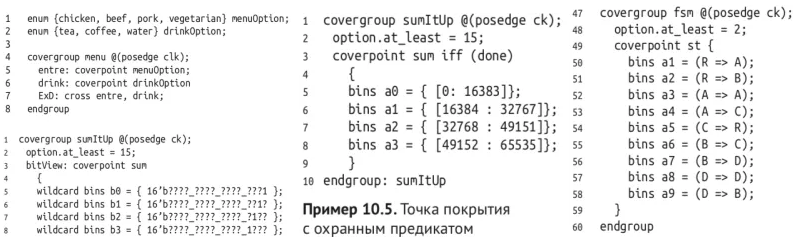

Aqui está um exemplo da declaração temporal mais simples "se q for verdadeiro na extremidade positiva do sinal do relógio, a sequência s2 deve ser executada através do ciclo, no qual r é verdadeiro primeiro e s está em mais três ciclos":

O que ler antes e depois do livro “Projeto Lógico e Verificação de Sistemas no SystemVerilog” de Donald Thomas?

Se você não entende nada do meu post, tente ler o livro

“Circuitos Digitais e Arquitetura de Computadores” de David Harris e Sarah Harris . O livro Harris & Harris pode ser entendido por todos que sabem ler e contar, desde que o leitor tenha motivação. O livro começa no ensino médio - voltagens, números binários - e termina com o design de seu próprio processador em risco.

Spoiler: David Harris e Sarah Harris não são marido e mulher, nem mesmo irmão e irmã. São apenas nomes que acidentalmente começaram a trabalhar como professores na mesma universidade, durante a qual escreveram um livro.

Aqui à esquerda na foto está a garota Irina, do Novosibirsk Academgorodok, segurando a edição em inglês da Harris & Harris, e à direita está a edição em russo.

Após o livro de Donald Thomas, recomendo o download de artigos de Cliff Cummings. Ele é o treinador de verbos mais famoso para síntese e verificação. Ao ler o livro de Donald Thomas, tive a idéia de "muitas vezes seria bom inserir tal e tal peça de Cliff Cummings" para completar.

Cliff leva de US $ 1.000 a US $ 3.000 para cada aluno nos seminários, dependendo da duração do seminário (do dia para a semana), e as empresas eletrônicas pagam para melhorar a qualidade de seus engenheiros que não são bem treinados nas universidades. Mesmo em Stanford, infelizmente, nem todo mundo aprende isso - eu tinha um estagiário em Stanford, eu sei disso por ele. Se você baixar todos os artigos gratuitos de Cliff Cummings depois de ler Donald Thomas, economizará todo esse dinheiro.Esses dois artigos são obrigatórios - eles gostam de perguntar em todos os lugares da entrevista:Técnicas de Design e Verificação do Clock Domain Crossing (CDC) Usando Técnicas de Simulação e Simulação de Verilog do Sistemae Técnicas de Síntese para Projeto FIFO Assíncrono com Comparações de Ponteiros AssíncronosÉ aconselhável ler estes três artigos, especialmente sobre a remoção de uma redefinição assíncrona, a recodificação de estados FSM e o estilo FSM "case (1'b1) // synopsys parallel_case ... state [STATE_N]: ...", que há muito tempo é usado em chips de alta velocidade. Sun Microsystems, e continua a ser usada hoje:Asynchronous & Synchronous as técnicas de projeto reset - Part Deuxcodificação e as técnicas de script para o FSM Designs a Síntese, com-otimizado, Glitch-the Free the Saídassintetiz�eis the Machine Solution design Estado Finite: Usando as técnicas a nova SystemVerilog 3,0 MelhoriasE aqui está um artigo curioso, onde você verá a falta de pensamento do verílogo, que permanece desde a década de 1980. Embora agora, na era da análise de tempo estático, isso não seja tão relevante, mas os atrasos inerciais e de transporte às vezes são mencionados na literatura e no código, e você deve saber como modelá-los:Métodos corretos para adicionar atrasos a modelos comportamentais da VerilogEsse sou eu com Cliff Cummings: