Se você pensou que a "gangue" da Intel é a mais leal defensora

da lei de Moore , provavelmente não ouviu como Philip Wong está se espalhando sobre esse assunto. Wong, vice-presidente de pesquisa corporativa da Taiwan Semiconductor Manufacturing Corp (TSMC), fez uma apresentação em uma recente conferência Hot Chips afirmando que a lei de Moore não está apenas viva e bem, mas com um conjunto bastante diversificado de truques tecnológicos, ainda não é verdade menos de três décadas.

"Ele não está morto", disse ele aos presentes no Hot Chips. "Ele não diminui a velocidade, nem tosse."

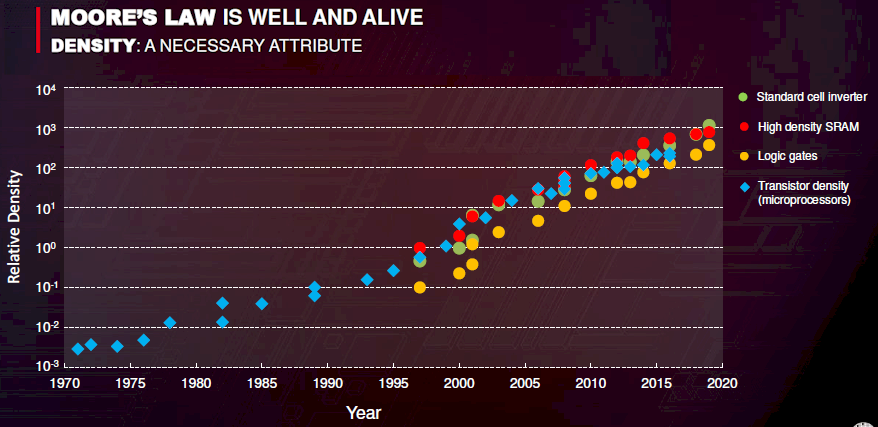

Ouça Wong, então a única ação necessária para manter a lei de Moore é melhorar a densidade. E embora ele admita que a frequência do relógio repousou no seu teto, marcando o fim

da lei de escala de Dennard , ele diz que é a densidade dos transistores que melhorará a velocidade e a eficiência energética.

A lei de Moore está viva

A lei de Moore está vivaPor fim, não importa quanta densidade mais alta seja alcançada. Wong acredita que o principal é que as empresas podem colocar mais transistores em um volume menor com melhor eficiência energética. No curto prazo, isso pode ser conseguido da maneira antiga e comprovada, ou seja, aprimorando a tecnologia de fabricação do CMOS, para produzir transistores com um comprimento de porta menor.

O TSMC já dominou a tecnologia de processo de 7 nm e está avançando para 5 nm. Wong disse que o ecossistema de desenvolvimento de tecnologia de processo de 5 nm já está pronto e a empresa já começou a produção de amostras de risco - ou seja, a tecnologia de processo e as ferramentas de desenvolvimento estão prontas e os substratos de trabalho estão sendo produzidos. Na última reunião de acionistas, a TSMC anunciou que planeja iniciar a produção em massa de chips a 5 nm no primeiro semestre de 2020. Acontece que os planos da empresa já incluem uma tecnologia de processo de 3 nm.

Mas toda essa tecnologia é baseada em chips

planares [planos], e Wong admite que essa abordagem acabará por diminuir de escala. "Se seguirmos o caminho do aumento bidimensional, já alcançamos várias centenas de átomos e logo todos os nossos átomos se esgotarão", explicou ele.

Mas isso não significa o fim do aumento da densidade. Ele observou que algumas inovações na indústria de semicondutores apoiavam um gráfico de densidade ascendente, mesmo no final do dimensionamento de Dennard. Em particular, a tecnologia do silício tensionado e

do dielétrico high-k apareceu e, em seguida, o FInFet (Fin Field Effector Transistor), a tecnologia das estruturas tridimensionais, foi seguida. Agora, para ir além dos 7 nm, a tecnologia DTCO (Design Technology Co-Optimization) está sendo investigada.

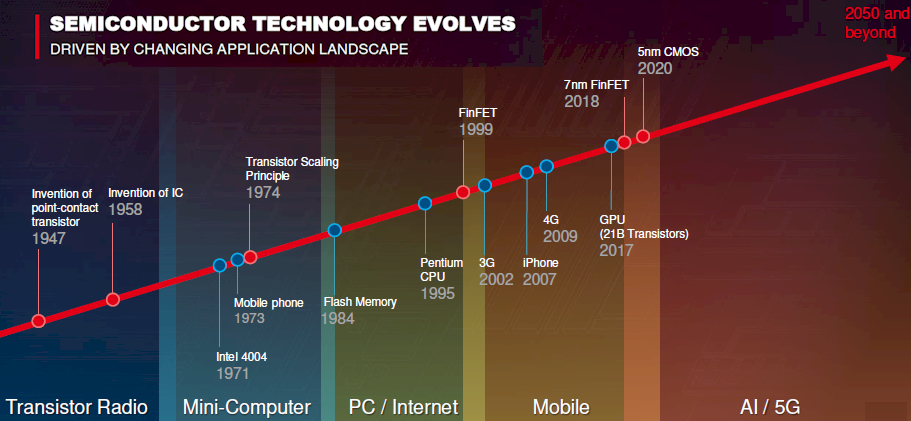

Todas essas inovações ocorreram porque era necessário desenvolver novas plataformas de computação que exigissem hardware mais rápido e com maior eficiência energética. Essa evolução gerou minicomputadores na década de 1970, PCs na década de 1980, Internet na década de 1990 e hoje dispositivos móveis. Cada estágio exigiu um aumento na densidade através da melhoria na fabricação de semicondutores. Wong acredita que os seguintes pedidos virão de inteligência artificial e 5G.

Evolução da tecnologia de semicondutores

Evolução da tecnologia de semicondutoresQue inovações serão necessárias para garantir que o Partido da Lei de Moore não pare?

No curto prazo, a densidade computacional geral e a densidade da memória aumentarão o uso de chipsets usados para criar caixas com vários chips de estruturas 2.5D, mesmo que os próprios chips não fiquem mais densos. Wong disse que esse processo já está tornando a tecnologia de processo específica de um chiplet individual um parâmetro menos importante do que a capacidade de integrar esses componentes em um único pacote.

O TSMC possui sua própria versão do chassi 2.5D com tecnologia CoWoS (Chip-Wafer-on-Substrate) (Embedded Multi-die Interconnect Bridge, ou EMIB, da Intel compete com esta tecnologia). O CoWoS permite criar gabinetes com vários chips, consertar chipsets e uma memória adequada no interposer e conectá-los usando os contatos verticais do TSV. A implementação mais interessante do CoWoS é o Nvidia Tesla V100 GPU Accelerator, no qual o GV100 GPU é embalado com alta largura de banda de memória (HBM). Mais chipsets estão sendo integrados pela Intel, AMD e Xilinx.

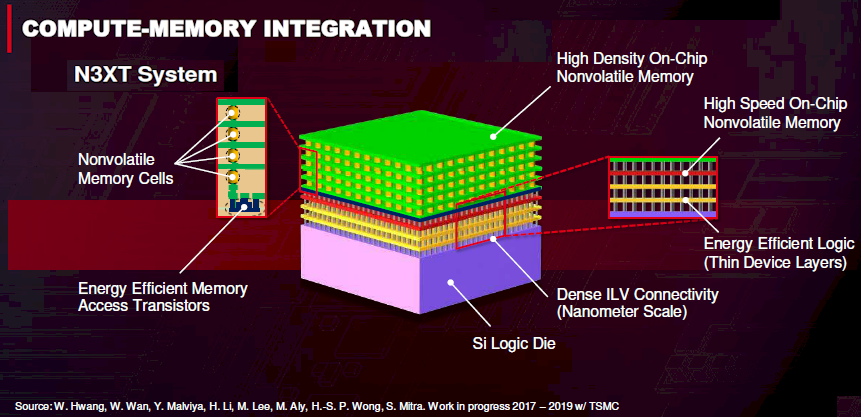

Mas as possibilidades de 2.5D para aumentar a densidade não são ilimitadas. Uma solução mais escalável exigirá tecnologias de posicionamento de transistor verdadeiramente tridimensionais. Para isso, de acordo com Wong, a tecnologia tridimensional monolítica N3XT é mais adequada com base em novos materiais e forte integração da memória com a lógica. O N3XT, a "tecnologia de nanoengenharia de sistemas de computação", é discutida na academia desde 2015, mas agora que empresas como a TSMC começaram a levar isso a sério, há uma boa chance de comercialização.

Wong mostrou slides com diagramas de como esse dispositivo pode parecer. Consiste em camadas de lógica de eficiência energética (amarela), memória de alta velocidade (vermelha) e memória não volátil de alta capacidade (verde), dispostas alternadamente uma acima da outra. E tudo isso assenta em um cristal lógico comum de silício (roxo).

Sistema N3XT

Sistema N3XTO principal aqui é combinar as várias camadas através do ILV, Inter-Layer-Via (acesso vertical entre camadas). Ao contrário de um TSV à escala micrométrica, o ILV pode ser formado em escala nanométrica. Embora essa seja uma parte extremamente importante da tecnologia N3XT, a Wong não pôde falar muito sobre isso. É óbvio, no entanto, que o TSMC está trabalhando de perto e já registrou várias patentes relacionadas a ele.

Em chips tridimensionais, a intercalação de memória e lógica é muito importante, pois permite reduzir a distância entre eles, garantindo alta taxa de transferência e baixa latência de transferência de informações, o que será necessário para aplicativos como AI e 5G. No CMOS, memória e lógica não podem ser intercaladas, pois a gravação de transistores lógicos requer uma temperatura da ordem de 1000 graus Celsius, o que destruiria as camadas vizinhas na produção. Requer algo que possa ser fabricado em temperaturas da ordem de 400 graus.

Acontece que, nos últimos anos, os pesquisadores estudaram novos materiais que parecem adequados para a produção de transistores de alta velocidade a temperaturas relativamente baixas. Ao contrário dos materiais de silício usados atualmente na produção, as monocamadas de metais de transição dichalcogeneto (DTM) são usadas lá com base em elementos como molibdênio, tungstênio e selênio.

Os materiais de DTM demonstram alta mobilidade dos portadores de carga - os elétrons viajam através deles com grande facilidade - com canais estreitos. O que é conveniente, são necessárias apenas essas características para criar transistores com um tamanho inferior a 2-3 nm. Wong disse que o laboratório TSMC está testando substratos experimentais de DTM com base em dissulfeto de tungstênio.

Outro candidato para nanomateriais são os nanotubos de carbono. Wong disse que suas variações experimentais foram feitas, mostrando um bom comportamento material como um semicondutor. Já foram montados protótipos funcionais de lógica e SRAM baseados em nanotubos de carbono, incluindo a variante RISC-V de pesquisadores do MIT.

Quanto à memória, de acordo com Wong, os candidatos mais prováveis à integração tridimensional serão: SST-MRAM (memória de acesso aleatório magnetorresistivo de torque de transferência de rotação, memória de acesso aleatório magnetorresistente que usa transferência de momento de rotação eletrônica para registrar);

Memória de mudança de fase PCM;

memória resistiva de acesso aleatório ReRAM; memória baseada na metalização programável da célula CBRAM; Memória de

acesso aleatório ferroelétrico FERAM. Tudo isso é memória não volátil com acesso aleatório, que não requer a operação de apagar uma célula antes de gravar novas informações nela. Algumas opções já estão no mercado - Everspin MRAM, Samsung MRAM, Crossbar ReRAM e Intel 3D XPoint (que, segundo a maioria, é uma variante do PCM).

Novos tipos de memória

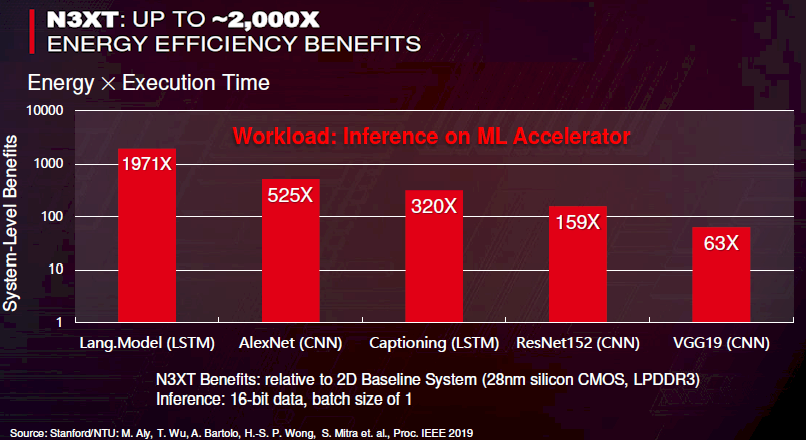

Novos tipos de memóriaOs pesquisadores simularam o desempenho dos dispositivos N3XT e os compararam aos chips bidimensionais tradicionais com aproximadamente as mesmas capacidades de lógica e memória. De acordo com suas pesquisas, onde vários métodos para medir a velocidade dos algoritmos de aprendizado de máquina foram usados, os dispositivos da tecnologia N3XT mostraram-se 63-1971 vezes mais eficientes do que os bidimensionais.

A vantagem do N3XT em relação aos sistemas bidimensionais

A vantagem do N3XT em relação aos sistemas bidimensionaisIsso parece promissor. Mas Wong não divulgou como exatamente essas tecnologias nos próximos 30 anos serão capazes de manter a velocidade do aprimoramento da tecnologia necessária para a lei de Moore. Por exemplo, a transição para novos nanomateriais nos dará um aumento único na densidade de transistores em relação aos componentes bidimensionais. Mas aí, no final, encontraremos restrições atômicas.

Teoricamente, se você pode dobrar a altura dos dispositivos tridimensionais a cada 18 meses, pode obter um aumento na densidade por área de superfície quadrada. Obviamente, para dispositivos móveis e embarcados, essa abordagem rapidamente se tornará muito complicada, e os chips para computadores nos data centers após sete a oito gerações ficarão em um teto de 4 metros.

Para que tudo continue funcionando por várias décadas e que a densidade continue a se encaixar na curva da lei de Moore, outras inovações técnicas não mencionadas por Wong precisarão ser desenvolvidas. Mas se você produz chips como o TSMC, precisa aceitar que os pesquisadores constantemente ofereçam novos candidatos a tecnologias que só precisam de solicitações de tarefas novas e mais exigentes para entrar no mercado. E se você se lembra da história, essas tarefas certamente aparecerão.