1. Introdução

Uma vez eu precisei implementar um pequeno bloco de CAM (memória associativa). Depois de ler como o Xilinx faz isso no BRAM (blocos de memória estática) ou no SRL16 (registros de deslocamento de 16 bits), fiquei um pouco triste, pois suas implementações ocupavam muito espaço. Eu decidi tentar fazer isso sozinho. A primeira opção foi a implementação da testa. Olhando para o futuro, chegou quase a mim imediatamente e, bem, a frequência alvo para o design era de apenas 125 MHz.

Arquitetura

Para começar, considere a declaração do problema. Portanto, precisamos de um pequeno CAM com uma largura de palavra de 8 a 64 bits e uma profundidade de 16 a 1024 palavras. Eu precisava de uma pesquisa binária no CAM, mas, mais tarde, verificou-se que criar TCAM (memória associativa ternária) a partir dele é bastante barato em termos de recursos e afeta levemente o tempo. O limite de frequência mais baixo é de 125 MHz na família Kintex7 . Vamos começar! Nosso CAM será composto dessas linhas, cada uma das quais corresponderá a um endereço e armazenará uma palavra:

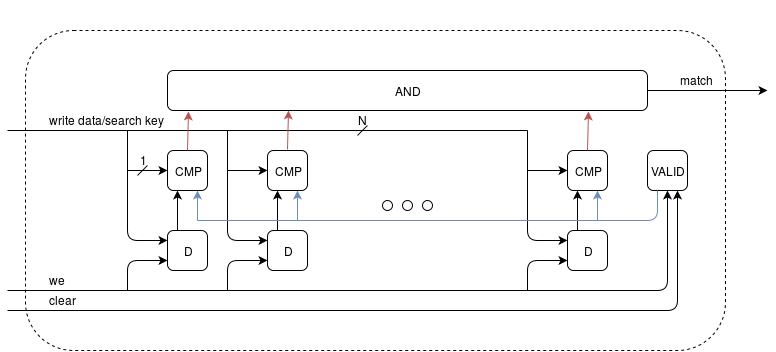

Figura 1. A estrutura de uma linha do CAM

Na Fig. 1, D é um gatilho D regular para armazenar dados; o número desses gatilhos na linha corresponde à largura da palavra de dados de entrada no CAM. VÁLIDO - D-trigger, que armazena '1' se os dados na linha forem relevantes. O CMP é um comparador que compara o valor do bit do barramento da chave de pesquisa correspondente se VALID = '1'. write data - escreve o barramento de dados , conectado bit a bit ao D correspondente (largura da palavra N - CAM), escrevemos sinalizador, limpamos - redefinimos VALID (invalidação da linha de dados). AND - saídas AND lógicas dos comparadores, o sinalizador de correspondência se transforma em '1' se a pesquisa nesta linha for bem-sucedida.

Portanto, temos uma linha na qual podemos pesquisar. Agora combine-os:

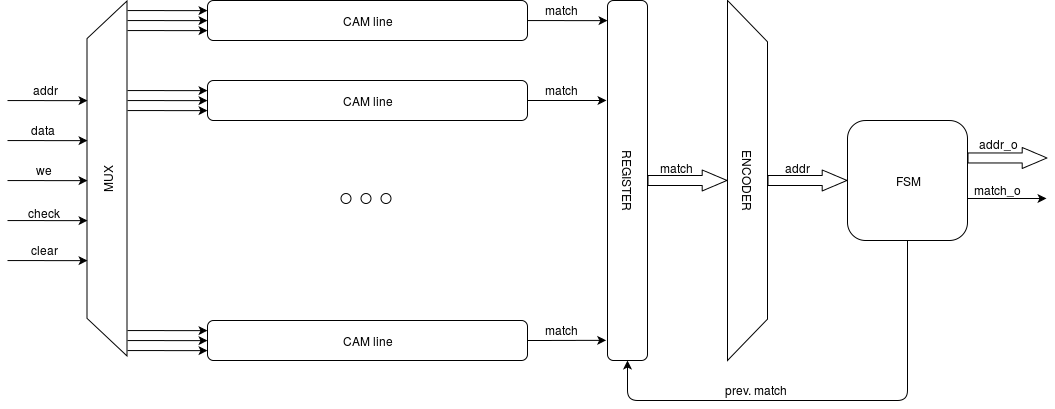

Figura 2. Estrutura CAM

Na Fig. 2, CAM_line é a própria linha CAM da Fig. 1, MUX é o multiplexador de endereço de entrada, MATCH REGISTER é um registro que armazena valores de flag de correspondência , ENCODER é um decodificador que converte o barramento de correspondência no endereço de correspondência mais baixo encontrado. O FSM é uma máquina de controle de estados finitos, que é anterior. match remove de MATCH REGISTER o bit correspondente ao endereço enviado, para que ENCODER alterne para o próximo endereço encontrado. A interface do nosso CAM será a seguinte:

Tabela 1. Interface CAM

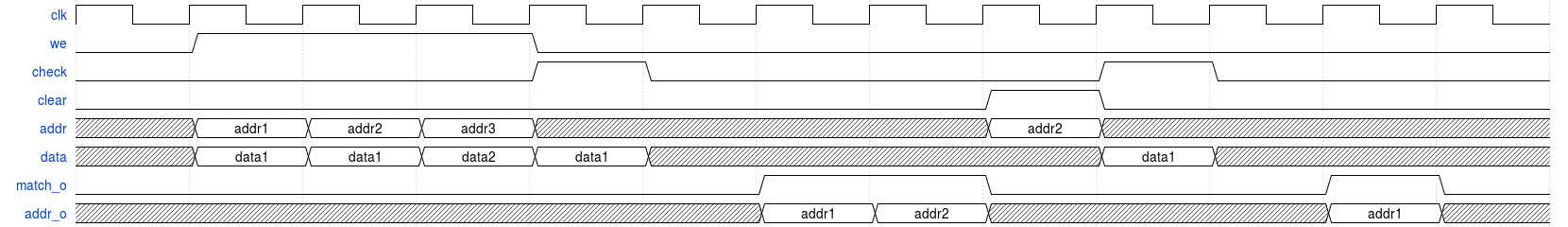

Abaixo, na Fig. 3, está um diagrama de tempo da operação desta interface, que mostra primeiro a gravação de três palavras no CAM, depois uma pesquisa bem sucedida, apagamento e pesquisa novamente:

Figura 3. Diagrama de tempo da interface para o CAM

Então, temos uma descrição do CAM, vamos para a síntese.

Síntese

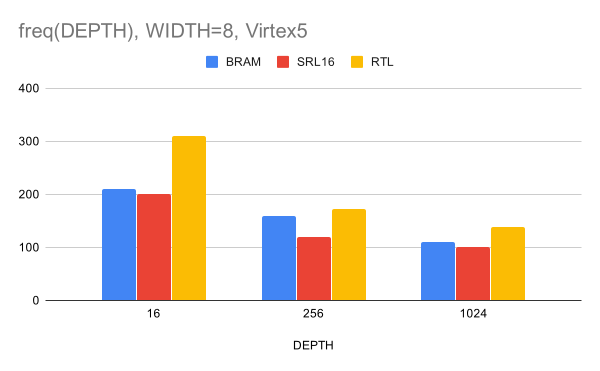

Vamos sintetizar no Xilinx ISE para comparar os resultados com os obtidos no XAPP1151 .

Figura 4. Dependência de frequência após XST (sintetizador como parte do ISE) na profundidade do CAM para largura de barramento de dados de 8 bits

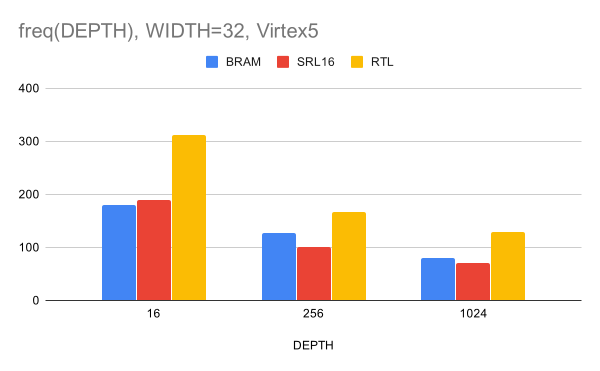

Figura 5. Frequência após profundidade XST versus CAM para largura do barramento de dados de 32 bits

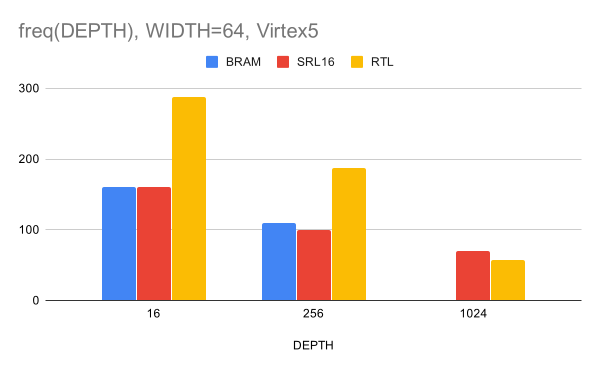

Figura 6. Frequência após profundidade XST versus CAM para largura do barramento de dados de 64 bits

Na Fig. 6, não há dados para o Virtex5 , pois o CAM desse tamanho não se encaixava no BRAM existente. Também observamos que, para uma largura de 64 bits e uma profundidade de 1024, nosso resultado foi um pouco pior que o da implementação no SRL16. Agora vamos à síntese do Vivado para o XC7K325T . Os resultados são os seguintes:

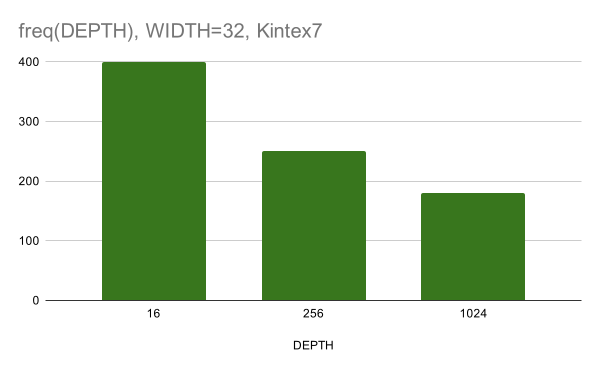

Figura 7. Dependência de frequência após PnR (colocação de blocos no chip e rastreamento de sinal) na profundidade do CAM para uma largura de barramento de dados de 32 bits

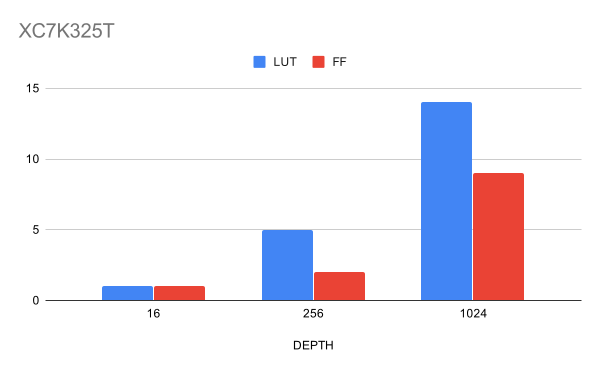

Figura 8. Utilização de recursos para várias profundidades de CAM para uma largura de dados de 32 bits em%

É importante notar que os resultados no Vivado foram obtidos após o PnR, o que significa que o design não tem dificuldades em rastrear.

TCAM

Como mencionado acima, obter essa abordagem do CAM TCAM não era um problema específico. É suficiente adicionar um barramento de mascaramento de dados para bits de dados e distribuí-lo pouco a pouco em comparadores, para que, ao comparar dados com uma chave, eles levem em consideração seu valor. Essa mudança não levou a uma queda na frequência ou a um aumento sério dos recursos consumidos; por isso, adquirimos o TCAM gratuitamente.

Conclusões

Assim, conseguimos concluir a tarefa. O design resultante permite que a 7ª família Xilinx FPGA receba CAM suficientemente grande com uma frequência acima do alvo 125 MHz. O resultado da comparação com o XAPP1151 foi inesperado para mim, presumi que a implementação no BRAM, embora seja muito cara em termos de recursos, ultrapassará a implementação frontal em frequência. No entanto, não celebre a vitória tão cedo, este documento descreve o núcleo IP Xilinx CAM, que permite, por exemplo, obter CAM com profundidade de células 32K e frequência de 155 MHz, com base no BRAM. Provavelmente, esse resultado pode ser alcançado na versão proposta no artigo, adicionando os estágios do pipeline ou coletando CAM grande de pequenos, mas não posso prever imediatamente se ele se encaixará no chip. No futuro, tentarei implementar algo semelhante no BRAM, mas, por enquanto, obrigado por sua atenção.