A colocação de chipsets nus em uma rede de silício permitirá criar computadores menores e mais poder de processamento

A necessidade de tornar cada dispositivo cada vez menos, enquanto outros cada vez mais, tem sido o principal motivador da inovação em eletrônicos. A primeira opção se manifesta em andamento, desde laptops a smartphones, depois a relógios inteligentes, fones de ouvido inteligentes e outros eletrônicos "invisíveis". A segunda opção determina a configuração dos data centers modernos - monstros de megawatt que preenchem instalações de armazenamento especialmente construídas para eles em todo o mundo. Curiosamente, em ambos os casos, o progresso é limitado pela mesma tecnologia - apenas por várias razões.

Argumentamos que o PCB é o culpado. Nossa solução é se livrar completamente dela.

Nosso estudo mostra que as placas de circuito impresso podem ser substituídas pelo mesmo material em que os chips soldados nela são constituídos - ou seja, silício. Essa abordagem tornaria possível criar sistemas de tamanho e peso menores, adequados para aparelhos eletrônicos vestíveis e outros dispositivos de tamanho limitado, e computadores de alta velocidade incrivelmente poderosos, capazes de transferir o poder de computação de uma dúzia de servidores para um substrato de silício do tamanho de um prato.

Uma tecnologia totalmente em silício semelhante, que chamamos de rede de interconexão de silício, permite conectar chips nus diretamente a fragmentos de silício individuais. Diferentemente das faixas nas placas de circuito impresso, o contato entre os chips em nosso substrato é do mesmo tamanho das faixas dentro dos chips. Nesse sentido, muito mais conexões podem ser estabelecidas no substrato e todas elas são capazes de transmitir dados mais rapidamente com menos consumo de energia.

O tecido de interconexão de silício (Si-IF) oferece outro benefício adicional. Essa é uma ótima maneira de dividir os sistemas de chip único relativamente grandes, complexos e desconfortáveis [system-on-a-Chip, SoC], nos quais tudo repousa hoje, de smartphones a supercomputadores. Em vez de SoC, os desenvolvedores de sistemas poderiam usar conglomerados menores, mais simples em design e produção de chiplets, intimamente interconectados no Si-IF. Essa revolução de chipsets já está em andamento - AMD, Intel, Nvidia e outras empresas estão oferecendo conjuntos de chipsets montados em gabinetes avançados. Uma rede de silício de interconexão estende essa ideia quebrando a caixa do sistema e permitindo incluir todo o computador nela.

Para entender todos os benefícios de eliminar uma placa de circuito, considere o que acontece com um SoC típico. Devido ao desenvolvimento da eletrônica de acordo com a lei de Moore, em um centímetro quadrado de silício, você pode embalar quase tudo o que precisa para um smartphone funcionar. Infelizmente, por muitas razões relacionadas aos recursos da placa de circuito impresso, esse pedaço de silício é colocado dentro de uma caixa de plástico, às vezes 20 vezes o tamanho do próprio chip.

A diferença de tamanho entre o chip e o gabinete cria pelo menos dois problemas. Em primeiro lugar, o peso e o volume de um chip embalado é maior que o de um pedaço de silício. Obviamente, esse é um problema para todos os dispositivos que precisam ser pequenos, finos e leves. Em segundo lugar, se um produto final requer vários chips trocando dados entre si (e a maioria dos sistemas possui um), a distância que o sinal precisa cobrir aumenta em mais de 10 vezes. Esse é um gargalo para velocidade e consumo de energia, especialmente ao trocar grandes quantidades de dados. Este é provavelmente o maior desafio para a implementação de aplicativos dependentes de dados - gráficos, aprendizado de máquina e pesquisa. Pior ainda, os chips nesses casos são mais difíceis de esfriar. A dissipação de calor tem sido um fator limitante na eletrônica por várias décadas.

Mas se esses casos são tão problemáticos, por que não se livrar deles? Por causa da placa de circuito.

A tarefa da placa de circuito é combinar chips, componentes passivos e outros dispositivos em um sistema em funcionamento. Mas essa tecnologia não é perfeita. As placas de circuito impresso são difíceis de uniformizar - elas geralmente se dobram. As caixas de chip geralmente são conectadas à placa usando gotículas de solda, que derreterão e voltarão a soldar durante a produção. As limitações da tecnologia de solda, juntamente com a curvatura da superfície, fazem com que as gotículas não fiquem mais próximas que 0,5 mm uma da outra. Em outras palavras, será possível colocar não mais que 400 contatos por centímetro quadrado. Para muitas aplicações, isso é muito pouco para transmissão de energia e sinal de e para o chip. Por exemplo, em uma pequena superfície ocupada pelo cristal do processador Intel Atom, há espaço suficiente para centenas de contatos com tamanho de 0,5 mm e precisa de 300. Os desenvolvedores usam casos de cristais para que a matemática converja com o número de contatos por unidade de área. O gabinete pega pequenos contatos de um chip de silício - de 1 a 50 mícrons de largura - e os estende à escala da placa, 500 mícrons.

Recentemente, a indústria de semicondutores tentou limitar os problemas associados às placas de circuito impresso, desenvolvendo gabinetes avançados com tecnologia de interposição de silício. O Interposer é uma fina camada de silício, na qual um pequeno número de chips de silício está conectado, conectados entre si por um grande número de contatos. Mas, ao mesmo tempo, o interpositor com seus chips ainda precisa estar oculto no gabinete e colocado na placa de circuito impresso, portanto, essa opção aumenta a complexidade sem resolver os problemas restantes. Além disso, os interposers são necessariamente finos, frágeis e de tamanho limitado - o que significa que é difícil criar grandes sistemas neles.

Acreditamos que a melhor opção seria livrar-se completamente das caixas e das placas de circuito impresso conectando os chips a um substrato de silício relativamente espesso (de 500 mícrons a 1 mm). Processadores, cristais de memória, chipsets de RF, módulos de controle de tensão e até componentes passivos, como indutores e capacitores, podem ser conectados diretamente ao silício. Comparado com o material usual das placas de circuito impresso - composição de fibra de vidro e epóxi FR-4 - o substrato de silício é sólido e pode ser polido para um plano quase perfeito, para que a curvatura não tenha medo. Além disso, como os chips e o substrato se expandem e se contraem quando a temperatura muda na mesma quantidade, você não precisa mais de uma conexão grande e flexível entre o chip e o substrato, como solda.

Gotas de solda podem ser substituídas por pinos de cobre micrômetros embutidos no substrato. Usando compressão térmica - de fato, a aplicação precisa de aquecimento e pressão - os contatos de entrada / saída de cobre dos chips podem ser conectados diretamente aos pinos. A otimização completa da junta de termocompressão pode nos fornecer contatos muito mais confiáveis do que a soldagem e, ao mesmo tempo, usar menos materiais diferentes.

Ao eliminar as placas de circuito impresso e seus pontos fracos, será possível organizar as portas de E / S a uma distância de apenas 10 mícrons uma da outra em vez de 500 mícrones. Como resultado, será possível colocar 2500 vezes mais portas em um chip de silício sem a necessidade de usar um gabinete.

Melhor ainda, o processo padrão de fabricação de semicondutores pode ser reconfigurado para fabricar diagramas de fiação Si-IF de vários níveis. Suas faixas podem ser muito mais finas do que nas placas de circuito impresso. Eles podem ser separados um do outro por apenas 2 mícrons, e não por 500 mícrones, como nas placas de circuito impresso. A tecnologia ainda permite que você coloque chips a uma distância de 100 mícrons um do outro, ao contrário das placas de circuito impresso, onde devem ter mais de 1 mm. Como resultado, o sistema Si-IF economiza espaço, energia e tempo de viagem do sinal.

Além disso, diferentemente das placas de circuito impresso e dos materiais para gabinetes IC, o silício conduz o calor razoavelmente bem. Os radiadores podem ser montados nos dois lados do Si-IF para remover ainda mais calor - de acordo com nossas estimativas, 70% a mais. E quanto mais calor é removido, mais rápido os processadores podem trabalhar.

Embora o silício tenha boa resistência à tração e tenacidade, é levemente quebradiço. Felizmente, a indústria de semicondutores desenvolveu métodos para trabalhar com grandes substratos de silício para evitar rachaduras ao longo de várias décadas. E depois de todos os procedimentos de produção de Si-IF necessários, esperamos que eles passem na maioria dos testes de confiabilidade, incluindo testes de impacto, aquecimento cíclico e exposição ambiental.

Não há como fugir do fato de que o silício cristalino é mais caro que o FR-4. Embora o custo dependa de muitos fatores, o preço por milímetro quadrado de uma placa de circuito impresso de 8 camadas pode ser dez vezes menor que o de um Si-IF de 4 camadas. No entanto, nossa análise mostra que, se você subtrair o custo de colocar os chips nos estojos e a produção complexa das placas, e levar em conta a economia de espaço usando a tecnologia Si-IF, a diferença de custo será insignificante e, em alguns casos, o Si-IF poderá ser ainda mais lucrativo.

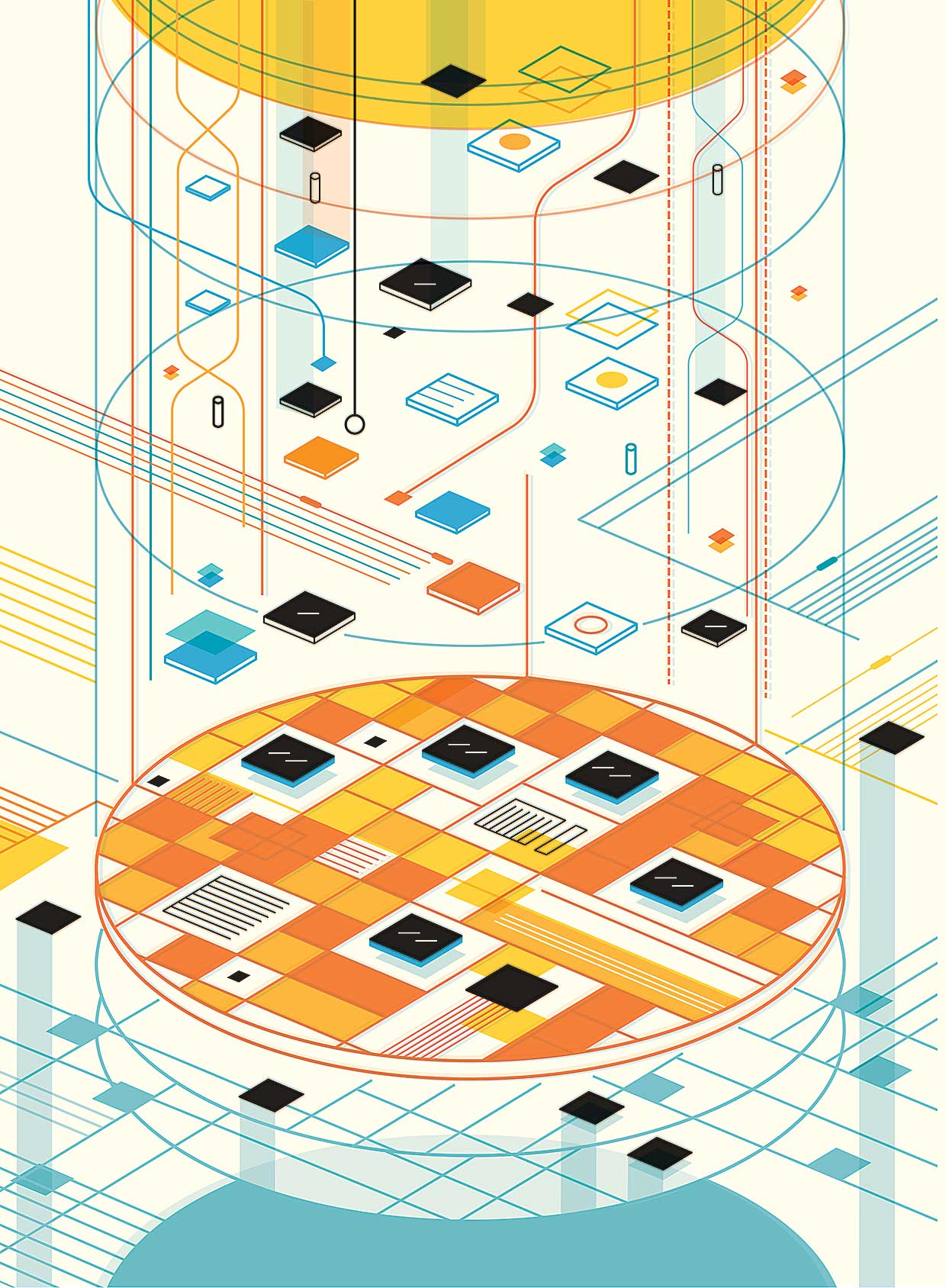

Rede de silício entre componentes em comparação com a placa de circuito impresso e os chips no chassi. Na parte inferior do diagrama, há uma escala aproximada para entender a diferença de tamanho.

Rede de silício entre componentes em comparação com a placa de circuito impresso e os chips no chassi. Na parte inferior do diagrama, há uma escala aproximada para entender a diferença de tamanho.Vejamos alguns exemplos dos benefícios do uso do Si-IF em um sistema de computação. Em um estudo de projetos de servidores, descobrimos que o uso de processadores sem chassi usando Si-IF pode dobrar o desempenho dos processadores convencionais devido à conectividade aprimorada e ao aumento da dissipação de energia. Além disso, o tamanho da placa de silício (na ausência de um termo melhor) pode ser reduzido de 1000 cm

2 para 400 cm

2 . Uma redução tão séria afetará significativamente o volume de edifícios do data center e o tamanho da infraestrutura de refrigeração. Quanto ao outro extremo da escala, estudamos um pequeno sistema para a “Internet das Coisas” baseado no microcontrolador Arm. Nesse caso, o uso do Si-IF reduz não apenas o tamanho da placa em 70%, mas também seu peso, de 20 para 8 gramas.

Além de reduzir os sistemas existentes e aumentar a produtividade, o Si-IF permitirá que os desenvolvedores criem computadores que, de outra forma, seriam impossíveis de construir - ou seriam muito impraticáveis.

Em um servidor poderoso típico, a placa custa de 2 a 4 processadores. Alguns projetos com alta carga computacional requerem vários servidores. Ao mover dados entre diferentes processadores e placas, ocorrem atrasos e gargalos. Mas e se todos os processadores fossem colocados em um único substrato de silício? Eles poderiam ser integrados com tanta força que todo o sistema funcionaria como um grande processador.

Este conceito foi proposto pela primeira vez por Gene Amdahl em sua empresa Trilogy Systems. Mas a Trilogia não teve êxito, porque seu processo de produção falhou em produzir qualidade suficiente para o sistema de trabalho. Ao fabricar um chip, sempre há a possibilidade de defeitos e, com um aumento em sua área, a probabilidade de casamento aumenta exponencialmente. Quando o tamanho do chip é comparável a um prato, é quase garantido que ele mata todo o sistema do casamento.

Mas se você possui uma rede de interconexão de silício, pode começar com os chipsets que já podemos produzir sem defeitos e depois combiná-los em um único sistema. Nossa equipe de pesquisadores da Universidade da Califórnia em Los Angeles e da Universidade de Illinois em Urbana-Campain desenvolveu um sistema com um substrato contendo 40 GPUs. Nas simulações, acelerou os cálculos em mais de 5 vezes e consumiu energia em 80% menos que o sistema equivalente de 40 GPUs criadas usando gabinetes avançados de múltiplos chips e placas de circuito impresso.

Os resultados foram convincentes, embora a tarefa não tenha sido fácil. Tivemos que levar em conta muitas restrições, em particular: a quantidade máxima de calor removida do substrato; como fazer a GPU trocar dados o mais rápido possível; como fornecer energia sobre toda a área do substrato.

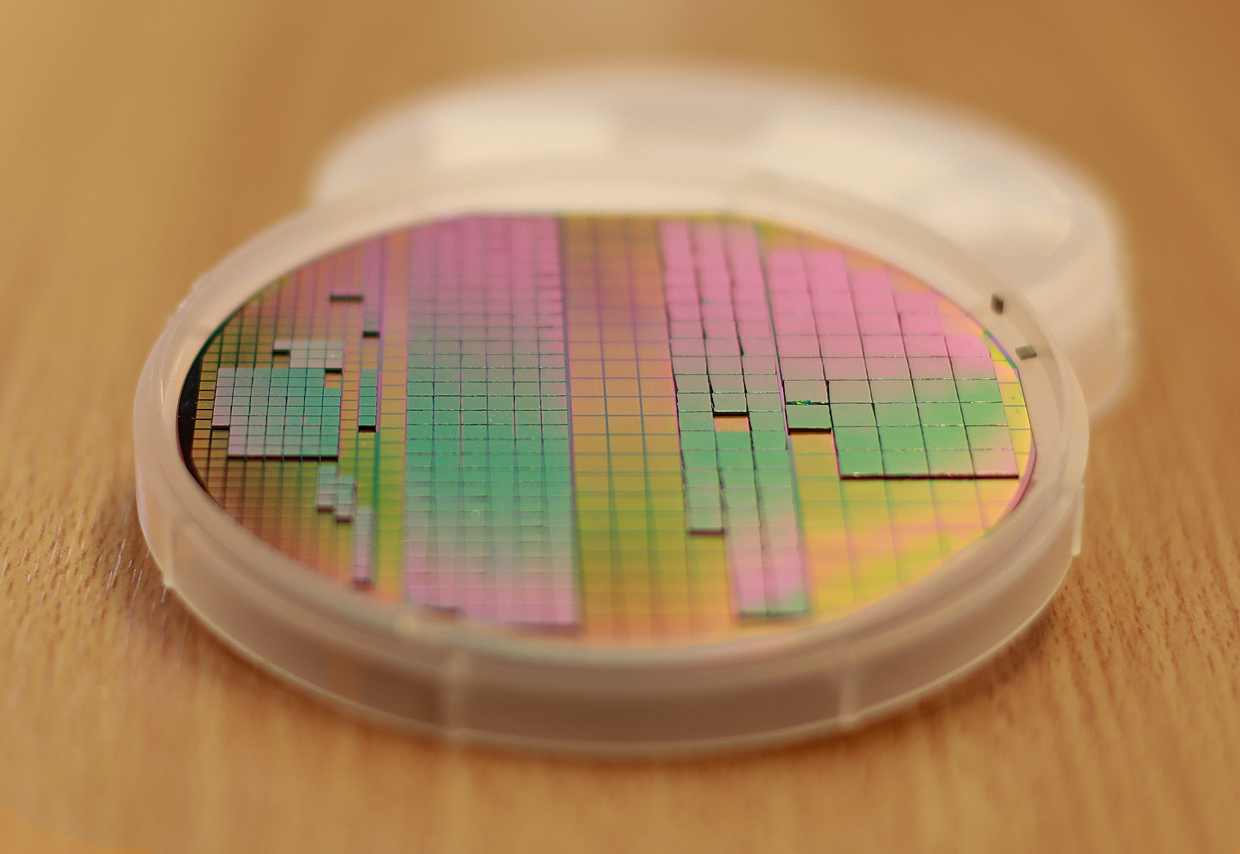

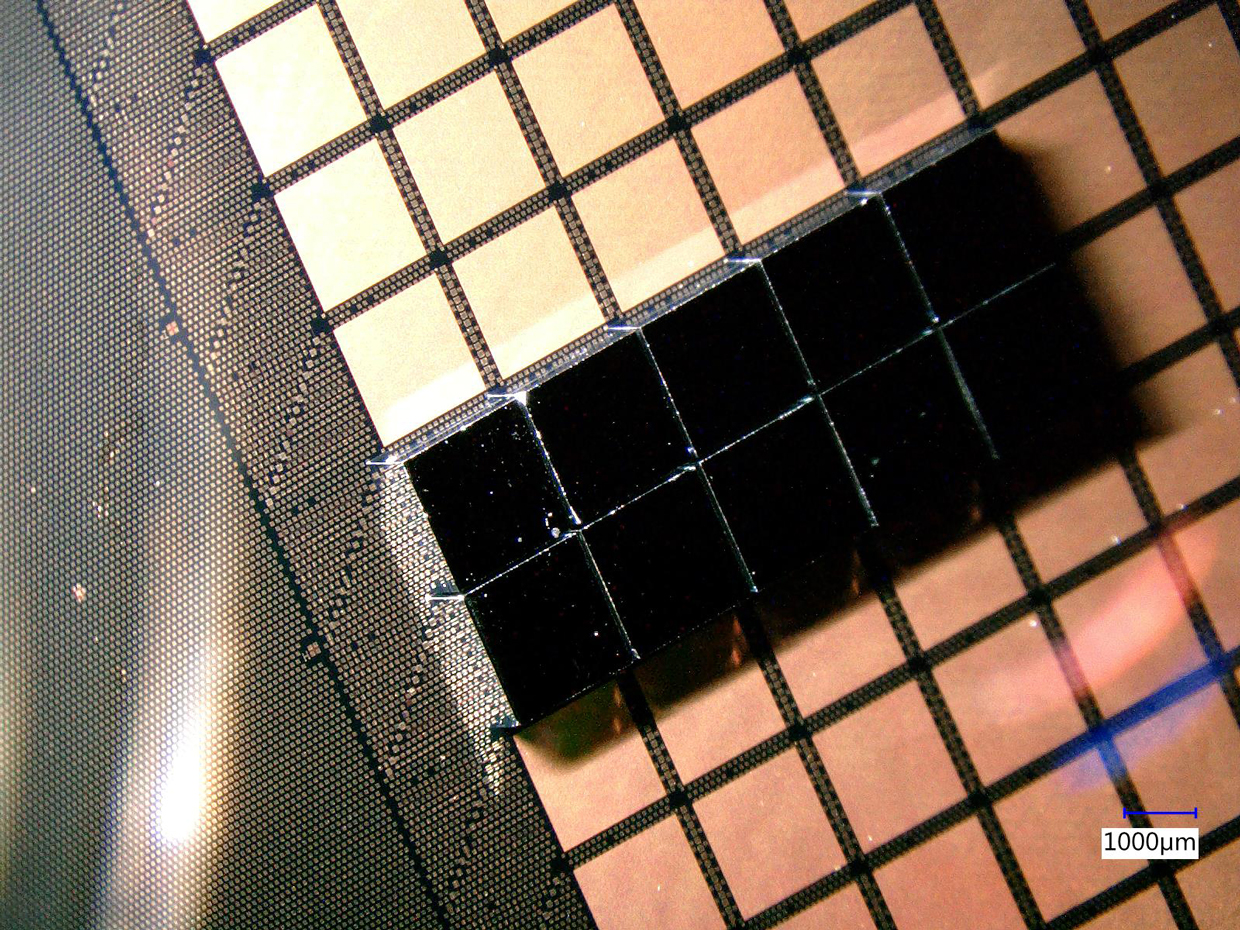

Dilets, ou chipsets, integrados em uma rede de silício interconectada, substrato de 100 mm. Os dilets, ao contrário dos chips em uma placa de circuito impresso, podem ser colocados a uma distância de 100 mícrons um do outro

Dilets, ou chipsets, integrados em uma rede de silício interconectada, substrato de 100 mm. Os dilets, ao contrário dos chips em uma placa de circuito impresso, podem ser colocados a uma distância de 100 mícrons um do outroA principal limitação foi a nutrição. Com uma voltagem operacional padrão de chip de 1 V, as faixas finas do substrato teriam que consumir 2 kW. Em vez disso, aumentamos a tensão para 12 V, reduzindo assim a corrente e a potência. Para fazer isso, era necessário distribuir os reguladores e capacitores de tensão por todo o substrato, e eles substituíram o local que, de outra forma, poderia ser atribuído a GPUs adicionais. Inspirados nos primeiros resultados, estamos montando um protótipo de sistema de computação que esperamos concluir até o final de 2020.

Uma rede de silício de interconexão pode desempenhar um papel em uma tendência importante na indústria de computadores: a divisão do SoC em conjuntos integrados de daylets [dielet de matriz, cristal e letreiro, caixa retrátil / aprox. transl.] ou chiplets (preferimos chamá-los de dia-dia, pois isso enfatiza sua essência como cristais de silício, seu tamanho pequeno e, possivelmente, funcionalidade incompleta sem outros dia-a-dia Si-IF). Nas últimas duas décadas, o desejo de aumentar o desempenho e reduzir os custos convenceu os desenvolvedores a substituir conjuntos de chips por SoCs integrados ainda maiores. E, apesar de suas vantagens, o SoC tem um número suficiente de desvantagens.

Em primeiro lugar, o SoC é um chip grande e, como já mencionado, é bastante difícil obter indicadores aceitáveis da porcentagem de rejeitos na produção de chips grandes, especialmente em indústrias avançadas de semicondutores (lembre-se de que o percentual de rejeitos cresce exponencialmente com o aumento da área do chip). Outra desvantagem do SoC é o alto custo de projeto e início da produção; por exemplo, nos EUA, uma máscara fotolitográfica pode custar US $ 2 milhões, o que torna a opção SoC indisponível para a maioria dos esquemas. Além disso, qualquer pequena mudança no esquema ou a atualização do processo de produção exigirão processamento significativo de todo o SoC. Por fim, a abordagem SoC tenta encaixar todos os subsistemas em um processo de produção, mesmo quando alguns desses subsistemas poderiam ser executados melhor em outro processo. Como resultado, nada no SoC atinge a maior eficiência ou velocidade possível.

A integração no Si-IF sem a participação de gabinetes evita todos esses problemas, mantendo o pequeno tamanho e velocidade do SoC, além de oferecer vantagens e custos de desenvolvimento. Ele divide o SoC em seus componentes constituintes e recria um sistema em um substrato, system-on-Si-IF (SoIF).

Esse sistema consiste em daylets produzidos de forma independente, conectados via Si-IF. Os dilets de separação de distância mínima (dezenas de micrômetros) são comparáveis à distância entre dois blocos funcionais de SoC. A fiação no Si-IF é a mesma usada no nível superior do SoC, portanto a densidade dos compostos é comparável.

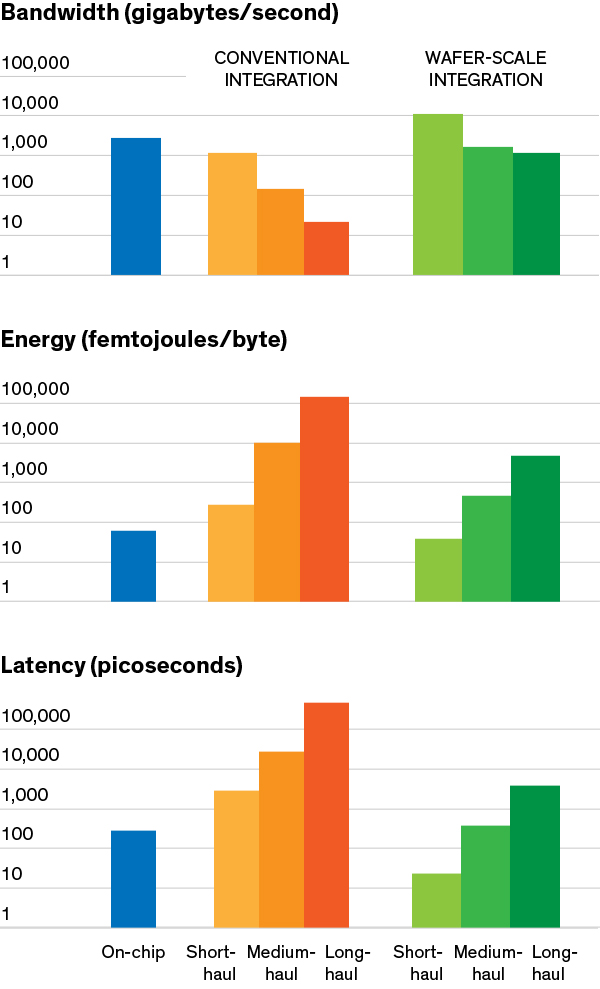

De cima para baixo: largura de banda (GB / s), consumo de energia (fJ / B), atraso (ps).

De cima para baixo: largura de banda (GB / s), consumo de energia (fJ / B), atraso (ps).

Azul - sistema em um chip, tons de vermelho - integração normal, tons de verde - sistema sobre substratoAs vantagens do SoIF sobre o SoC são devidas ao tamanho do atraso. Pequenas exclusões são mais baratas de produzir do que grandes SoCs, porque elas têm uma taxa de rejeição mais baixa devido ao seu tamanho pequeno. No SoIF, apenas o substrato em si tem um tamanho grande. Mas é improvável que ela tenha um problema com o casamento, uma vez que é feito de várias camadas que são fáceis de fabricar. A maior parte da perda devido a defeitos se deve a defeitos nas camadas do transistor ou nas camadas metálicas inferiores superdensas, e é o caso de uma rede de silício interconectada.

Além disso, o SoIF terá todas as vantagens na busca pela qual a indústria está mudando para chipsets. Por exemplo, a transição do SoIF para o próximo processo de fabricação deve ser mais fácil e mais barata. Cada dylet pode ter sua própria tecnologia de produção, e somente os dylets que realmente exigem isso podem ser atualizados. E exclusões que não se beneficiam particularmente de transistores reduzidos não precisarão ser alteradas. Essa integração heterogênea permite criar uma classe completamente nova de sistemas que misturam misturadores de diferentes gerações e tecnologias que geralmente não são compatíveis com o CMOS. Por exemplo, nosso grupo demonstrou recentemente a combinação de um cristal de fosfeto de índio com SoIF como um exemplo de uso potencial em circuitos de alta frequência.

Como as diletas serão produzidas e verificadas antes da conexão com o SoIF, elas podem ser usadas em diferentes sistemas, o que economizará significativamente. Como resultado, o custo total de desenvolvimento e fabricação de SoIF pode ser 70% menor que o do SoC. Isso será especialmente verdadeiro para grandes sistemas produzidos em pequenos lotes - como é o caso das indústrias aeroespacial e de defesa, onde há demanda apenas por lotes da ordem de várias centenas ou milhares de unidades. Sistemas personalizados também serão mais fáceis de serem executados no SoIF, pois isso reduz o custo e o tempo de desenvolvimento.

Acreditamos que esses benefícios de custo e diversidade podem levar ao início de uma nova era de inovação, na qual o novo hardware estará disponível para um número muito maior de designers, startups e universidades.

Nos últimos anos, fizemos um progresso significativo na tecnologia de integração Si-IF, mas ainda há muito a ser feito. Antes de tudo, é necessário mostrar um processo de produção de Si-IF com baixo defeito comercialmente viável.

A criação de substratos na escala Si-IF pode exigir inovação na litografia sem máscara. A maioria dos sistemas litográficos que existem hoje em dia pode fabricar substratos medindo 33x24 mm. Como resultado, precisamos de um sistema capaz de fornecer um substrato com um diâmetro de 300 mm.Também precisamos de mecanismos para verificar dia-a-dia e o Si-IF. A indústria já está se movendo para testar cristais nus, enquanto os fabricantes de chips estão mudando para cheatlets em pacotes avançados e integração tridimensional.Então precisamos de novos radiadores ou outras estratégias de dissipação de calor que usem boa condutividade térmica de silício. Meus colegas da Universidade da Califórnia e eu estamos desenvolvendo uma solução integrada de refrigeração e nutrição de substratos chamada PowerTherm.Além disso, para a montagem de sistemas completos, você precisará de estruturas, fixadores, conectores e cabos.Também precisaremos fazer algumas alterações na metodologia de desenvolvimento para que uma das promessas do SoIF se torne realidade. Si-IF é um substrato passivo no qual existem apenas um condutor. Portanto, as conexões entre vôos devem ser curtas. Para faixas mais longas conectando dilettes distantes, precisamos de dilettes intermediárias que transmitam dados mais adiante na cadeia. Será necessário revisar os algoritmos de design responsáveis pelo arranjo dos elementos e a finalidade dos contatos para que eles tirem proveito máximo desse tipo de integração. E também precisaremos desenvolver novas maneiras de explorar várias arquiteturas de sistema que tiram vantagem da heterogeneidade e atualizabilidade do SoIF.Também precisaremos considerar a confiabilidade dos sistemas. Se um dylet estiver com defeito após anexá-lo ou falhar durante a operação, será muito difícil substituí-lo. Portanto, no SoIF, especialmente nos grandes, será necessário criar tolerância a falhas. Pode ser implementado no nível da rede ou no nível do dia. No nível da rede, será necessário garantir a passagem do sinal ignorando os daylets com falha. No nível do dia, vários truques com redundância física podem ser considerados, por exemplo, o uso de vários pinos de cobre para cada uma das portas de entrada / saída.Obviamente, as vantagens de uma montagem de daylet dependem da disponibilidade de daylets úteis que podem ser integrados ao sistema. Até agora, a indústria está escolhendo quais tipos de dilets produzir. Você não pode simplesmente fazer um daylet para cada subsistema no SoC, pois alguns deles serão muito pequenos. Uma abordagem promissora é o uso do processamento estatístico de circuitos SoC e placas de circuito impresso existentes, a fim de encontrar funções que "tendem" a estar fisicamente mais próximas uma da outra. Se essas funções tiverem as mesmas tecnologias de produção e ciclos de atualização, elas precisarão ser integradas em um único dia.Essa lista de problemas pode parecer muito longa, mas os pesquisadores já estão trabalhando em alguns deles como parte do programa Estratégias de Integração Heterogênea Comum e Estratégias de Reutilização de IP (CHIPS) da Agência de Projetos de Pesquisa Avançada em Defesa, bem como com consórcios do setor. E se pudermos resolver esses problemas, isso nos ajudará seriamente a manter o legado da lei de Moore de uma maneira menor, mais rápida e mais barata.