Recentemente, estávamos envolvidos na restauração do computador de controle de bordo Apollo, um computador responsável por controlar, navegar e monitorar as missões Apollo que voavam para a Lua. Este computador histórico foi um dos primeiros a usar circuitos integrados (ICs) e seu processador foi completamente construído em válvulas NOR (o segundo tipo de CIs, um amplificador de leitura, foi usado na memória do computador). Neste artigo, descreverei a arquitetura e o design da CPU.

Arquitetura de computador Apollo Control

Bandejas separadas do computador de controle Apollo. A bandeja esquerda contém lógica baseada em portas NOR. Na direita - memória e componentes auxiliares.O

Bandejas separadas do computador de controle Apollo. A bandeja esquerda contém lógica baseada em portas NOR. Na direita - memória e componentes auxiliares.O Computador de Orientação Apollo (AGC) foi desenvolvido na década de 1960 para permitir que as missões da Apollo voassem para a lua. No momento em que a maioria dos computadores ocupava espaço de uma geladeira de tamanho normal para uma sala inteira, o AGC era algo único - era pequeno o suficiente para caber a bordo da espaçonave Apollo, pesava 32 kg e não levava mais que 0,03 m

3 (30 litros).

O computador AGC é de 15 bits. É estranho encontrar um tamanho de palavra que não seja uma potência de dois, mas na década de 1960, mesmo antes de os bytes se tornarem populares, os computadores usavam uma variedade de tamanhos de palavra. 15 bits forneciam precisão suficiente para pousar na lua (e usavam dados com precisão dupla e tripla, se necessário); portanto, 16 bits simplesmente aumentariam o tamanho e o peso do computador desnecessariamente.

A instrução AGC estava localizada em uma palavra de 15 bits e consistia em 3 bits, indicando o código de operação, e 12 bits, indicando o endereço na memória. Infelizmente, esses volumes ainda não eram suficientes; portanto, o computador usou vários truques e soluções alternativas, e a arquitetura acabou sendo um pouco estranha. Um endereço de memória de 12 bits só pode acessar palavras em 4K. Ao mesmo tempo, o AGC tinha 2K palavras na RAM principal e 36K na memória principal. Para acessar toda a memória, a AGC usou um sofisticado sistema de comutação de banco de memória e vários registros. Em outras palavras, a memória pode ser acessada apenas em pedaços de 256 palavras e ROM - em pedaços de tamanho um pouco maior.

3 bits para o código de operação não foram suficientes para indicar diretamente 34 instruções possíveis; portanto, o AGC usou truques com a extensão do valor das instruções e com o fato de que algumas instruções faziam sentido para serem executadas apenas com determinadas células de memória. Além disso, truques como endereços “mágicos” na memória foram usados - por exemplo, a gravação na célula “shift right register” executou uma mudança bit a bit, eliminando assim a necessidade de uma instrução “shift direita” separada. Havia também instruções combinando várias ações ao mesmo tempo.

A arquitetura AGC era bastante simples, mesmo para os padrões da década de 1960. Embora tenha sido criado em uma era de mainframes complexos e poderosos, as capacidades da AGC eram muito limitadas; em termos de potência e arquitetura, é comparável aos primeiros microprocessadores. Seus pontos fortes foram o tamanho compacto e os excelentes recursos para fornecer entrada e saída de dados em tempo real.

O diagrama arquitetural abaixo mostra os principais componentes do AGC. Destaquei em cores as partes em que me refiro com mais detalhes. O AGC possuía um pequeno conjunto de registros e um módulo aritmético simples que tratava apenas da adição. Ele tinha apenas 36K palavras ROM e 2K palavras RAM. O "barramento de gravação" era a principal maneira de transferir dados entre componentes. As instruções de decodificação e um gerador de sequência geraram pulsos de controle para o AGC.

Diagrama de blocos AGC

Diagrama de blocos AGCCerca de metade do diagrama é ocupado por memória, o que reflete o fato de que em muitos aspectos a arquitetura AGC foi desenvolvida em torno de sua memória. Como a maioria dos computadores da década de 1960, a AGC usava memória central, armazenando cada bit em um minúsculo anel de ferrite (núcleo) preso a uma malha de arame. Como cada bit exigia um núcleo físico separado, a quantidade dessa memória era radicalmente menor que a de um semicondutor moderno. Uma característica distintiva da memória nos núcleos era que a leitura de uma palavra da memória a excluía; portanto, após cada acesso, esse valor precisava ser reescrito. O AGC também tinha memória ROM fixa, os famosos

núcleos costurados - eles eram usados para armazenar programas e eram costurados fisicamente com fios (veja abaixo).

Memória de close-up em núcleos costurados

Memória de close-up em núcleos costuradosVálvulas NOR

O AGC foi um dos primeiros computadores a usar IP. As possibilidades desses primeiros IPs eram muito limitadas; nos chips AGC (abaixo), havia apenas seis transistores e oito resistores, e juntos eles implementaram uma porta NOR com três entradas.

Válvula NOR dupla com três entradas da AGC. Dez fios fora do cristal estão conectados aos contatos externos do IC.

Válvula NOR dupla com três entradas da AGC. Dez fios fora do cristal estão conectados aos contatos externos do IC.A designação esquemática da válvula NOR é mostrada abaixo. Esta é a porta lógica mais simples: se todas as entradas forem iguais a zero, a saída será igual a uma. Você pode se surpreender, mas um portão NOR é suficiente para criar um computador. A NOR é uma válvula universal: qualquer outra válvula lógica pode ser fabricada com base. Por exemplo, ao combinar todas as entradas NOR, obtemos um inversor. Depois de colocar o inversor na saída da NOR, obtemos uma válvula OR. Ao colocar os inversores nas entradas da porta NOR, obtemos uma porta AND. E a partir desses portões você pode construir uma lógica mais complexa: gatilhos, somadores e contadores.

A válvula NAND tem a mesma versatilidade. Nos circuitos modernos, por razões técnicas, as NANDs são usadas com mais frequência do que as NORs. No curso popular "

From NAND to Tetris " descreve como criar um computador a partir de válvulas NAND, até a implementação do jogo "Tetris". Primeiro, um conjunto de portas lógicas é construído a partir de NAND (NOT, AND, OR, XOR, multiplexador, desmultiplexador). Então, blocos de construção maiores são criados a partir deles (gatilho, somador, contador, ALU, registro) e a partir deles - um computador.

A porta NOR fornece 1 se todas as entradas tiverem 0. Se pelo menos uma das entradas tiver 1, a NOR fornecerá 0.

A porta NOR fornece 1 se todas as entradas tiverem 0. Se pelo menos uma das entradas tiver 1, a NOR fornecerá 0.Muitas vezes, no AGC, encontra-se um componente como o acionador RS (set-reset, set / reset). Este circuito é composto de duas portas NOR e armazena um bit de dados. O bit 1 é armazenado na entrada configurada e o bit 0 é armazenado na entrada de redefinição, ou seja, o pulso 1, aplicado à entrada de ajuste, desliga a válvula superior e liga a mais baixa, de modo que a saída 1 é acionada. . Se 0 for aplicado às duas entradas, o gatilho lembrará seu estado anterior, desempenhando o papel de uma unidade. Na próxima seção, mostraremos como os registros são feitos a partir de um gatilho.

Gatilho RS de dois portões NOR. Uma válvula, quando ligada, desliga a outra. Uma linha acima de uma das saídas indica que complementa a outra.

Gatilho RS de dois portões NOR. Uma válvula, quando ligada, desliga a outra. Uma linha acima de uma das saídas indica que complementa a outra.Registros

O AGC possui um pequeno conjunto de registros para armazenamento temporário de valores fora da memória principal. O registro principal é o inversor (A) usado em muitas operações aritméticas. Ele também possui um contador registrador Z, bloco aritmético registra X e Y, buffer B, endereço de retorno Q e alguns outros (em computadores modernos, a pilha é usada para chamar rotinas e retornar a partir delas, mas nessa época, os programadores precisavam escrever a pilha para recursão. ) Para acessar a memória, há um registro de endereço de memória S e, para dados, um registro de buffer de memória G. Além disso, o AGC possui registros na memória principal - por exemplo, contadores de entrada / saída.

O diagrama abaixo mostra o esquema de registro AGC, simplificado para o caso com um bit e dois registros. Cada bit de registro possui um gatilho usando o esquema descrito anteriormente (azul e roxo). Os dados são transferidos de e para os registradores através do barramento de gravação (vermelho). Para gravar no registro, o gatilho é redefinido por um sinal claro (CQG ou CZG, verde). Em seguida, o sinal de "gravação" (WQG ou WZG, laranja) permite que os dados que percorrem o barramento de gravação definam o gatilho de registro correspondente. Para ler o registro, o sinal de leitura (RQG ou RZG, ciano) passa a saída do gatilho pelo amplificador de gravação para o barramento de gravação e é usado em outras partes do AGC. O esquema de registro completo é mais complexo, possui vários registros de 16 bits, mas o esquema básico é o seguinte.

Operação simplificada de registro AGC

Operação simplificada de registro AGCO gráfico de registro ilustra três pontos principais. Em primeiro lugar, o circuito de registro é construído a partir de portas NOR. Em segundo lugar, a movimentação de dados é construída em torno do barramento de gravação. Finalmente, as ações dos registradores dependem de certos sinais de controle que chegam no momento certo.

Módulo aritmético

A maioria dos computadores possui um

dispositivo lógico aritmético que executa operações aritméticas e booleanas. Em comparação com os computadores modernos, o módulo aritmético do AGC é muito limitado: ele apenas realiza a adição de quantidades de 16 bits; portanto, é chamado módulo aritmético e não o módulo aritmético-lógico (o restante das operações é realizado por meio de vários truques; por exemplo, a subtração é realizada por adição, antes da qual para um dos argumentos, os bits são invertidos etc.).

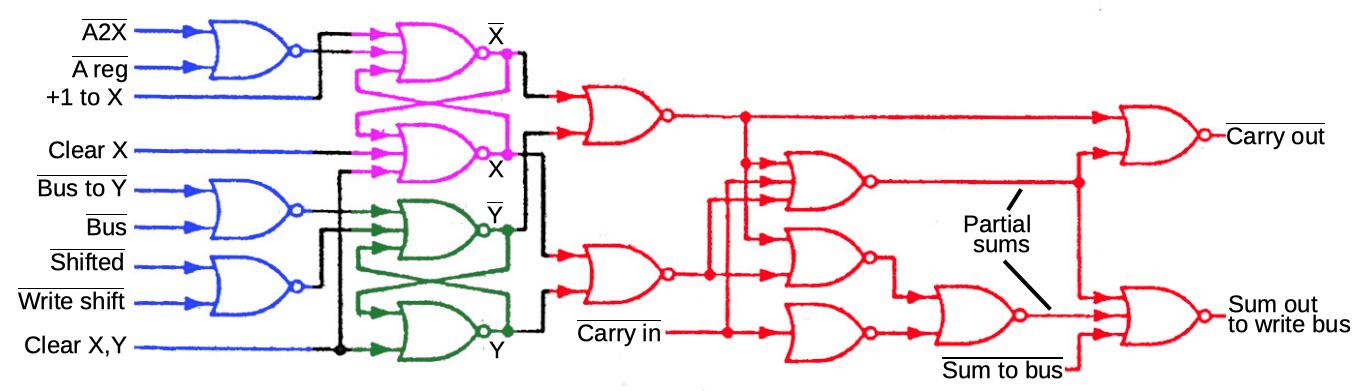

O diagrama abaixo mostra um bit do módulo aritmético do AGC.

O somador completo (vermelho) calcula a soma de dois bits e carrega. A transferência é transferida para o próximo adicionador - dessa forma, eles podem ser combinados para adicionar palavras mais longas (para acelerar a transferência de transferências em casos como 111111111111111 + 1, o AGC usa um adicionador com um

salto de transferência ).

Os registros X e Y (roxo e verde) fornecem dois bits de entrada para o somador. Eles são implementados usando os gatilhos já descritos nas válvulas NOR. O loop azul grava os valores nos registradores X e Y de acordo com os sinais de controle. O esquema é bastante complicado, porque permite armazenar constantes e valores com uma alteração nos registros, mas não vou entrar neste tópico. Preste atenção ao sinal de controle A2X, que transfere o valor do registro A para o registro X; voltaremos a ele mais tarde.

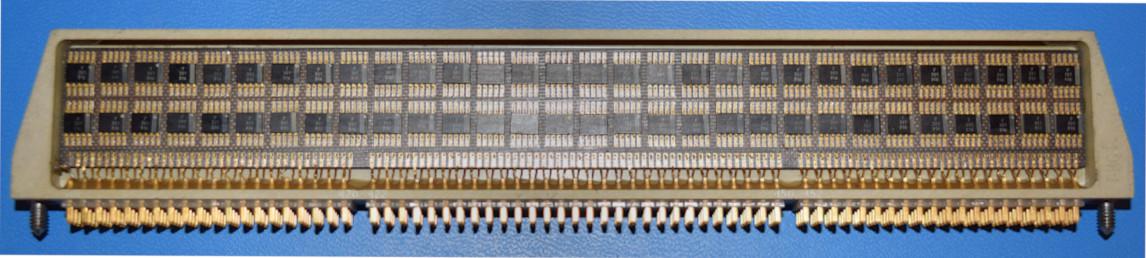

A foto abaixo mostra a implementação física do circuito AGC. Este módulo implementa quatro bits para registros e um módulo aritmético. Retângulos pretos são IPs planos; cada módulo possui duas placas com 60 chips cada e um total de 240 portas NOR. O módulo aritmético e os registros são montados a partir de quatro módulos idênticos, cada um dos quais processa quatro bits; isso é semelhante à

seção do

microprocessador .

O módulo aritmético e os registros são montados a partir de quatro módulos idênticos. Os módulos são instalados nos slots de A8 a A11.

O módulo aritmético e os registros são montados a partir de quatro módulos idênticos. Os módulos são instalados nos slots de A8 a A11.Execução de instruções

Esta seção descreve a sequência de operações que o AGC executa para executar a instrução. Em particular, mostrarei como a instrução ADS (adicionar ao armazenamento) funciona. Esta instrução lê o valor da memória, o adiciona à unidade (registro A) e salva a soma no somador e na memória. Esta é uma instrução única, mas, para sua execução, o AGC executa várias etapas e muitos valores são movidos para cá e para lá.

O cronômetro de instruções é implementado devido ao subsistema de memória nos núcleos magnéticos. Em particular, a leitura de um valor da memória apaga o valor armazenado; portanto, após cada leitura, o valor deve ser gravado novamente. Além disso, ao acessar a memória, há um atraso entre a designação do endereço e o recebimento de dados. Como resultado, cada ciclo do relógio passa 12 etapas para leitura e gravação subseqüente. Cada intervalo de tempo (de T1 a T12) dura um pouco menos de microssegundos e todo o ciclo dura 11,7 μs e é chamado de tempo de ciclo de memória (MCT).

Módulo de memória de núcleo magnético apagável da AGC. Ele armazena 2 folhas de quilos, cada bit é armazenado usando um pequeno anel de ferrita separado.

Módulo de memória de núcleo magnético apagável da AGC. Ele armazena 2 folhas de quilos, cada bit é armazenado usando um pequeno anel de ferrita separado.MCT é a unidade básica de memória para executar instruções. Uma instrução típica requer dois ciclos de relógio: um para extrair a instrução da memória e o segundo para executar a operação. Portanto, uma instrução típica utiliza dois MCTs (23,4 μs), o que fornece 43.000 instruções por segundo (comparado aos processadores modernos e seus bilhões de instruções por segundo, isso é extremamente lento).

O AGC processa instruções, dividindo-as em subcomandos, cada um dos quais requer um ciclo de clock de memória. Por exemplo, uma instrução ADS consiste em dois subcomandos: ADS0 (adição) e STD2 (chamando a próxima instrução). O diagrama abaixo mostra o movimento dos dados dentro do AGC para executar a instrução ADS0. 12 medidas vão da esquerda para a direita.

Os passos mais importantes são os seguintes:

T1: o endereço do operando é copiado do registro de instruções B para o registro de endereços de memória S para iniciar a leitura da memória.

T4: O operando é lido da memória no registro de dados da memória G.

T5: O operando é copiado de G para o somador Y. O valor da unidade A é copiado para o somador X.

T6: O somador calcula a soma U e a copia para o registro de dados da memória G.

T8: O contador de programa Z é copiado para o registrador de endereço de memória S, em preparação para receber a próxima instrução da memória.

T10: A soma do registro de dados da memória G é gravada de volta na memória.

T11: O valor U é copiado para a unidade A.

Embora esta seja uma instrução simples de soma, muitos dados são transmitidos repetidamente aqui em 12 intervalos de tempo. E com cada uma dessas ações um sinal de controle específico é associado; por exemplo, o sinal A2X no intervalo T5 copia o valor do inversor A para registrar X. Para copiar o registro G para registrar Y, são necessários dois pulsos de controle: RG (leia G) e WY (escreva Y). Na próxima seção, explicarei como o módulo de controle AGC gera os sinais de controle necessários para cada instrução.

Módulo de controle

Como a maioria dos computadores, o módulo de controle AGC decodifica cada instrução e gera sinais de controle que informam ao restante do processador o que ele precisa fazer. O AGC usa um módulo de controle pré-programado que consiste em válvulas NOR para gerar sinais. O AGC não usa microcódigo; ele não possui microinstruções e controle a memória, pois isso ocuparia muito espaço físico.

O coração do módulo de controle AGC é chamado de gerador de ponto cruzado. Leva um subcomando e um dos períodos de tempo e gera sinais de controle para essa combinação. Pode ser imaginada na forma de uma rede, na qual os subcomandos vão em uma direção e os segmentos de tempo na outra, e cada um dos pontos de interseção possui seu próprio sinal de controle.

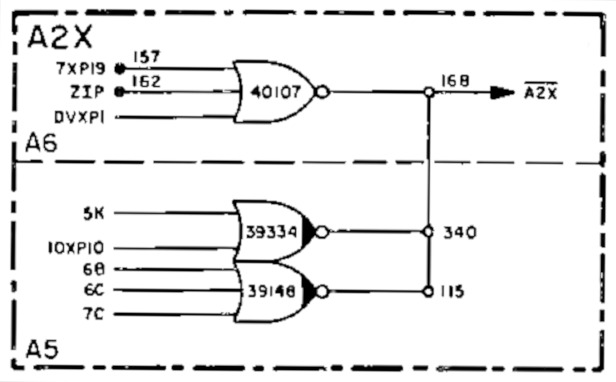

O gerador de interseção requer muitos componentes e é dividido em três módulos; Este é o módulo A6. Preste atenção aos fios adicionados que alteram o circuito. Esta é uma versão inicial de um módulo para testes no terreno; módulos de vôo já não tinham fios.

O gerador de interseção requer muitos componentes e é dividido em três módulos; Este é o módulo A6. Preste atenção aos fios adicionados que alteram o circuito. Esta é uma versão inicial de um módulo para testes no terreno; módulos de vôo já não tinham fios.Para eficiência, o módulo de controle final é altamente otimizado. Instruções com comportamento semelhante são combinadas e processadas pelo gerador de interseção, o que reduz o tamanho do circuito necessário. Por exemplo, o AGC possui uma instrução "adicionar a uma unidade com precisão dupla" (DAS). Como é aproximadamente equivalente a duas adições de palavras únicas, os subcomandos DAS1 e ADS0 no gerador de interseção têm lógica comum. O diagrama abaixo mostra o circuito gerador de interseção para o intervalo de tempo T5, e a lógica do subcomando ADS0 (usando o sinal DAS1) é destacada. Por exemplo, um sinal 5K é gerado a partir de uma combinação de DAS1 e T5.

Mas o que são sinais 5K e 5L? Essa é outra otimização. Muitos pulsos de controle geralmente são alimentados juntos; portanto, em vez de gerá-los diretamente, o gerador de interseção gera sinais intermediários para interseções. Por exemplo, 5K gera pulsos de controle A2X e RG e 5L gera pulsos de controle WY. O diagrama abaixo mostra como o sinal A2X é gerado: qualquer um dos 8 sinais diferentes (incluindo 5K) gera A2X. Circuitos semelhantes geram outros sinais de controle. Essas otimizações tornaram possível reduzir o tamanho do gerador de interseção, mas ele ainda permaneceu grande e cresceu para três módulos.

Resumindo, podemos dizer que o módulo de controle é responsável por dizer à CPU o que fazer para executar a instrução. Primeiro, as instruções são divididas em subcomandos. O gerador de interseção gera os pulsos de controle necessários para cada intervalo de tempo e subcomando, informando aos registradores, módulo aritmético e memória o que eles precisam fazer.

Normalmente, as instruções consistiam em dois subcomandos, mas havia exceções. Algumas instruções, como multiplicação ou divisão, exigiram o uso de muitos subcomandos, pois consistiam em várias etapas. Por outro lado, a instrução de salto no TC usava um subcomando, pois só precisava chamar a próxima instrução.

Outros processadores usaram abordagens diferentes para a geração de sinais de controle.

O 6502 e muitos outros microprocessadores iniciais decodificaram as instruções usando um PLA (array lógico programável) que implementa a lógica AND / OR através da memória somente leitura. Microprocessador 6502.

Microprocessador 6502.Conclusão

Foi um passeio emocionante pelo computador de controle a bordo da Apollo. Para não esticar muito, concentrei-me nas instruções de adição do ADS e em alguns pulsos de controle (A2X, RG e WY). Espero que você tenha uma idéia de como montar um computador a partir de elementos primitivos como as válvulas NOR.A parte mais visível da arquitetura é o caminho dos dados: um módulo aritmético, registradores e um barramento de dados. Os registros AGC são baseados em gatilhos simples de portas NOR. E embora o módulo aritmético do AGC possa fazer apenas a adição, o computador ainda pode lidar com todo o conjunto de operações, incluindo operações de multiplicação, divisão e booleanas.No entanto, o caminho dos dados é apenas parte do computador. Entre outros componentes críticos, há um módulo de controle que informa aos componentes o que eles precisam fazer. A abordagem usada no AGC é baseada em um gerador de interseção que usa lógica altamente otimizada e codificada para gerar os pulsos de controle corretos para subcomandos específicos e intervalos de tempo.Usando esses recursos, o AGC forneceu orientação, navegação e controle a bordo das missões Apollo e tornou possível pousar na lua. Ele também estimulou a indústria de circuitos integrados inicial, usando 60% dos CIs fabricados nos EUA em 1963. Portanto, os computadores modernos devem muito ao AGC e seus componentes simples da NOR. O AGC trabalha em um laboratório conectado a um osciloscópio Tektronix vintage

O AGC trabalha em um laboratório conectado a um osciloscópio Tektronix vintage