Boris Tsirlin e Alexander Kushnerov

30/10/2019

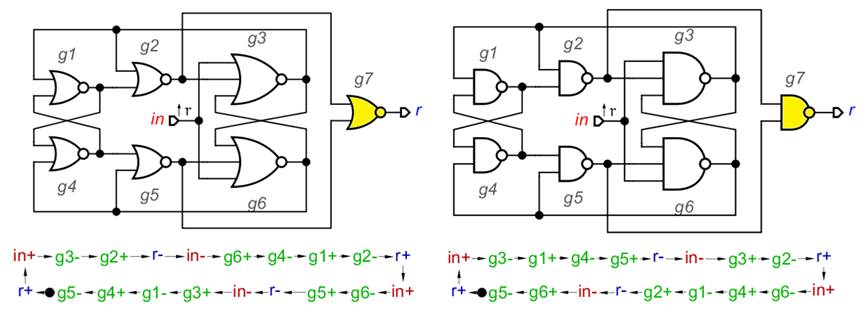

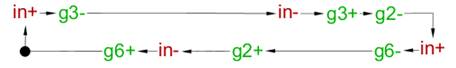

Não é difícil para um projetista experiente descobrir um circuito familiar, não importa de que forma ele seja desenhado. Neste artigo, mostramos que os dois circuitos de transistor das patentes são uma variante do gatilho de contagem assíncrona (AST). Comparado ao circuito padrão, alguns transistores estão ausentes nas patentes. Isso pode ser considerado um mau funcionamento. Mostraremos que, se a mesma falha ocorrer no circuito padrão, ela continuará funcionando corretamente. Um AST implementado apenas nos elementos OR-NOT [1] ou apenas nos elementos AND-NOT é conhecido como um gatilho de Harvard. Ambas as variantes dos esquemas são mostradas na Fig. 1, em que g7 é um indicador de conclusão transitória. No futuro, não consideraremos isso. Na Fig. A Figura 1 também mostra os gráficos de transição de sinal (STGs) [2] construídos no Workcraft [3].

Fig. 1. Gatilho de contagem assíncrona (AST) e seu STG.

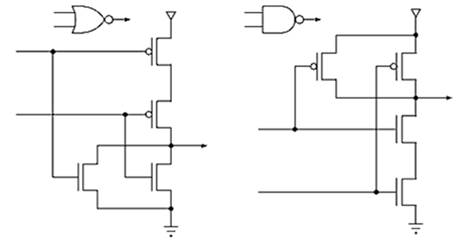

Observe que nas duas versões do AST existem três pares de elementos (g1, g2), (g4, g5) e (g3, g6) que possuem uma entrada comum. Circuitos de transistor dos elementos 2I-NOT e 2OR-NOT mostrados na Fig. 2. Os elementos de três entradas são organizados de forma semelhante e contêm 6 transistores.

Fig. 2. Circuitos transistores dos elementos 2I-NOT e 2OR-NOT.

Pegamos dois elementos 2OR-NOT e selecionamos em cada entrada, onde o transistor p-MOS está conectado ao Upit. Conecte essas entradas e conecte ao terra (log. 0). Ambos os transistores abrirão e a tensão em seus drenos será igual a Upit. Isso é suficiente para conectar com segurança os drenos e substituir os dois transistores por um, como mostrado na Fig. 3? Não. Você precisa verificar o que acontece se efetuar logon na entrada compartilhada. 1. As saídas de ambos os elementos serão conectadas ao terra e teremos um circuito de ponte de quatro transistores p-MOS. Para as duas entradas restantes, temos quatro combinações 0 e 1. É fácil mostrar que em nenhuma delas existe um curto-circuito entre Upit e terra.

Fig. 3. Dois elementos 2OR-NOT que compartilham uma entrada comum.

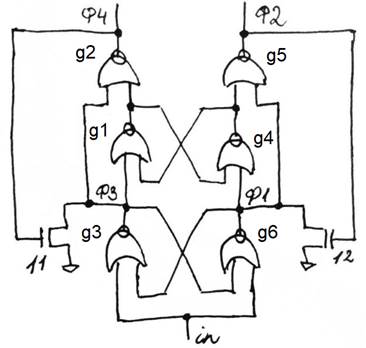

Agora, consideramos o circuito distribuidor de pulsos [4] na Fig. 4. Usando a Fig. 3, podemos redesenhar este diagrama como mostrado na Fig. 5. Já é possível reconhecer AST na Fig. 1, no entanto, lá os elementos g3 e g6 têm 3 entradas.

Fig. 4. O esquema do distribuidor de pulsos de [4].

Fig. 5. Uma variante do circuito na Fig. 4)

As portas dos transistores 11 e 12 podem ser consideradas como entradas de elementos 3OR-NOT nos quais o terceiro transistor p-MOS está em curto. Isso afeta a operação correta do circuito? Considere a ordem de aparecimento dos sinais em, g2 e g6 na entrada do elemento g3. Para fazer isso, exclua todos os outros sinais no STG correspondente na Fig. 1 como mostrado na Fig. 6

Fig. 6. STG para OU NÃO. Sinais em, g2, g6 e g3.

Como o terceiro transistor p-MOS está em curto, a troca de g3 + pode ocorrer após a troca de in- e g6- (em qualquer ordem) sem permitir a troca de g2-. No entanto, como pode ser visto na Fig. 6, na seção de g2 + para g2- há apenas in- e g6 +, portanto, a troca proibida g3 + não ocorre. Antes de alternar g2 +, o elemento g3 já está em 0 e em sua entrada g6 ainda é 0, ou seja, O primeiro transistor p-mos está aberto. A troca de g2 + abre o transistor 11 e deve desligar o transistor p-MOS em curto. Além disso, isso não acontece, a comutação abre o segundo transistor p-MOS. Assim, através de dois transistores p-MOS abertos e um transistor aberto 11, a corrente começa a fluir de Upit para o solo. Isso continua por um curto período de tempo até que o próximo comutador g6 + feche o primeiro transistor p-MOS. Durante esse tempo, o transistor 11 fornece 0 na saída de g3. Como exatamente? Suponha que as resistências dos transistores p-MOS e n-MOS abertos sejam iguais e iguais a R e, depois de ligar a tensão no g3, salta de 0 a (1/3) Upit, mas este é o caso ideal. Na prática, existe alguma capacitância parasitária entre g3 e o solo, cuja tensão aumenta suavemente e pode não atingir (1/3) Upit. De uma forma ou de outra, essa tensão será menor que (1/2) Upit e significa um log. 0. Para o transistor 12, tudo é semelhante, fornece um curto espaço de tempo 0 na saída de g6. Assim, os atrasos dos elementos g6 e g3 determinam dois períodos de tempo em que o gatilho consome uma grande corrente aproximadamente igual a Upit / (3R).

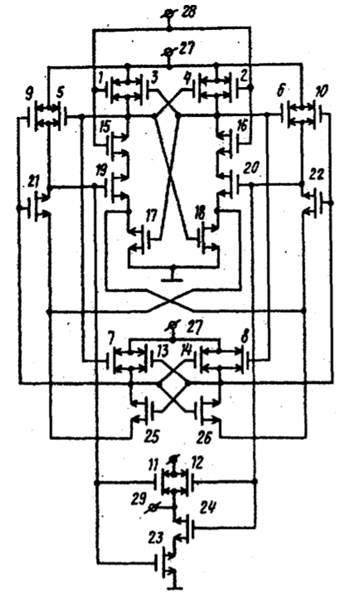

Vamos agora considerar o circuito do gatilho de contagem [5] na Fig. 7. Aqui, os transistores 11, 12, 24, 23 formam o elemento 2I-NOT, que, aparentemente, é um indicador de AST na Fig. 1. Outro elemento 2I-NOT é formado pelos transistores 7, 13, 25 e 18. Vamos prestar atenção ao fato de que o transistor 18 está conectado ao terra e de forma semelhante ao exemplo na Fig. 3, é comum aos três elementos E NÃO. O segundo elemento 2I-NOT, que inclui o transistor 18, é formado pelos transistores 5, 9, 21 e o terceiro é 3I-NOT nos transistores 2, 4, 16, 20. Paralelamente aos transistores 2 e 4, deve haver um terceiro transistor p-MOS mas ele está ausente. O circuito na Fig. 7 é simétrico; para um melhor entendimento, o redesenhamos como mostrado na Fig. 8)

Fig. 7. Esquema do gatilho contável de [5].

Fig. 8. Uma variante do circuito na Fig. 7)

Haverá saídas g3 e g6 na Fig. 8 mudar corretamente se o terceiro transistor p-mos em paralelo estiver ausente? Isto será entendido após a análise do STG na Fig. 9, que, como no caso anterior, é obtido do STG correspondente na Fig. 1 removendo todos os sinais, exceto em, g2, g6 e g3.

Fig. 9. STG para NAND. Sinais em, g2, g6 e g3.

O elemento g3 é 3I-NOT, portanto, após ativar +, g6 + e g2 + (em qualquer ordem), g3- alternará. Qualquer um dos comutadores in, g6 ou g2- reverso deve causar a alternância do g3 +. No entanto, g2- não pode abrir o transistor p-MOS ausente, portanto g3 permanecerá em 0 e aguardará a troca de in- ou g6-. Como pode ser visto na Fig. 9, na seção g3- a g3 + não há comutação g2- e o transistor p-MOS não é necessário aqui. Por outro lado, esse transistor deve fornecer um log. 1 a g3 quando in e g6 alternam arbitrariamente. Considere na Fig. 9ª seção de g3 + a g2 +. A comutação g2- fecha o transistor 19. Em seguida, a ativação + fecha o transistor 1 e abre o transistor 15. O elemento g6 permanece em 1, ou seja, o transistor 17 está aberto e o transistor 3 está fechado. Assim, em + desconecta g3 da terra e da Upit. No entanto, o log é mantido no g3. 1, uma vez que na prática existe uma capacitância parasitária entre g3 e terra, que é carregada até Upit. A comutação g6- abre o transistor 3 e conecta essa capacitância ao Upit. Para a segunda metade do esquema, tudo é semelhante. Assim, os atrasos dos elementos g6 e g3 determinam o tempo durante o qual o estado é armazenado no tanque. Na prática, é importante que a corrente de fuga dos transistores 19 e 20 seja pequena; caso contrário, a capacitância pode descarregar abaixo de (1/2) Upit no tempo previsto.

Comparado com o AST padrão na Fig. 1, nos diagramas da Fig. 5 e na fig. 8, a função de definir 1 elemento 3 OU NÃO e a função de redefinir como 0 do elemento 3 OU NÃO está danificada. Isso significa que o AST padrão continuará funcionando corretamente, mesmo se ocorrer um mau funcionamento nos elementos g6 e g3. Para um circuito padrão (sem g7), são necessários 28 transistores. Para os circuitos na Fig. 4 e na fig. 7 (sem os transistores 11, 12, 24, 23), são necessários 23 e 22 transistores, respectivamente. Se você retornar os transistores p-MOS ausentes, esses circuitos funcionarão com mais confiabilidade. O número mínimo de transistores no circuito na Fig. 7 não significa necessariamente que é melhor do que o circuito na Fig. 4 e melhor circuito na Fig. 1. Além do número de transistores e do consumo atual, existem outros parâmetros importantes, por exemplo,

- complexidade de um circuito adicional para definir estados iniciais

- capacidade de carga (taxa de recarga da capacidade de carga)

- taxa de saída do estado metaestável

- número e valores de capacitâncias parasitárias

- número e valores de correntes de fuga

Uma análise comparativa desses parâmetros, bem como uma discussão dos esquemas AST implementados em outros elementos, está além do escopo deste artigo.

Literatura

[1] GT Osborne, "Estágio de contador binário assíncrono com flip-flop e gate, utilizando a pluralidade de circuitos NOR interconectados". Patente US3139540, 30 de junho 1964

[2] L. Ya. Rosenblum e A. V. Yakovlev, "Em uma nova forma gráfica para ilustrar a essência da invenção", Issues of Invention, No. 11, pp. 36-40, 1988.

[3] https://workcraft.org

[4] V. I. Goryachev, B. M. Mansurov, Ya. D. Martynenko e R. G. Talibov, "Distribuidor de pulso de quatro fases". Certificado de direitos autorais SU342299, 14/06/1972.

[5] V. I. Varshavsky, N. M. Kravchenko, V. B. Marakhovsky e B. S. Tsirlin, "Contagem de trigger em transistores CMOS". Certificado de direitos autorais SU1398069, 05.23.1988.