Em condições modernas, o engenheiro de projeto precisa adquirir constantemente novos conhecimentos para estar em demanda no mercado de trabalho. Freqüentemente, novas informações precisam ser recebidas, por assim dizer, "sem interrupção da produção": durante o trabalho em um projeto, em viagens ao trabalho etc. O mundo digital moderno permite isso, seria um desejo. No entanto, às vezes a qualidade do conhecimento adquirido pode sofrer. A informação é assimilada por uma pessoa superficialmente ou mesmo de forma distorcida.

Ao me comunicar com rastreadores de software que trabalham em software CAD para placas de circuito impresso Cadence OrCAD / Allegro, às vezes notei que as pessoas não dão muita importância à indicação de cores dos campos no editor de regras do Constraint Manager. A saber: os usuários não prestam atenção ao fato de que algumas colunas são pintadas de amarelo.

De fato, a cor amarela no editor de regras de cadência significa que essa verificação não pode ser executada por qualquer motivo. Os motivos podem ser diferentes:

- Validação desativada pelo usuário.

- O caminho condutor não está definido ou não está completo.

- Outras razões

Na maioria dos casos, não há situações fatais nas quais aparecem erros que levam à inoperabilidade do software. Como o OrCAD PCB Editor possui um mecanismo de vários estágios para verificar o projeto na RDC, assim, você não pode desativá-los de uma só vez. No entanto, às vezes por causa de uma lacuna de conhecimento infeliz ou por desatenção, são criadas situações que levam a situações incorretas no projeto.

Por exemplo, um desenvolvedor me contou como ele desativou acidentalmente a verificação de curto-circuito nas linhas opostas. Além disso, o software CAD não relatará um erro nesta situação, pois a verificação é desativada pelo usuário.

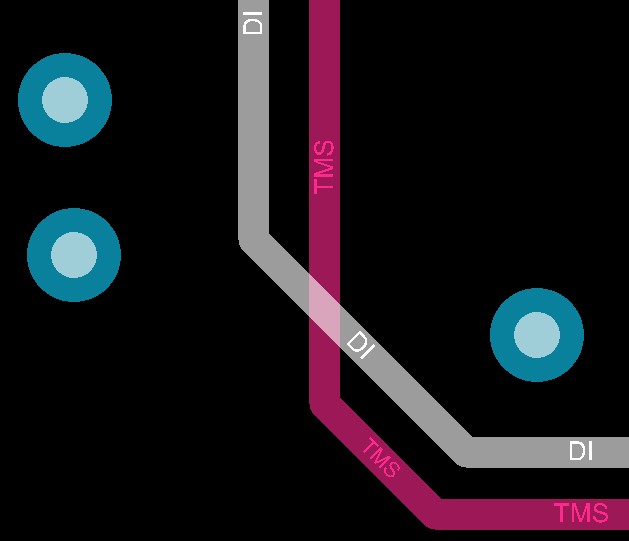

Interseção de um condutor por outro sem mensagem de erro

Interseção de um condutor por outro sem mensagem de erroA figura mostra que os condutores de linhas opostas se cruzam. No entanto, uma mensagem de erro não ocorre. O motivo desse comportamento do programa não é claro para o desenvolvedor, pois durante o rastreamento on-line, todas as lacunas definidas no gerenciador de constantes são salvas e mantidas.

Lacunas e regras nas regiões são suportadas ao rastrear

Lacunas e regras nas regiões são suportadas ao rastrearA falta de um token de DRC reside precisamente nas configurações do Gerenciador de restrições.

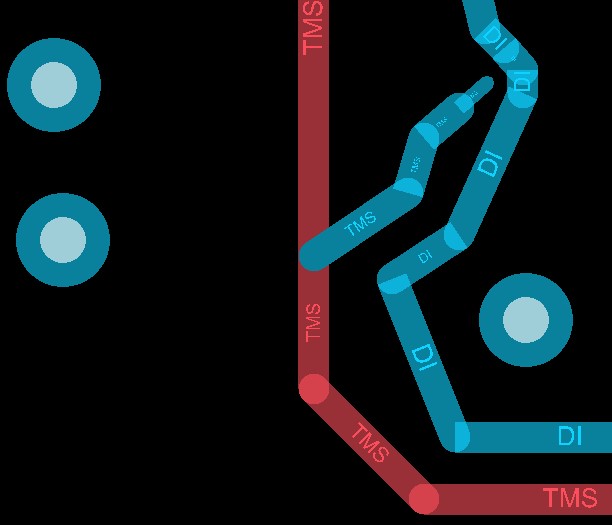

É assim que a verificação desativada se parece no Gerenciador de restrições

É assim que a verificação desativada se parece no Gerenciador de restriçõesUma cor amarela na seção Verificação de intervalo linha a linha significa que a verificação não é realizada (ou não pode ser executada). Por esse motivo, o marcador da RDC não ocorre. Obviamente, a desativação parcial das verificações às vezes é muito conveniente e pode reduzir o tempo total para verificar um projeto, mas ... Isso pode levar a consequências fatais se, ao enviar um projeto e gerar arquivos para produção, o desenvolvedor não incluir todas as verificações necessárias e não realizar uma verificação final na RDC.

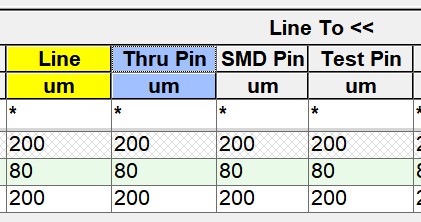

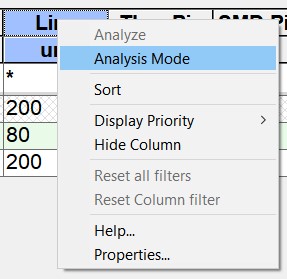

Desabilitar ou habilitar uma verificação específica no Cadence é muito simples: basta clicar no cabeçalho da célula de interesse e selecionar Modo de Análise no menu suspenso.

Ativar ou desativar rapidamente certos tipos de verificações

Ativar ou desativar rapidamente certos tipos de verificaçõesQuando a verificação é ativada, a cor da tampa fica cinza; quando a verificação é desativada, a cor da tampa é amarela.

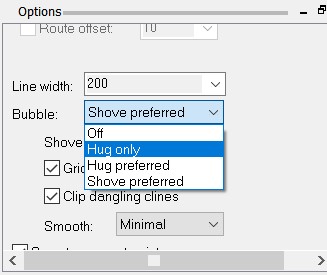

Por que, quando a verificação está desabilitada no Constraint Manager, as lacunas necessárias ainda são suportadas durante o rastreamento, e o OrCAD PCB Designer impede que o usuário cometa um erro acidental? Isso ocorre precisamente porque o sistema de verificação da RDC consiste em duas partes: verificações on-line da DRC em tempo real e verificações sob demanda do modo de lote da DRC. O modo de lote DRC é encerrado à força no Gerenciador de restrições. O DRC online continua funcionando se, no modo de rastreamento, o valor do parâmetro Bolha na janela Opções for diferente do estado DESLIGADO.

Valores possíveis que o parâmetro Bubble pode levar

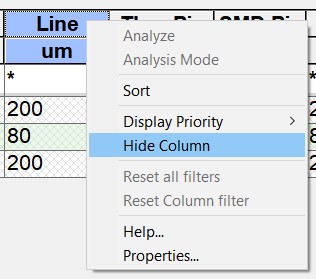

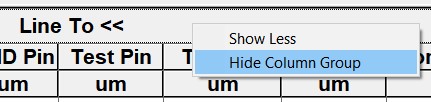

Valores possíveis que o parâmetro Bubble pode levarSe um engenheiro não quiser ver as verificações desabilitadas ou algumas seções no editor de regras do Gerenciador de restrições, elas poderão ser ocultadas facilmente.

Ocultar uma coluna ou seção da consideração

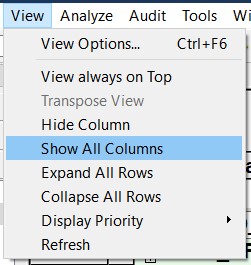

Ocultar uma coluna ou seção da consideraçãoQuando a verificação se torna necessária novamente, ela pode ser retornada no campo de colunas exibidas.

Retornar colunas ocultas

Retornar colunas ocultasVale ressaltar que o editor de tabelas das regras CAD Cadence Allegro / OrCAD, com todo o seu poder, é muito conveniente e fácil de configurar, e as próprias verificações são realizadas com bastante rapidez, e muitas vezes não é necessário forçar o desligamento.

Por outro lado, se for necessário desativar algumas verificações lentas, o desenvolvedor pode primeiro salvar o arquivo "tecnológico" que contém as configurações de todas as verificações necessárias, depois desativá-las temporariamente e, ao emitir a documentação do projeto após a conclusão do rastreio, recarregue esse arquivo tecnológico com todas as verificações e execute a RDC final.

Sim, a propósito, se você se lembra do desenvolvedor que desativou o teste de curto-circuito entre os circuitos - felizmente, o fabricante de PCB no início do pedido chamou sua atenção para o problema do circuito entre os circuitos, para que eles conseguissem evitar perdas financeiras e de tempo. Mas, por experiência em uma empresa envolvida na fabricação de placas de circuito impresso, posso dizer que o problema de desativar verificações "desnecessárias" era muito comum para a maioria dos clientes e não dependia de quais desenvolvedores de CAD trabalham. Portanto, não esqueça de incluí-los no momento certo!