Nesta semana, a Intel compartilhou seus planos de longo prazo para a introdução de novos processos de fabricação. Por volta de 2029, a Intel

pretende introduzir uma tecnologia de processo com padrões de 1,4 nm. Após 10 anos, é improvável que a equipe de gerenciamento da empresa seja a mesma de hoje. Portanto, esses planos são sutilmente remanescentes da parábola de Khoja Nasreddin sobre o burro, cã e professor do animal na pessoa de Khoja. Ao meio-dia, o réu pode não estar lá. Mas isso não é sobre isso. Planejado, então aceitamos como um guia de ação.

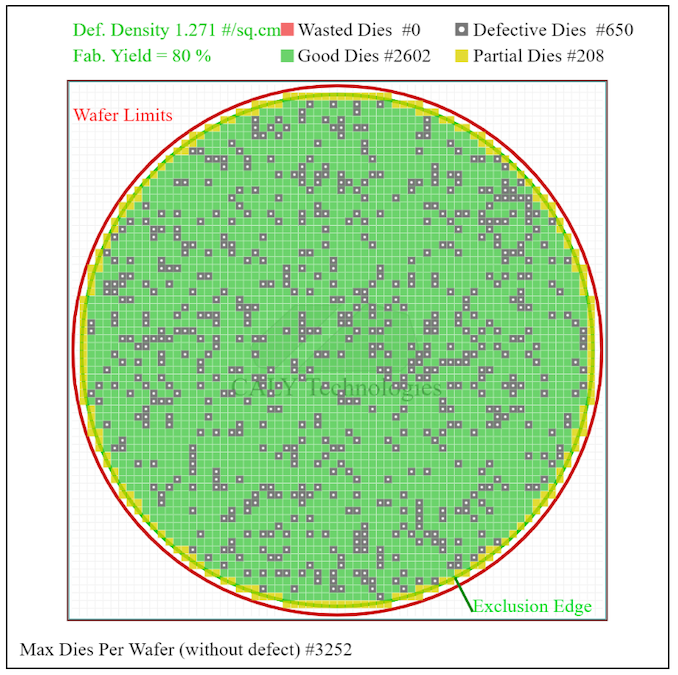

Nos campos dos principais fabricantes de semicondutores, há um pouco mais de clareza, o que é confirmado pela produção arriscada de chips TSMC com padrões de 5 nm (

hoje , a taxa de defeitos é de apenas 20% na taxa de 3-8% para cristais com uma área de 17,92 mm

2 , para chiplets. O AMD Zen 2 terá um nível mais alto de rejeição - até 60%). No entanto, antes do lançamento dos processadores AMD com padrões de 5 nm, pelo menos mais um ano e meio passará.

/ imagem do site da AnandTech

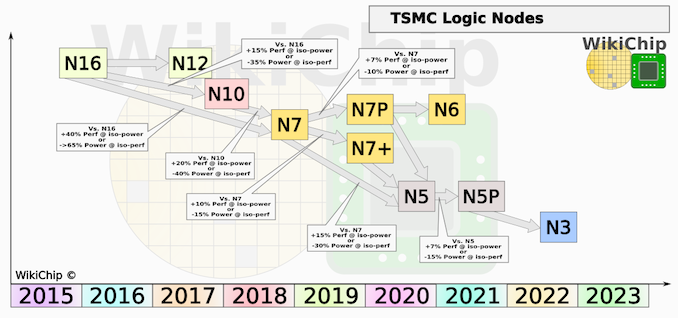

/ imagem do site da AnandTechNo próximo ano, a partir do segundo trimestre, a tecnologia de processo TSMC com padrões de 5 nm será usada para produção em série de SoC em núcleos ARM. Em 2022, a TSMC obviamente começará a produção arriscada de chips de 3 nm (o que esses nanômetros significam) e, em alguns anos, a empresa promete começar a produção de soluções de 2 nm. Será em 2024-2025, ou dois a três anos antes da Intel apresentar a mesma tecnologia de processo.

Para a Samsung, processos com padrões de 5 nm e 4 nm serão a

evolução da tecnologia de processo de 7 nm, que será expressa em uma pequena redução gradual nas etapas de metalização nos elementos FinFET, como canais e portas. Em geral, a estrutura dos transistores (o número de arestas) permanecerá a mesma que a estrutura da célula SRAM não será alterada. A Samsung começará a produção de chips usando a tecnologia de processo de 4 nm na área de 2021. No mesmo ano, a empresa promete iniciar uma produção arriscada usando uma tecnologia de processo de 3 nm. E algumas fontes sul-coreanas

afirmam que isso pode acontecer já em 2020, o que parece improvável.

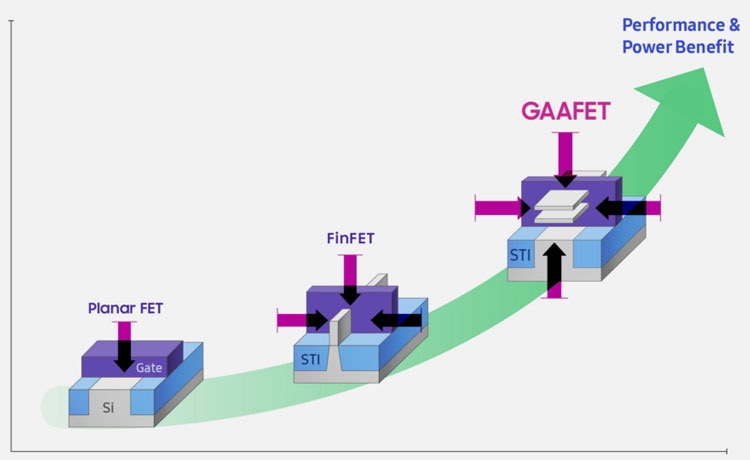

Neste artigo, estamos interessados no fato de que, até a tecnologia de processo de 4 nm, a Samsung e, obviamente, a Intel e a TSMC usarão transistores FinFET - aletas de altas portas, nas quais as cristas de canais verticais cortam e perfuram. Nesses transistores, o campo eletromagnético do portão penetra nos canais de três lados, e dois ou três canais em cada transistor no total fornecem a corrente necessária para a válvula operar.

/ Imagem Samsung

/ Imagem SamsungComeçando com a tecnologia de processo de 3 nm, a Samsung quebrará essa prática. O conceito FinFET deixará de funcionar como antes. As portas do transistor FinFET serão muito pequenas e não poderão comutar transistores. A necessidade de reduzir ainda mais a tensão de alimentação dos transistores apenas agravará essa situação. Portanto, para a tecnologia de processo de 3 nm, será

introduzido um transistor com um anel GAA (Gate-All-Around).

/ Imagem Samsung

/ Imagem SamsungA Samsung deu ao novo transistor o nome comercial MBCFET (Multi Bridge Channel FET). Na prática, esse é o desenvolvimento da idéia de um transistor,

criado em conjunto por pesquisadores da IBM, Samsung e GlobalFoundries. Supunha-se que um transistor semelhante em estrutura estaria envolvido na transição para uma tecnologia de processo com padrões de 5 nm. Mas, na realidade, essa estrutura de válvula aparecerá nos chips apenas no início da produção de 3nm da Samsung. O transistor MBCFET consistirá em canais dispostos horizontalmente uns sobre os outros na forma de nanopáginas, em vez de sulcos verticais, como no FinFET. As características dos transistores MBCFET serão convenientemente controladas variando o número de páginas localizadas uma acima da outra e alterando a largura da página. Cada página é um canal. A soma dessas variáveis determinará qual transistor temos: potente e rápido, ou fraco, mas com baixa potência. Haverá mais de duas gradações - de cinco a sete.

/ Imagem Samsung

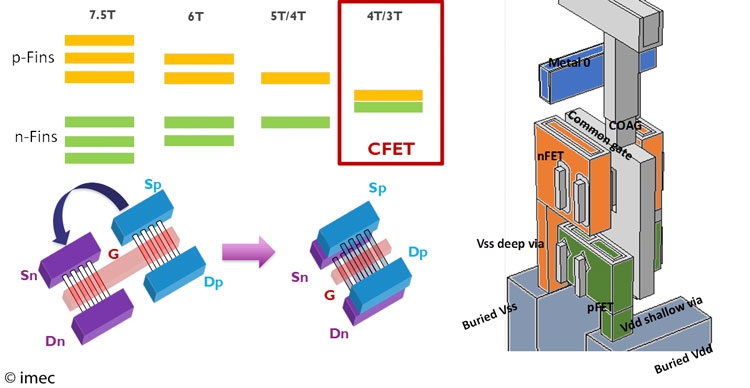

/ Imagem SamsungO mais interessante, para o qual esta nota foi concebida, é que o transistor MBCFET pode aparecer apenas dentro da estrutura da tecnologia de processo de 3 nm, e a tecnologia de processo com padrões de 2 nm exigirá novamente alterações na estrutura do transistor. Um novo transistor com o nome de Forksheet foi proposto pelo centro de pesquisa belga Imec. Pela primeira vez, os representantes da Imec

falaram em detalhes sobre a estrutura de um transistor com páginas separadas (nano) nesta primavera em um evento anual. Mas você não pode alimentar o rouxinol com fábulas. Nós sentiríamos isso. Você ainda não pode sentir, mas os belgas realizaram uma simulação do transistor Forksheet no TCAD, que foi

relatado três dias atrás.

Antes de considerar os dados, explicamos que o transistor Forksheet é uma modificação do transistor com nanopáginas - o mesmo MBCFET ou Gate-All-Around, se ignorarmos os termos Samsung. A aleta do obturador vertical no transistor Forksheet é um pouco maior que a do MBCFET, mas as nanopáginas dos canais do transistor são divididas em duas e separadas por uma camada dielétrica. De fato, um transistor MBCFET com um movimento do pulso se transforma em um par de transistores complementares de transistores do tipo p e n.

A estrutura proposta destrói uma séria barreira na vedação de transistores na forma de complexidade para aproximar os transistores p e n o mais próximo possível e, ao mesmo tempo, evitar a influência negativa mútua dos portões.

Obviamente, a abordagem proposta aumentará a densidade dos transistores no chip, mas a modelagem mostrou que o desempenho e o consumo de energia também melhorarão. Mudar para um transistor com páginas separadas reduzirá a área de cristal em até 20% e, ao reduzir capacitâncias e vazamentos espúrios, o desempenho de dispositivos eletrônicos aumentará em até 10%. Se você não aumentar a frequência, poderá reduzir o consumo de energia em até 24%.

Em estoque, a Imec possui outra

tecnologia que pode aumentar ainda mais a densidade dos transistores. Pode ser aplicado tanto na fase de produção de chips de 3 nm quanto em padrões de produção mais baixos. A idéia é criar um par de transistores complementares um sobre o outro. Essa operação aparentemente simples promete reduzir o tamanho da célula lógica padrão e da célula SRAM em 50%. As idéias bem desenvolvidas e parcialmente testadas nos modelos terminam aqui.

Mudar para uma tecnologia de processo de 1 nm também pode exigir uma nova estrutura de transistor. Ao mesmo tempo, deve-se lembrar que os engenheiros geralmente acham possível aumentar seu prazer - criar algo assim para dar mais um passo em frente nas muletas velhas.