Este artigo discutirá as etapas necessárias para criar um dispositivo que atenda aos requisitos gerais de segurança funcional (CE). E também será proposta a arquitetura do gerador de tensão de "segurança" mais simples. Desde o controle da tensão, você pode controlar quase qualquer dispositivo.

O site tem

artigos maravilhosos (

um ,

dois ) sobre esse tópico e um

livro no qual eu cresci como engenheiro no FB.

Uma série de normas GOST R IEC 61508 (IEC 61508) é a base para os padrões russos que determinam a ordem de desenvolvimento dos dispositivos para os quais os requisitos do FB são impostos. Como você sabe, ao desenvolver dispositivos relacionados ao FB, existem padrões do setor que governam o procedimento de desenvolvimento (para ferrovias, esses são GOST R 52980-2015 “Requisitos de software”, GOST R 34012-2016 “Requisitos gerais para equipamentos ferroviários”, etc. e)

De acordo com as normas GOST R IEC 61508 e IEC 61508, as falhas são divididas em 2 tipos: sistemático e aleatório.

As falhas sistemáticas são determinadas por erros na especificação, projeto, codificação de software, a proteção contra elas é criada por meio da organização do ciclo de vida, incluindo: verificação de todas as etapas do ciclo de vida para conformidade com os requisitos e validação (teste de validação) do produto final.

Falhas aleatórias são calculadas como a probabilidade de falha de hardware; a proteção contra elas geralmente é determinada por decisões de arquitetura.

Por padrões, todos os métodos podem ser divididos em dois grupos: organizacional e técnico. Os métodos organizacionais incluem: implementação do ciclo de vida, aplicação de padrões de codificação, monitoramento da produção de hardware. Os métodos técnicos incluem: sabotagem (da diversidade inglesa - diversidade), redundância, proteção contra influências ambientais, independência e separação de componentes, autodiagnóstico (cada um desses métodos deve ser descrito em artigos separados).

Os principais métodos organizacionais para proteção contra erros sistemáticos são descritos nos apêndices do GOST R IEC 61508. Como exemplo, consideramos o componente sistemático do software. Ao escrever código, deve-se prestar muita atenção às regras e padrões de codificação usados na codificação. Um dos padrões bem conhecidos de programação na linguagem SI é o MISRA-C; seu uso melhora a segurança do sistema. Além disso, existem analisadores estáticos (geralmente é útil para os analisadores verificarem qualquer código quanto a erros) que podem verificar a conformidade com o padrão MISRA-C, um deles é o

PVS-Studio .

O desvio parcial de software pode ser alcançado através do uso de vários algoritmos de desenvolvimento de software. Um sistema completo de diversificação de software é alcançado apenas quando há duas especificações diferentes de requisitos de software, equipes diferentes de programadores, diferentes meios de programação de dispositivos em produção, ou seja, esses programas devem ser completamente diferentes e o processo de programação de dispositivos também deve ser diferente. Além disso, ao desenvolver ferramentas de software, é necessário proteger contra erros de ferramentas. O software mais crítico em termos de ferramentas é o compilador em conjunto com a biblioteca padrão e o vinculador. É possível obter uma variedade de ferramentas usando os compiladores ARMCC e GCC. No entanto, algumas versões do ARMCC têm certificação TUV para conformidade com SIL-3, de acordo com a IEC 61508, e o GCC é usado com sucesso no desenvolvimento do

software Falcon 9 .

Considere os resultados da compilação do comando "Write to Port":

| Comando no idioma SI (ISO / IEC 9899): MDR_PORTE-> CLRTX = 0x0040 |

|---|

| GCC | "ARMCC" |

|---|

| LDR r3, [pc, nº 20] | MOVS r0, # 0x40 |

| MOVS r2, 64; 0x40 | LDR r1, [pc, nº 16]; @ 0x0000072C |

| STR r2, [r3, nº 36] | STR r0, [r1, # 0x24] |

Mesmo pelo exemplo de um comando tão simples (como pode ser visto na tabela), a sequência de comandos do microcontrolador é diferente e diferentes registros de trabalho são usados. O que, de alguma forma, nos fornece “diversidade”, reduzindo assim a probabilidade de erros devido à

causa comum da falha das ferramentas.

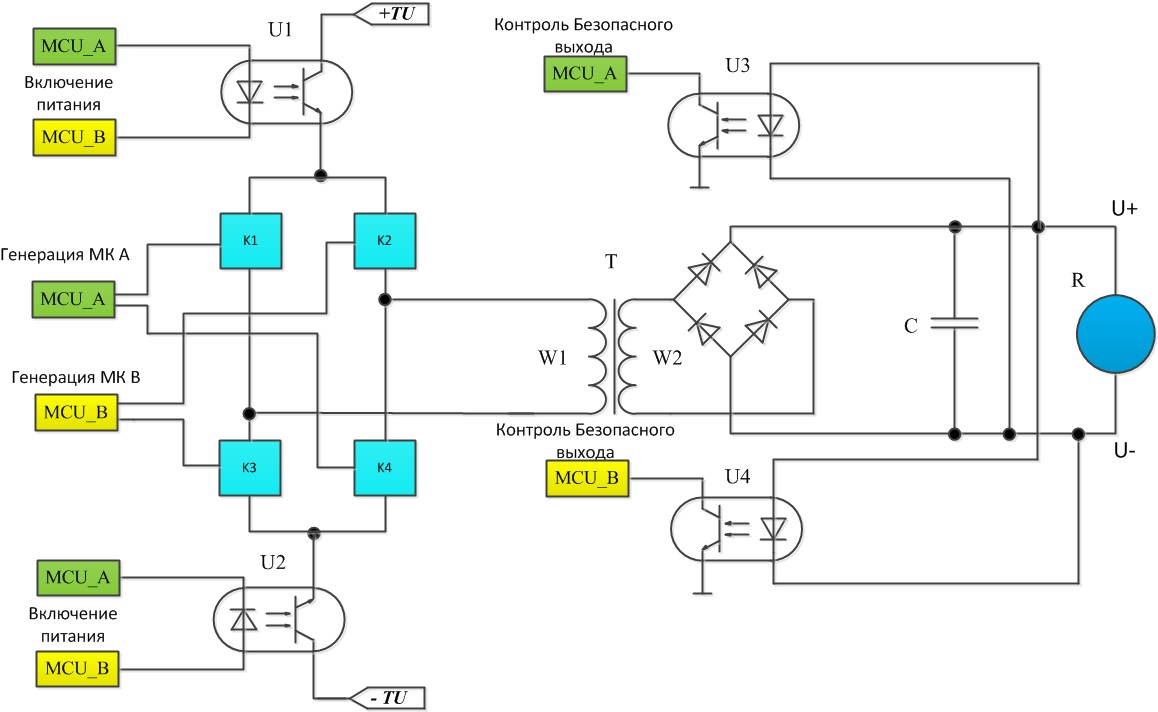

Considere métodos de proteção contra erros acidentais no exemplo de um dispositivo que controla um relé eletromagnético, mostrado na figura. Para determinar os métodos de proteção, é necessário identificar falhas perigosas no equipamento. Como você sabe, o relé é controlado pelo fornecimento de tensão ao seu enrolamento; nesse caso, uma falha perigosa para este dispositivo será a ocorrência não autorizada de tensão suficiente para o relé operar. Este dispositivo é baseado na arquitetura 2 de 2. Nessa arquitetura, MCU_A e MCU_B devem receber comandos em redes fisicamente separadas.

Figura - Diagrama de emparelhamento seguro

Figura - Diagrama de emparelhamento seguroNa estrutura deste artigo, não descreveremos completamente a árvore de falhas; portanto, consideramos uma das cadeias de eventos mais prováveis que levam a uma falha perigosa:

- O optocoupler U1 rompe

- A chave K2 rompe

- O transformador rompe

A intensidade do início dos eventos desse tipo é determinada pela fórmula

. Como todas as três falhas estão relacionadas, a intensidade dessa cadeia será determinada pela fórmula

. Sob premissas grosseiras, a taxa de falhas dessa cadeia é menor que (10e-15) 1 / h, assumindo que as falhas possam se acumular dentro de 24 horas.

Vamos considerar mais uma das falhas: falha de MCU_A e MCU_B para que elas “aleatoriamente” gerem uma sequência de pulsos na saída.

Por "caminho aleatório", o microcontrolador executa pelo menos nove comandos (três entradas na porta), enquanto a tensão de saída será detectada por dois microcontroladores e um erro será gerado entre os comandos recebidos e os "comandos emitidos". A intensidade desses eventos é extremamente baixa, pois: dois MKs terão que executar 9 comandos simultaneamente (sem mencionar que os MKs terão que escrever valores opostos às portas, em determinados intervalos, para gerar a tensão necessária para o relé operar na saída).

Em conclusão, deve-se notar que, como métodos para aumentar a segurança funcional, recomenda-se aplicar:

- diversificação de software e hardware;

- autodiagnóstico de todos os recursos do microcontrolador (RAM, ROM, ALU, registros de trabalho etc.), bem como nós do dispositivo;

- redução dos parâmetros dos elementos do circuito em relação aos valores-limite (desclassificação), para garantir melhores características operacionais e reduzir a probabilidade de falhas.

Todos esses métodos podem ser usados no desenvolvimento de dispositivos que atendem aos requisitos do CE.

P.S. No exemplo considerado, para reduzir a probabilidade de falhas devido a um motivo comum, um dos microcontroladores pode ser substituído pelo FPGA.

Obrigado a todos pela atenção (este é o meu primeiro artigo)!