Em 10 de julho de 1962, o foguete Tor, com o primeiro satélite comercial de telecomunicações a bordo, foi lançado a partir do local de lançamento em Cape Canaveral. O Telstar-1 foi o início de uma nova era da astronáutica, que mostrou que o espaço pode trazer benefícios reais para as pessoas. Esse dispositivo aguardava um grande futuro, mas um dia antes, no céu, sobre o Johnson Atoll, localizado na parte desértica do Oceano Pacífico, a bomba atômica Starfish Prime explodiu. A explosão destruiu trezentos postes de iluminação no Havaí, localizados a mil e quinhentos quilômetros, e também criou uma enorme quantidade de elétrons livres, captados pelo campo magnético da Terra no cinturão de radiação artificial. Cada vez que o Telsat-1 passava por esse cinturão, um enchimento avançado de transistor ganhava uma dose de radiação e, em novembro de 1962, ele parou de funcionar. A história da proteção dos eletrônicos espaciais contra radiação começou com um estudo das consequências desse incidente.

Felizmente, eles começaram a se envolver rapidamente em explosões nucleares em grandes altitudes, mas mesmo sem elas há trabalho suficiente e os requisitos de confiabilidade e durabilidade apresentados aos satélites modernos estão se tornando mais ambiciosos. É impossível falar sobre tudo, mas tentarei cobrir brevemente o passado e o presente dos microprocessadores espaciais de diferentes países. Por que exatamente microprocessadores? A maioria deles são informações sobre eles e são melhor compreendidos por não especialistas. O artigo acabou sendo longo, então eu o dividi em duas partes: uma história antiga no exemplo dos EUA e da Europa (abaixo do corte) e moderna - no exemplo da Rússia (

aqui ). Vamos lá!

Regras do jogo

Vamos começar com termos e definições. Por "microprocessador", quero dizer um microcircuito ou um conjunto de microcircuitos de alto grau de integração, projetado para executar programas. O primeiro microprocessador de chip único popular foi o Intel 4004 de quatro bits, lançado em 1971 - isso ocorre depois que os americanos pousaram na lua, então, com essa definição, os computadores de bordo da era da exploração espacial heróica desaparecem de cena, deixando-nos apenas “cavalos de trabalho” chatos. No entanto, muito foi escrito sobre computadores de bordo da era heróica, inclusive sobre Habré.

Aqui ,

aqui e

ali . Eles, por regra, foram projetados para uma missão específica, tinham algum tipo de sistema de comando e profundidade de bits de 13 bits, depois 17 e 21 - em geral, não tente repeti-lo em casa. A unificação começou com cortes no orçamento após o final da corrida lunar e com a implantação simultânea de várias constelações de satélites. Como resultado, quase todas as partes interessadas chegaram a um número limitado de chips universais usados onde quer que eles acabassem.

O segundo ponto importante é a disponibilidade de informações. A indústria espacial nunca foi particularmente aberta. O primeiro satélite, o acesso do astronauta à lua ou o número de satélites na constelação GLONASS é um anúncio simples e compreensível, mas é difícil se gabar das características do consumidor do design do transmissor de rádio no Sputnik-3. Adicione o segredo tradicional de quase-guerra de cima - e sabemos sobre o processador RAD750 que "existem mais de 150 deles" e apenas uma dúzia de satélites nos quais ele se encontra. Uma citação típica de publicações científicas especializadas escritas nos anos setenta é mais ou menos assim:

“Um registro de turno PMOS / SOS de 32 bits e resistente à radiação também foi construído e testado; no entanto, os dados de teste neste circuito são classificados. ” Sobre dados abertos sobre satélites e microcircuitos russos (e, é claro, eu uso apenas dados abertos), eu nem quero começar; as migalhas existentes geralmente acessam a Internet por supervisão. As publicações científicas nos poupam um pouco - especialmente se você sabe o que está procurando. O banco de dados on-line do IEEE é simplesmente um depósito para o historiador da eletrônica; com os arquivos das revistas e conferências científicas soviéticas e russas, a situação é radicalmente pior do que com os estrangeiros, mas também sem esperança. O ponto negativo das publicações é que, através delas, é difícil rastrear a conexão entre microcircuitos e sua aplicação, mas informações interessantes sobre o design de microcircuitos podem ser encontradas. Total: o artigo não pretende ser completo, é uma coleção de exemplos pelos quais se pode acompanhar o desenvolvimento e apresentar o estado atual dos microprocessadores e microcontroladores para aplicações espaciais.

A terceira coisa a concordar - não compararei o desempenho do processador do rover com um iPhone. Há um pouco de diversão nisso, mas a diferença de desempenho não é de uma vida boa, ela tem razões objetivas: um longo ciclo de desenvolvimento, outros requisitos de confiabilidade, longa certificação e teste de tudo, desde a tecnologia de fabricação de chips até a montagem do satélite. Obviamente, os desenvolvedores de espaço sempre querem obter o máximo poder de computação - para processar informações a bordo, economizando a largura de banda do canal de rádio -, mas muitas vezes outras prioridades são mais importantes. É por isso que dez anos podem passar da conclusão do desenvolvimento até o primeiro voo e, portanto, todo mundo adora soluções que já voaram - há muito menos problemas com elas. Como resultado, a vida espacial dos microcircuitos espaciais pode ser de trinta a quarenta anos, o desenvolvimento de uma nova geração pode começar mesmo antes do primeiro vôo do anterior, e agora os processadores desenvolvidos nos anos noventa ainda estão iniciando. Notarei imediatamente que o design da espaçonave está se tornando cada vez mais complicado, e agora pode haver dezenas de computadores a bordo com requisitos muito diferentes: você precisa processar matrizes de imagens o tempo todo e pesquisar alguns sensores uma vez por hora.

Quarto, um breve lembrete dos efeitos da radiação no espaço sideral. Um lembrete de tamanho médio

está aqui , mas muito longo -

aqui .

Os efeitos de uma dose completa de radiação estão associados ao acúmulo de carga elétrica nos dielétricos e na interface entre um dielétrico e um semicondutor; Estamos interessados principalmente em óxido de porta e isolamento lateral de transistores MOS. Esses efeitos se manifestam como uma mudança na tensão limiar dos transistores (para canais p, um aumento no valor absoluto, para canais n geralmente diminui, mas mais tarde você verá nuances), uma diminuição na mobilidade dos portadores de carga (diminuição da velocidade do circuito) e vazamentos nos transistores de canal n ( entre o dreno e a fonte de um transistor e entre diferentes transistores), levando a um aumento no consumo de energia estática.

Os efeitos únicos são devidos ao fato de que quando uma única partícula carregada entra no transistor, parte da energia dessa partícula é transferida para o material do microcircuito e nele formam-se pares livres de elétrons-orifícios. Alguns desses pares são separados no microcircuito por um campo elétrico e "vê" um pulso de corrente curto, "trazido" por uma partícula externa. Além disso, esse pulso atual pode alterar o valor registrado na célula de memória, ir para a entrada do elemento lógico ou fazer algo catastrófico, por exemplo, para romper a porta do transistor ou abrir a estrutura do tiristor parasita e criar uma falha de terra local com energia.

Os efeitos do deslocamento são devidos ao fato de uma partícula de entrada não apenas criar pares de elétrons-buracos, mas também interagir diretamente com átomos de uma substância, arrancando-os das posições corretas na estrutura cristalina. Para transistores comuns, esses defeitos locais não são terríveis, mas levam a danos significativos em dispositivos optoeletrônicos, semicondutores bidimensionais e transistores em nanoescala.

Ainda existem

efeitos na taxa de dose , mas eles têm aplicações principalmente não comerciais, por isso não vou falar sobre eles.

O estágio inicial - o exemplo dos Estados Unidos

O fato de eu não conseguir descobrir com segurança qual microprocessador foi o primeiro a bordo da espaçonave era bastante previsível. Os dados públicos estão disponíveis apenas em missões científicas conhecidas, e eles geralmente são colocados nos mais confiáveis e verificados, ou seja, discretamente trabalhados com antecedência em satélites mais baratos. Sabe-se que os computadores de bordo Viking e Voyager foram montados em lógica discreta, mas foi neles que a padronização e reutilização de componentes começaram. A Voyager é interessante por ter sido o primeiro dispositivo a usar memória semicondutora em vez de núcleos magnéticos. Além disso, era um CMOS SRAM volátil, ou seja, as informações nele são apagadas se a energia for perdida. Como os engenheiros conseguiram convencer a gerência a assumir esse risco? Primeiro, sem uma nova memória, não faria sentido aplicar uma lógica rápida do CMOS. No espaço, a tecnologia CMOS era mais do que oportuna: apesar de os circuitos CMOS serem mais lentos que os bipolares e muito mais sensíveis à descarga eletrostática, eles toleravam extremos de temperatura, tinham baixa sensibilidade ao ruído e consumiam radicalmente menos energia, que geralmente está a bordo houve uma escassez. Em segundo lugar, como um backup da fonte de alimentação, a voltagem da saída RTG foi diretamente trazida para a memória, raciocinando razoavelmente que, se algo acontecer com o gerador, os problemas de memória não serão mais relevantes.

Figura 1. Placa com memória semicondutora com Voyager.

O primeiro - RCA 1802

A primeira nave espacial que encontrei na qual não eram microcircuitos de médio grau de integração, mas um microprocessador monolítico (RCA 1802 de 8 bits) é o satélite Magsat lançado em 30 de outubro de 1979. Dado que os primeiros RCA 1802 comerciais foram lançados em 1975, isso significa que eles atingiram a NASA antes das prateleiras das lojas - o que, em geral, era uma prática normal nos primeiros dias do Vale do Silício.

Como um pequeno exemplo dessa época, citarei um artigo de EE King, "Efeitos da dose total no microprocessador de 1802", IEEE Transactions on Nuclear Science, 1977. O artigo compara o efeito da dose de radiação em quatro variantes de 1802: duas comerciais, uma amostra experimental produzida em um substrato de silício sobre safira (SPS) e uma amostra produzida por um processo especial projetado para aumentar a resistência à radiação.

Figura 2. Mudança da tensão limiar de ambos os tipos de transistores sob a influência da dose de radiação. C1 e C2 são chips comerciais, S é um chip no SPS, X é uma amostra especial.

Pode-se ver pela figura que tanto as amostras comerciais quanto o chip KNS em doses de radiação bastante pequenas (8 a 15 crad (Si)), o limiar dos transistores de canal n se torna menor que zero e os circuitos lógicos simplesmente param de mudar. Ao mesmo tempo, um processo técnico especial tornou possível obter uma resistência superior a 1 Mrad (Si), ou seja, duas ordens de magnitude a mais. Mais uma vez, observo que o ano é apenas 1977, e chips especiais já foram desenvolvidos e produzidos. No entanto, o RCA 1802 descrito foi provavelmente o primeiro sinal, porque nas lembranças dos participantes do desenvolvimento do próximo grande dispositivo da NASA - Galileu - encontrei uma história de que, na época da escolha da arquitetura da eletrônica de controle em 1977, 1802 era o único microprocessador monolítico resistente a radiantes a preço acessível.

É importante observar que eles já tentaram usar os chips mais comuns no espaço - e continuam a fazê-lo com sucesso agora. Para muitas aplicações, nem extrema confiabilidade, nem alta resistência à radiação, nem a completa ausência de falhas são necessárias - apenas a ausência de falhas em um período de tempo razoável é importante, e muitos chips comerciais atendem a esse requisito, sendo várias ordens de magnitude mais baratas do que as projetadas especialmente. irmãos Para uma constelação de satélites de várias centenas de dispositivos em órbita baixa, mesmo a presença de falhas não muito frequentes não é crítica, em contraste com o custo. E somente onde a segurança do país depende do funcionamento dos microcircuitos, a vida dos astronautas, ou pelo menos o destino de uma missão científica de vários milhões de anos, é impossível sem chips resistentes a radiações. É claro que existem abordagens mistas, quando os sistemas mais críticos são executados em chips resistentes a radiantes, e o restante em sistemas convencionais e também conhecido como bom dado, quando o fabricante pega os mesmos cristais usados em produtos caros resistentes a radiantes, empacotando-os em caixas plásticas baratas e não realiza testes de ponta a ponta, economizando no preço várias vezes. Existem empresas que se dedicam especificamente ao teste de chips comerciais para encontrar entre elas aquelas que se revelaram acidentalmente resistentes a radiações. Mas voltando a Galileu e 1802.

Figura 3. Lançamento do Galileo com ônibus espacial. Os computadores de bordo do ônibus espacial, criados nos anos setenta, funcionavam em microcircuitos de pequeno grau de integração, e apenas durante uma grande atualização, já feita no segundo milésimo, o PowerPC 750 resistente a radiantes 386-e, 1802-e civil.

O Galileo, devido a vários problemas, voou apenas em 1989, mas foi projetado quase imediatamente após os Voyagers e usando suas melhores práticas. “1802 ninguém na equipe de desenvolvimento realmente gostou”, porque soluções discretas, embora mais complicadas, eram muito mais rápidas. Como resultado, suas vantagens ainda eram superadas pelos contras, e o subsistema de comando e dados do dispositivo (Subsistema de Comando e Dados) foi construído em 1802, e o subsistema menos carregado, porém mais exigente, relacionado à velocidade de controle de manobras (Subsistema de Controle de Atitude e Articulação) foi controlado por um computador de 16 bits montado a partir de chips bipolares de quatro bits Am2900 (equivalente soviético - série 1802).

O Galileo é adicionalmente importante para a nossa história, pois foi o primeiro dispositivo em que o problema de falhas únicas foi levado em consideração no design. Em microcircuitos fabricados de acordo com padrões rígidos de projeto, eles quase não apareceram, e ninguém sabia da existência deles até que as sondas de pesquisa chegassem aos cinturões de radiação de Júpiter. A magnetosfera de Júpiter é tão grande que parte de seus satélites (Europa, Io e Ganimedes) está dentro dela! Os campos magnéticos de Júpiter aceleram íons pesados para uma energia colossal, cuja fonte é Io vulcanicamente ativa. Tais condições monstruosas acabaram sendo suficientes para causar mau funcionamento, mesmo nos microcircuitos antigos da Pioneer, mas quanto menores os padrões de projeto, menos energia é necessária para mudar a memória!

Figura 4. Uma imagem da radiação ao redor de Júpiter. Fonte: Hans Huybrighs, “A viabilidade de observações in situ das plumas de vapor de água da Europa”, 2015

Em 1977, quando o projeto Galileo começou, os Voyagers ainda não haviam chegado a Júpiter e todos os dados de radiação disponíveis estavam relacionados apenas aos Pioneiros. Alguns de seus erros misteriosos foram posteriormente classificados como falhas únicas, mas mais tarde, e até o momento, nem códigos de autocorreção nem outras formas de encontrar e corrigir erros foram incorporados ao equipamento de bordo do Galileo. Após a provável causa das falhas nos Pioneers and Voyagers (1982), todos os componentes eletrônicos do Galileo, selecionados para resistir à dose de radiação, foram urgentemente enviados ao acelerador: descubra como eles irão lidar com um novo problema. Os resultados foram decepcionantes: se 1806, realizado usando uma tecnologia relativamente antiga, se comportou normalmente, no conjunto de microprocessadores bipolares progressivos 2901, de 20 a 50% dos acertos de partículas carregadas causaram problemas e foi impossível iniciá-lo. O que fazer Foram encontradas duas opções:

- Experimente o mais recente computador de bordo resistente à alegria baseado na arquitetura 1750A e recompile todo o software, depois de escrever o compilador. O custo dessa opção foi estimado em 20 milhões de dólares (os então dólares, eram significativamente mais caros que os atuais).

- Para solicitar com urgência o desenvolvimento de análogos tolerantes a falhas dos chips com problemas 2901. Nesse caso, todo o software testado repetidamente não pôde ser refeito. A Sandia Labs estimou o desenvolvimento de novos chips em 5 milhões, e uma decisão foi tomada.

NASA Tech Briefs, Volume 10, Edição 3 fornece alguns detalhes sobre os chips desenvolvidos pela Sandia Labs: eles não eram bipolares como o original, mas o CMOS, havia nove tipos deles (dos quarenta chips da série original) e foram usados para obter tolerância a falhas transistores mais largos do que o necessário, bem como resistores nos circuitos de feedback dos elementos de armazenamento.

Recuar sobre falhas únicasFigura 5. Esquema de uma célula de memória estática de seis transistores (6T SRAM)

Quando um SLC entra no dreno de um transistor fechado, um pulso de corrente de ionização surge e dois processos começam na célula: disparo de feedback positivo e dissipação de carga induzida.

Deixe o impacto ocorrer em um transistor fechado M2, no dreno do qual um pulso de corrente apareceu como resultado. O transistor M1 neste momento está completamente aberto e possui uma pequena resistência, ou seja, a corrente TZCh induzida por ele vai para o solo. No entanto, a capacidade do nó nQ pode ser pequena o suficiente para carregar em alta tensão, o que levará à comutação do segundo inversor (M3-M4), que, por sua vez, alternará o primeiro inversor através do feedback. Esta é uma falha induzida por radiação (problema único, SEU). A instalação de resistores no circuito de feedback permite desacelerar o processo de feedback e dar tempo suficiente à carga para resolver.

Projeto SA3000 - Resistente a Radiantes 8085

O processo de desenvolvimento de microcircuitos resistentes a radiantes na época parecia que você pode seguir as publicações científicas. Como exemplo, peguei um artigo de W. Kim et. al., «Radiation-Hard Design Principles Utilized in CMOS 8085 Microprocessor Family», 1983 IEEE Transactions on Nuclear Science. Sandia Labs , SA3000 – Intel 8085 ( SA3001 SA3002 RAM Intel 8155 ROM Intel 8355). , Intel , . , . RHBP , – - , n+- . , – RHBD .

NMOS- , , . 700 (Si) 30 (Si). , . Sandia Labs ( ), -. , -, . , .

.

- n- 2 ( 1 ) p- -0.5 -4 ( -1 ). - , , , , .

- , -4 5 p- , , Sandia Labs , 10 . , , NMOS CMOS , .

- , p- , NAND ( p- ) NOR ( ).

- , . , , . , , , .

( ) , , 10 , , . , 10 5 .

«» : – , – , , – , - . Sandia Labs pin-to-pin 18000 6500, . : , . , , , - .

- , . , - . .

, , JFET , . 1984 , DARPA GaAs MIPS — RCA, McDonnell Douglas CDC-TI. 30 , “ ”. , GaAs- Am2900, 1802 , .

, 1984-1994 GaAs , «» 6500 . , GaAs , 6500 , - (). GaAs – - , . .

RISC-

GaAs RISC-, CISC . , RISC- , . « » – ARM, MIPS, SPARC, POWER – , -, - , -, , – , .

1980 US Air Force Mil-Std-1750A, 16- . , , USAF . , , JOVIAL (Mil-Std-1589) (Mil-Std-1815A). JOVIAL, , ( , , ).

USAF, NASA, ESA . 1750- ( , , , bit-slice 2901 , Galileo) , Cassini . Mil-Std-1750A MA31750 Dynex Plessey - . IT , 1750A USAF 1996 , , 16 32- , . , , 1750 . , Rosetta, 2004 , “”, 2013.

, : «1802+8085» «1750+386», 386 Sandia Labs Intel; 386 , Hubble , Space Shuttle. - MIPS-, Mongoose-V, New Horizons, - RAD, POWER. Phoenix, Opportunity, Spirit Curiosity, Spitzer Kepler – , NASA . – RAD5500 – 2016 . – HPSC (High Performance Spaceflight Computing), Boeing ARM-, NASA USAF. , (RTEMS ), , – Yocto Linux.

, , – HPSC , , , . Mongoose-V – MIPS , RAD6000 , PowerPC601. , , ; . , , , .

Figura 6. Comparação dos cristais PowerPC750 e RAD750. Os chips são fabricados com os mesmos padrões de design, e sua área ao mesmo tempo quase dobra. Preste atenção ao layout quase idêntico do bloco - é o que acontece quando a compatibilidade de baixo nível é garantida. Grandes diferenças no tamanho dos blocos de memória sugerem o uso de células de memória resistentes a radiações de multi-transistores (10T em vez de 6T) com redundância incorporada.

Uma mudança de paradigma - o caso da Agência Espacial Europeia

A história da engenharia européia de processadores espaciais está indissociavelmente ligada ao nome do engenheiro sueco Jiri Gaisler. Ele entrou na ESA em meados dos anos 80 e começou a desenvolver os primeiros microprocessadores espaciais europeus proprietários. No início, era um americano licenciado 1750A, depois seu próprio desenvolvimento baseado no mesmo sistema de comando (produzido na Inglaterra) - para manter a compatibilidade com o software já escrito. E, como este é um site de TI, vamos ver que tipo de software é:

Ferramentas proprietáriasCompilador Ada do TLD (EUA)

Código abertoO sistema de compilação GNU para 1750 foi inicialmente composto por duas partes principais.

um conjunto de ferramentas desenvolvidas pelo CNS sob o contrato da Agência:

- Compilador GNU C (gcc-2.7.2)

- Linker, assembler, arquivador, etc (binutils-2.7)

- Biblioteca c independente

- Biblioteca POSIX-Threads (IEEE 1003.1c-1995) (um executivo preemptivo em tempo real)

- Depurador GNU (gdb-4.16) para 1750

Um conjunto de ferramentas desenvolvidas internamente na Agência ou disponíveis a partir de fontes externas, nomeadamente:

- CRTX (o pequeno executivo cíclico / síncrono em tempo real da SmartCom - externo)

- Simulador autônomo 1750 (O. Kellogg sim1750-2.3b - externo)

- wxIDE (um ambiente de desenvolvimento integrado portátil baseado em J. Smart wxWindows 2.65 - interno)

Um ponto importante que distingue o trabalho da Agência Espacial Europeia em termos de software é o suporte e pagamento sistemáticos e direcionados para a criação de produtos de código aberto, bem como a criação de ecossistemas para reutilização do desenvolvimento e redução de custos. Não apenas para software: para microcircuitos resistentes a radiantes, o Instituto IMEC belga cria e suporta para os interesses da ESA plataformas de desenvolvimento DARE (Design Against Radiation Effects), que incluem rotas de design, PDKs adaptados e grandes conjuntos de blocos IP digitais e analógicos em seis diferentes processos de fabricação (350, 180 90 e 65 nm). Essas plataformas não são de código aberto, mas são licenciadas para todos os artistas de contato da ESA, se necessário.

ERC32 - o primeiro totalmente europeu

Agora, de volta a Jiri Geysler. A primeira geração de seus próprios processadores europeus 1750A em arquitetura (um kit de três chips foi concluído em 1989, o MA31750 totalmente integrado em 1991) foi desenvolvida de olho na missão Rosetta, que se tornaria um dos carros-chefe de um amplo programa científico europeu-americano, que também incluía o telescópio " Hubble ”e missões para estudar o sol e os planetas.

"Rosetta" é um aparelho com um destino longo e complexo. O projeto começou em 1986, junto com os Estados Unidos, e deveria reutilizar muitas partes dos dispositivos Mariner MkII (as pernas da 1750A estão crescendo daqui), mas depois de um tempo o Congresso dos EUA cancelou o financiamento para a parte americana do programa (posteriormente convertida em um orçamento mais baixo para a sonda Cassini), e A Europa permaneceu por conta própria. Em 1994, quando ficou claro que a missão original, que incluía a entrega de matéria cometária à Terra, por si só não podia ser puxada, as tarefas da missão foram reformuladas; dez anos depois, em 2004, Rosetta iniciou sua jornada para o cometa Churyumov-Gerasimenko e, em 2014, quando o alcançou, as notícias puderam ser lidas, inclusive sobre circuitos antigos com o desempenho de uma calculadora de bolso. E ainda não há notícias suficientes sobre os processadores de pilha no módulo de aterrissagem Philae que o hardware implementa a linguagem Forth.

O destino de Rosetta mostrou claramente à ESA que, dependendo dos parceiros americanos, não é a melhor idéia, e a agência começou a investir bastante dinheiro em programas para alcançar a independência tecnológica ou, em nossa opinião, a substituição de importações. Trinta anos depois, esses programas continuam existindo, recebendo um ímpeto relativamente novo relacionado ao desejo da Europa de ter acesso ao mercado espacial russo e, mais importante, ao mercado espacial chinês, independentemente das restrições, sanções e guerras comerciais dos EUA com a China.

Tendo adquirido experiência suficiente, a equipe da ESA assumiu uma tarefa mais ambiciosa: um processador de 32 bits. Naquela época, ainda estava na moda criar suas próprias arquiteturas RISC, mas a ESA não alocou dinheiro para esse entretenimento, sugerindo que os desenvolvedores escolhessem um dos ISAs existentes, além de não proprietários e, de preferência, com um bom ecossistema de software. Após algum estudo e discussão subsequente com algumas dúzias de potenciais contratantes da ESA, a escolha recaiu sobre o SPARC, que possui todas as qualidades necessárias e já é distribuído gratuitamente no início dos anos 90 por um consórcio respeitável liderado pela Sun e Fujitsu. Um fato engraçado: o ARM foi considerado, mas foi rejeitado devido à pequena quantidade de software. Entre outros requisitos interessantes para o processador estava o suporte de hardware para a linguagem Ada para acelerar o trabalho de software já escrito para o 1750A, bem como a presença de modelos VHDL para acelerar o desenvolvimento de sistemas baseados em processador.

Um ponto fundamentalmente novo nos requisitos de desenvolvimento foi que o próprio microprocessador não foi desenvolvido como um chip, mas um modelo de alto nível do processador em VHDL. Isso foi feito para não depender de um fabricante de chips específico e garantir a disponibilidade do processador por muitos anos, mesmo que algo aconteça com a fábrica selecionada. De acordo com a tradição americana, o design do núcleo foi baseado no processador comercial Cypress CY601, e a fábrica francesa Temic Semiconductor (processo de fabricação volumétrica resistente a radiantes com padrões de design de 800 nm) foi responsável pela resistência à radiação. Em vez dos três anos planejados, o projeto durou cinco (1992-1997), o design foi finalizado na décima (!) Iteração dos chips de teste, Ada teve que ser abandonada - mas, como resultado, o projeto foi considerado bem-sucedido. O design resultante foi chamado ERC32, um kit de microprocessador de três chips que entrou no mercado sob os nomes TSC691-693 e, mais tarde, o projeto foi executado em um único chip como TSC695 (20 MHz, 14 MIPS, 4 MFLOPS, 0,5 W).

Além da implementação usual do SPARC, o ERC32 implementa detecção de falhas e correção de software. 99% dos gatilhos na unidade inteira registram, 100% dos gatilhos na FPU e barramentos externos estão equipados com paridade. Os erros detectados causam seis tipos de interrupções, cuja resposta é determinada programaticamente. No caso mais simples, o tratamento de interrupção consiste em repetir a instrução com falha; no pior caso, pode ser uma reinicialização do computador de bordo. Além disso, a instrução NOP é modificada de forma que, em vez de fazer nada, verifique a soma de verificação recebida como o código de código XOR de todas as instruções anteriores. Se a soma não corresponder ao valor esperado (obtido na compilação), também será chamada uma interrupção. Concluindo a descrição do ERC32, observo que não há cache, ou seja, os desenvolvedores do processador enviaram esse grande problema para outras pessoas.

As medidas propostas para detectar falhas levaram a um aumento na área em 15%. Ou 130%, se considerarmos a inclusão de dois ERC32 em uma configuração duplicada, para a qual também havia suporte de hardware.

ERC-32 e o segmento russo da ISS

O primeiro dispositivo que utilizou o ERC32, sem dúvida, merece uma história separada, pois foi o primeiro caso de uso de uma unidade estrangeira em equipamentos de missão russa e também porque mostra claramente como projetos importantes não devem ser realizados.

Em 1992, devido a dificuldades adicionais na construção da estação espacial de longo prazo EUA-Europa Freedom, a ESA iniciou negociações sobre a possibilidade de sua participação no projeto da estação orbital russa Mir-2. O lado russo concordou, mas não tinha orçamento em 1992. Após dois anos de intensas negociações (a votação no Congresso dos EUA terminou com a pontuação 216-215), os projetos Mir-2 e Freedom se transformaram na Estação Espacial Internacional (ISS), como a conhecemos hoje. Enquanto isso, os acordos entre a Europa e a Rússia permaneceram em vigor, e a ESA lançou um projeto de um sistema de processamento de dados para o módulo russo “Dawn” (DMS-R, Sistema de Gerenciamento de Dados - Russo).

Os processadores disponíveis em 1995 - os resistentes a radiações 1750 e 386 - não atendiam aos requisitos de desempenho e, na carga do RAD6000, era necessário comprar placas de processador inteiras, o que não dava flexibilidade ao desenvolvimento. Outra opção era o ERC32, mas naquela época existia apenas na forma de modelos, e nenhum chip de teste em silício ainda havia sido feito. Não sei o que motivou essas pessoas, mas claramente não era a ideia de que algo poderia dar errado com um processador avançado

inexistente . E com ele, é claro, houve um atraso no cronograma (que foi ignorado por algum tempo usando análogos comerciais) e um mar de bugs (que era previsível para o primeiro grande projeto de uma pequena equipe de desenvolvimento), e os bugs foram mal documentados, mesmo sob constante controle direto. entre em contato com os desenvolvedores DMS-R e os desenvolvedores ERC32. Um dos bugs na FPU, que os desenvolvedores da RSC Energia não conseguiram localizar de forma alguma, acabou precisando ser contornado com as correções no sistema operacional.

Houve atrasos adicionais (em 1998, o financiamento espacial na Rússia não foi muito bom novamente), mas em 2000 os computadores de bordo desenvolvidos pela ESA foram colocados em órbita com sucesso e, desde então, trabalham dentro do bloco russo Zarya.

Figura 7. O computador de bordo do módulo ISS Zarya baseado no processador ERC32.

Em 1996, mesmo antes do final do projeto ERC32, começou o desenvolvimento de requisitos para seus herdeiros. O apetite dos programadores aumentou para 100-500 MIPS em vez de 10, e o sucesso retumbante do projeto original fez com que a Europa continuasse trabalhando com a arquitetura SPARC em um futuro próximo. A principal tarefa foi a criação de uma versão de chip único do ERC32, a mais promissora foi o novo núcleo do processador.

LEON-FT

A principal característica do projeto LEON-FT foi a tarefa inicial de criar não um produto final na forma de um chip, mas um núcleo licenciado na forma de um código vhdl e garantir tolerância a falhas em vez de dureza de radiação. A experiência do ERC32 mostrou que ele requer duplicação para uma operação confiável, e o próximo passo lógico foi desenvolver um sistema que não precisa dele. A solução para esse problema exigia não apenas detecção, mas também correção de falhas no nível do hardware, sem o uso de software. As idéias de tolerância a falhas e endurecimento por radiação por projeto não foram, obviamente, inventadas pelos autores do LEON-FT, mas antes deles essa abordagem foi considerada principalmente no nível do transistor, e eles foram os primeiros a desatar completamente a luta contra falhas únicas da implementação física do chip e fizeram o objetivo do projeto criar um chip estável em tecnologia comercial e disponível em um determinado momento - resolvendo o problema de obsolescência de processos tecnológicos e fechamento de fábricas. Assim, uma mudança de paradigma foi registrada: vinte anos antes de vermos o exemplo dos chips SA3000, o principal problema era a dose total de radiação, combatida com métodos tecnológicos, e falhas únicas foram consideradas de acordo com o princípio residual. Em 2000, o foco mudou, falhas únicas se tornaram o principal problema e o apego a uma tecnologia específica passou a ser visto como uma desvantagem, e não como um mérito, mesmo que a fábrica fosse testada e confiável. A propósito, agora o inglês (e nem uma palavra sobre Brexit) Dynex Semiconductor pertence aos chineses, e o francês Temic se tornou parte do microchip americano.

O núcleo LEON-FT foi escrito em VHDL e equipado com um configurador que permite escolher diferentes opções de proteção contra falhas únicas para diferentes partes do chip: para um arquivo de registro e memória cache (apareceu o cache!) Um / dois bits de paridade ou um código Hamming, além de forçar falta de cache, para acionar no caminho de dados a presença ou ausência de tripla redundância, para um pipeline (apareceu um pipeline) - a capacidade de redefinir e tentar novamente a partir de uma instrução com falha. Portanto, a única dependência da implementação física é apenas nos recursos da interface com blocos de memória personalizados que compõem o arquivo de registro. O crescimento da área central com proteção máxima, excluindo caches, é de cerca de 100%, considerando - cerca de 40%; com todas as opções desabilitadas, acabou sendo o núcleo do SPARC V8 lançado em código aberto como LEON (sem o prefixo -FT). Essa prática continuou ainda mais, e as versões subseqüentes do LEONx em uma versão instável foram estabelecidas em domínio público, e as versões configuráveis à prova de falhas do LEONx-FT foram licenciadas por dinheiro para criar microchips ou como Soft IP para firmware em FPGAs. De fato, como o LEONx-FT não está ligado à tecnologia de forma alguma, nada impede que eles sejam usados em FPGAs - é claro, se a condição (bastante rigorosa) para a ausência de falhas na memória que controla as conexões dos elementos no chip for atendida. No entanto, se essa memória não for SRAM, mas sim flash ou EEPROM, é uma idéia bastante realista, mesmo sem levar em consideração a existência de FPGAs tolerantes a falhas nos quais a memória de configuração é coberta por hardware com códigos de correção automática.

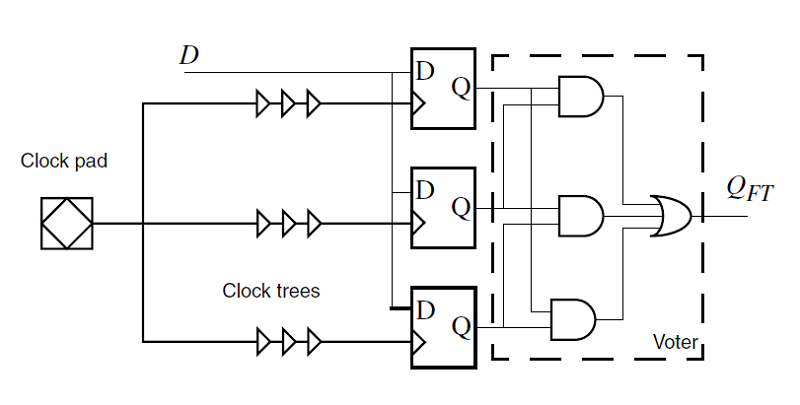

Figura 8. Gatilho troy.

Nota de projeto da biblioteca: para compatibilidade com qualquer biblioteca, o elemento de votação aqui é montado a partir de portas lógicas comuns. Obviamente, ele próprio não está protegido de falhas únicas de nenhuma maneira, mas é muito menos que um gatilho comum, o que significa que a probabilidade de entrar nele é menor e a falha é curta, mas não está bloqueada. Se isso não for suficiente, existem implementações especiais do elemento de votação no nível do transistor, mais resistentes a falhas do que a opção mostrada na figura, e elas podem ser adicionadas à biblioteca como primitivas. Nos padrões de projeto de 1000 a 100 nm, são possíveis várias implementações interessantes de elementos lógicos com maior tolerância a falhas, permitindo alterar minimamente o design lógico do microcircuito e não introduzir projetos triplos complexos. As opções mais populares são duplicação interna em elementos e filtragem interna (por exemplo, na forma de resistores em circuitos de feedback na memória).

Figura 9. Célula de memória DICE com duplicação embutida; Devido a feedbacks cruzados, uma falha só é possível se atingir simultaneamente dois inversores, o que é relativamente fácil de evitar. À direita estão as topologias de uma célula de memória comum e do DICE.

LEON-FT era um projeto de teste e não se destinava à comercialização; Esse desenvolvimento, bem como os produtos comerciais subsequentes - núcleos LEON2-FT - foram feitos por Geisler em sua própria empresa Gaisler Research, localizada em Gotemburgo. Os direitos exclusivos do LEON2-FT foram obtidos pela Atmel, que adquiriu a Temic, uma empresa ERC32; o produto resultante é o chip AT697, amplamente conhecido inclusive na Rússia, executado na tecnologia radiante especial Atmel e devido ao fato de a Atmel ser uma empresa americana sujeita a restrições de exportação e sanções. Em 2008, a Gaisler Research foi vendida aos americanos pela Aeroflex, depois a inglesa Cobham os comprou, depois o Brexit começou, e agora a Cobham está comprando algum investidor americano sob o uivo sobre a inadmissibilidade de desperdiçar o tesouro nacional e a defesa nacional. Essa é a história da substituição de importações e da independência tecnológica na Europa.

A versão atual - LEON5 - possui um pipeline de oito estágios, um preditor de ramificação e outros recursos dos microprocessadores modernos e, a partir da terceira versão, a Gaisler oferece não apenas núcleos de processador, mas também uma grande biblioteca de vários blocos de IP, permitindo que os usuários criem sistemas em um chip adequado para suas necessidades específicas. requisitos, bem como uma ampla variedade de softwares proprietários, de terceiros e de código aberto (uma descrição detalhada pode ser encontrada

aqui , os sistemas operacionais incluem VxWorks 6.9 e 7.0, RTEMS 4.10 e 5, além de Linux baseado no kernel 3.10 e 4.9).

Uma pequena digressão sobre economia e planejamentoLEON são considerados os chips espaciais de maior sucesso e grande escala. Ao mesmo tempo, a circulação total de ambas as variantes do ERC32 totalizou cerca de cinco mil unidades, e a circulação dos chips Atmel com base no núcleo LEON2-FT foi de cerca de mil e meia unidades. A American BAE Systems se vangloria de folhetos com 200 computadores de bordo com o RAD6000 e cento e cinquenta com o RAD750. É absolutamente claro que, com tais circulações, o desenvolvimento e a certificação de tais microcircuitos não podem ser justificados comercialmente a qualquer preço pelo microcircuito, e o desenvolvimento deve ser subsidiado pelo estado (ou, no caso da ESA, pela união dos estados). Além disso, a necessidade de subsidiar o desenvolvimento na maioria dos casos se aplica não apenas aos microprocessadores, mas também à maioria dos outros microcircuitos para aplicações espaciais, exceções são mais facilmente encontradas entre chips relativamente simples que podem ser desenvolvidos de maneira barata e vendidos em grandes quantidades pelos padrões espaciais. Por sua vez, isso cria as condições para o planejamento estratégico de longo prazo para o desenvolvimento da base de elementos espaciais, destacando as principais áreas e a reutilização da PI desenvolvida com dinheiro subsidiado. Nesse sentido, os modelos que operam nos EUA, Europa e Rússia diferem apenas nos detalhes da implementação e no nível de organização do processo.

Divisão do trabalho

Como eu disse acima, os núcleos IP LEONx-FT resolvem apenas o problema de falhas únicas; a proteção contra a dose total e o efeito tiristor recai sobre o usuário, que deve escolher um FPGA estável ou uma combinação de tecnologia e bibliotecas. Gaisler GR712, «».

. GR712 – LEON3-FT. – 180 TowerJazz. – RadSafe, Ramon Chips ( , «»). RadSafe . GR716 – LEON3-FT – IMEC, IP 180 UMC. GR740 – , LEON4-FT – 65 ST Microelectronics, . , , , .

10. , MA31750 , GR740 ( 65 STM, , 250 , 459 MIPS/, 22.7 MFLOPS).

, . -, , , . -, , , . -, ( ), , .

–

. , , , .