Esta é a segunda parte do artigo sobre a história dos microprocessadores para aplicações espaciais. A primeira parte está

aqui . Nele, nos exemplos de microcircuitos americanos e europeus, analisamos a história do desenvolvimento de chips resistentes a radiantes desde os primeiros processadores de cristal único até o final do segundo milésimo, quando os padrões de design para desenvolvimentos espaciais eram próximos a 100 nm.

O próximo grande passo para garantir a resistência à radiação veio com a transição para menos de 100 nm, onde quase toda geração de tecnologia traz novas questões: mudança de materiais, mudança de requisitos de topologia, potência estática cresce (vazamentos sem radiação, que se tornam ainda piores sob uma dose) , o significado dos efeitos únicos, que se transformam em múltiplos, continua a crescer. Essas tarefas exigiram o desenvolvimento de novas abordagens e, surpreendentemente, um retorno parcial às antigas, porque algumas das coisas que se mostraram excelentes nos padrões de 1-0,18 μm não funcionam em padrões mais refinados. Por exemplo, em tais tecnologias, para aumentar o rendimento, é proibido fazer transistores em anel amados pelos projetistas de chips resistentes a radiações. Vou contar como os designers lidam com novos desafios com o exemplo da Rússia - e, ao mesmo tempo, compararei as realizações de nossos compatriotas com os sucessos de colegas estrangeiros e mostrarei o que esperar no futuro próximo.

Modernidade - o exemplo da Rússia

Escolhi a Rússia para ilustrar o estágio atual, não porque os desenvolvimentos russos se destacam em escala global, mas porque não faz sentido escrever sobre algo mais antigo. Havia muitos microcircuitos legais na URSS, mas todas as informações sobre produtos de uso duplo foram mantidas em segredo, e agora você pode encontrar apenas bicicletas da forma "após o acidente de Chernobyl, Gorbachev pessoalmente procurou os desenvolvedores dos robôs para lidar com os escombros e trouxe de volta o microprocessador radiante VM6" (de fato, as palavras-chave "mantém a operabilidade em uma ampla variedade de fatores mecânicos, climáticos e

outros " estão contidas na descrição não "xxxxxBM6", mas 1806BM2). Existem pequenas coisas aleatórias: na série de 1839, de acordo com entrevistas disponíveis de desenvolvedores criados para necessidades industriais, existe um chip N1839VZh2 - um elemento de votação. Em computadores convencionais, o elemento majoritário não é necessário para nada, mas se você pesquisar um pouco no Google, poderá descobrir que a série 1839 são computadores de bordo dos satélites GLONASS-M. É uma pena que essa quantidade de dados não permita escrever nada. Além disso, na época do advento dos microprocessadores radiantes, a URSS já havia adotado firmemente o caminho de copiar desenvolvimentos ocidentais, de modo que inovações especiais ainda não deveriam ser esperadas.

Os anos noventa em microeletrônica foram marcados pela sobrevivência e compressão dos últimos sucos da herança soviética. Ocorreu uma reviravolta condicional em 2003, que se tornou um evento: no NIISI RAS, foi lançada sua própria fábrica com padrões de projeto de 500 nm, os primeiros processadores da família Multicor entraram na série Angstrem, a empresa Digital Solutions foi fundada, no primeiro antes disso, um distribuidor de Milandre abriu um centro de design. Em seguida, veio o programa-alvo federal “Desenvolvimento da base de componentes eletrônicos e radioeletrônicos” para 2008-2015, que não alcançou as metas estabelecidas (45 nm em 2015, vendas de 300 bilhões de rublos etc.), mas ainda assim conseguiu ajudar seriamente a microeletrônica russa. Atualmente, na Rússia, existem aproximadamente 150 a 200 centros de projeto envolvidos no desenvolvimento de circuitos integrados, de gigantes como o Micron a equipes de cinco a seis pessoas envolvidas em nichos de mercado. A grande maioria dessas equipes de alguma forma trabalha com pedidos do governo e cria produtos de uso duplo. Além disso, a década entre 2003 e 2014 passou não apenas no desenvolvimento de novos microcircuitos russos e nas tentativas de preencher a lacuna já catastrófica com fabricantes estrangeiros; uma tarefa mais difícil do que criar novos microcircuitos, foi a tarefa de convencer os fabricantes de sistemas a iniciar sua aplicação. Depois de esgotar a lista de pendências soviética, a maioria dos técnicos de sistema mudou-se densamente para componentes importados que eram melhor fabricados, melhor documentados, mais confiáveis, mais acessíveis - em geral, realmente não havia razão para fazer o contrário. Em seguida - um círculo vicioso de compatibilidade com versões anteriores e reutilização da lista de pendências existente, graças ao qual os desenvolvimentos domésticos mais rigorosos ainda continuavam a permanecer no mar. Para ser justo, havia e há empresas entre os fabricantes de equipamentos de rádio de bordo em princípio e cooperando consistentemente com os desenvolvedores domésticos de componentes eletrônicos, mas, em geral, a situação na indústria era mais ou menos assim:

Uma citação de uma entrevista com Nikolay Testoedov, diretor do maior fabricante de espaçonaves russa ISS, em homenagem a Reshetnev:

- O satélite de comunicações militares Blagovest possui uma grande parcela de componentes estrangeiros?

- Lá, o índice também não era muito bom, porque até 2014, quando não havia riscos ou restrições , comprávamos um grande número de componentes estrangeiros. O momento da criação de satélites para o Ministério da Defesa foi mais importante.

Parece que eu não entendo algo na definição da palavra "risco". Porém, uma vez que em veículos militares você pode usar componentes importados, podemos assumir que os "indicadores" nos microcircuitos não existem ou caem durante a inicialização devido a sobrecargas.

Uma mudança acentuada ocorreu em 2014, quando, devido a sanções, bons microchips importados de uso duplo se tornaram inesperadamente indisponíveis. Aqui, ao que parece, foi um ótimo momento para nos reunirmos e avançar para os desenvolvimentos domésticos, mas, em vez disso, a microeletrônica russa caiu novamente nos trilhos escorregadios da cópia ou, como dizem agora, da substituição de importações. No entanto, eu me empolguei demais com a letra, então vamos adicioná-la antes mesmo de examinar os padrões de design abaixo de 100 nm, analisar brevemente o estado das coisas nos microprocessadores e microcontroladores espaciais russos com base nos resultados de dez anos de desenvolvimento e cinco anos de substituição de importações.

O zoológico

Enquanto nos EUA existe um monopólio de fato do Poder, e na Europa - SPARC, na Rússia, todas as flores floresceram em todas as arquiteturas.

- ARM : três modelos de microcontroladores resistentes a radiantes baseados nos núcleos Cortex-M0 e Cortex-M4F são fabricados por Milander, mais um Cortex-M0 é a aliança Angstrem e Digital Solutions e mais três Cortex-M4F são NIIIS.

- MIPS : os núcleos RISCore32 “compatíveis com MIPS” controlam quatro processadores multi-placa heterogêneos resistentes a radiantes, desenvolvidos pela Elvis SPC; Os kernels KOMDIV "tipo MIPS" estão no desenvolvimento do "Progress" NIIISI, NIIIS e NIIMA.

- SPARC : o contratante principal para o desenvolvimento do russo LEON4 (1906MB016) - Voronezh NIIET. Curiosamente, o Centro de Moscou para Tecnologias SPARC (ICST) não tem nada a ver com isso. Aparentemente, a experiência de Voronezh no design de chips resistentes a radiantes acabou sendo mais importante.

- AMCS-96 : em geral, o MCS-96 é uma arquitetura de 16 bits, mas os sombrios gênios Voronezh da NIIET fizeram uma extensão de 32 bits e montaram um microcontrolador radiante.

- PowerPC (quase lá): existe um chip do “Módulo” do STC, que não possui resistência declarada, mas foi projetado para o “equipamento de bordo”. Aparentemente para aviônicos.

Além disso, existem vários microcontroladores de 8 e 16 bits, algumas opções de DSP / VLIW (seus próprios e de outros "análogos") e quase tudo: memória, BMC, FPGA, FPAA, ADC, DAC, microondas, dispositivos discretos. Existem alguns microcircuitos de aplicação espacial para quase todos os gostos - mas o fato é que não precisamos de alguns, mas competitivos, bem documentados e com bom suporte, e com o segundo e o terceiro pontos, os fabricantes russos tradicionalmente tinham tudo (e existem, que já está lá) ruim.

Figura 11. Outra observação sobre a questão da diversidade de microprocessadores domésticos: é assim que normalmente se parece um módulo de processador "substituído por importação". Acenamos a bandeira "temos um processador doméstico" e continuamos no modo normal. A mesma foto, em princípio, pode ser usada como uma ilustração da escala de quanto tudo precisa ser importado.

Digressão de dígitosOs padrões de projeto são uma excelente figura de marketing, que não tem muito a ver com o tamanho real dos transistores e é realmente importante para um número limitado de aplicativos, que incluem processamento de dados, armazenamento de grande capacidade e FPGA, onde muitos metais e transistores vão para a conexão de unidades de computação. Em todas as outras aplicações, os padrões de design não são tão críticos: os microcontroladores comerciais modernos são fabricados de acordo com os padrões de 180-90 nm e os microcircuitos de potência - 180-600 nm, ou mais. A escolha da tecnologia depende de muitos fatores, principalmente das tarefas que precisam ser abordadas. Isso também se aplica aos microcircuitos espaciais e, apesar de todos os volumes crescentes de processamento de informações a bordo, uma parte significativa dos microcircuitos a bordo é ocupada com coisas completamente diferentes - controle de atuadores, telemetria, conversão de energia, comunicações por rádio - e, portanto, não requer os padrões de design mais recentes.

Se você produz chips no exterior, agora, para produtos sobre os quais você não declara ser de uso duplo, não há riscos, nem restrições , e você pode executar qualquer coisa. Para produção na Rússia, agora estão disponíveis tecnologias com padrões de design de até 90 nm, mas os “cavalos de trabalho” para os chips resistentes a radiantes da maioria dos desenvolvedores russos são a tecnologia Mikron volumétrica de 180 nm e seu próprio processo SOI de 240 nm. As fábricas, no entanto, também estão cheias de problemas com as sanções devido a suprimentos e equipamentos importados, mas essa é uma história longa e triste em separado.

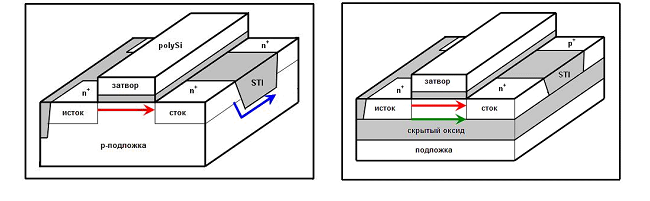

Figura 12. Comparação da ocorrência de correntes de vazamento em transistores volumétricos e SOI MOS. Os vazamentos são a principal causa de falhas paramétricas causadas por uma dose completa de radiação. A figura mostra claramente que o SOI não resolve todos os problemas com a resistência à radiação, mas a ausência fundamental de um efeito de tiristor devido ao isolamento completo de cada transistor facilita a vida dos desenvolvedores, para os quais muitos deles gostam muito de SOI.

Como é absolutamente impossível mencionar todos na Rússia sem resistência à radiação (e eles não fornecem informações sobre desenvolvimentos em todos os cantos), falarei brevemente de três empresas que lidam com microcircuitos espaciais não de tempos em tempos, mas sistemicamente e Obviamente, eles estão envolvidos em microprocessadores e microcontroladores. Essas empresas são Elvis, Milander e NIISI. Eu ficaria feliz em contar em detalhes sobre o desenvolvimento do NIIET, mas sobre os métodos de proteção contra radiação, foi difícil encontrar algo mais específico do que palavras gerais como “soluções estruturais e de circuitos especiais implementadas no microcontrolador que garantem sua operação estável no nível da dose acumulada não menos que 250 Crad e perda de energia linear (TZZ) até 60 MeV ∙ cm2 / mg ”. A exceção é o LEON, mas tudo é igual a qualquer outro LEON-FT - gatilhos triplos e codificação resistente a ruído na memória.

JSC SPC “Elvis”

A empresa Elvis desenvolve a plataforma Multicor desde o início dos anos 2000, que é uma combinação do núcleo de controle RISC e DSP em um chip. Eles começaram o trabalho sistêmico com a garantia da resistência à radiação quase ao mesmo tempo, juntamente com o Departamento de Eletrônica da MEPhI, primeiro usando tecnologias estrangeiras; após o surgimento da própria tecnologia de 180 nm da Micron, Elvis se tornou um dos primeiros clientes externos, desenvolvendo uma biblioteca radiante de portas lógicas e um conjunto de blocos de IP para criar sistemas em um chip. Nas descrições da maioria dos microcircuitos da

plataforma Multibort (a versão resistente à radiação do Multicore), a inscrição “o microcircuito é projetado e fabricado no território da Federação Russa”. Um conjunto de chips é projetado para construir redes de dados a bordo de acordo com os padrões SpaceWire e SpaceFibre e inclui processadores, DSP, memória, PLL e interruptores.

Desde o início, Elvis esteve envolvido ativamente na criação e desenvolvimento do padrão europeu de transferência de dados a bordo das naves espaciais SpaceWire (os americanos usam seu próprio padrão - RapidIO), participando de reuniões do grupo de trabalho internacional e sendo o principal impulsionador da implementação do padrão SpaceFiber ainda mais rápido.

Figura 13. Diagrama de blocos do processador 1892VM206. A frequência de operação do núcleo RISC é de 120 MHz, os núcleos DSP são de 140 MHz, quatro portas SpaceWire têm 300 Mbit / s cada, duas portas SpaceFibre têm 1,25 Gbit / se existem vários detalhes triviais.

A execução em nossa própria biblioteca resistente à alegria em todos os circuitos é declarada como a principal maneira de obter resistência à radiação. Os detalhes sobre algumas técnicas de arquitetura nas descrições no site oficial são poucos, e a busca por publicações não tornou a imagem mais clara, porque Elvis é publicado pouco e principalmente sobre outros tópicos. Para todos os processadores, a codificação Hamming de toda a memória é declarada e, em um dos chips, há uma reserva tripla do arquivo de registro e da árvore do relógio. Referindo-se à completude dessas informações com um ceticismo saudável, vamos supor que a defesa arquitetônica no Multiborts seja um pouco menos desenvolvida do que no LEON-FT.

JSC PKK “Milander”

Outro fabricante que lida muito com microcircuitos resistentes à chuva é Milander. A maioria de seus

chips resistentes à alegria é de alguma forma projetada para sistemas de telemetria de bordo - são chips de processamento de sinal de sensores, comutadores analógicos e digitais, ADCs, memória e, é claro, o assunto de nosso interesse são três microcontroladores. Mais precisamente, não três, mas duas e meia, porque o 1986BE8T e o 1986BE81T têm a bordo o núcleo do ARM Cortex-M4F, conjuntos periféricos idênticos e diferem apenas no tipo de memória do programa - ROM no primeiro caso e SRAM no segundo. Suponha que a variante SRAM seja realmente necessária para depurar a variante ROM. O 1923014 está equipado com um núcleo ARM Cortex-M0 mais modesto e faz parte do chipset para organizar um sistema de sensor multicanal, e esse chip não é um microcontrolador no sentido usual, mas um controlador especializado, afiado para uma aplicação específica.

Nas especificações para 1986BE8T e 1986BE81T (eles têm um comum), você pode encontrar uma descrição do “controlador para processar eventos de falha, falhas e erros”, incluindo, entre outras coisas, a funcionalidade de aparar falhas únicas, semelhante à descrita acima usando também o processador ERC32 uma descrição detalhada da operação da codificação de correção de erros (código de SECDED Hamming) em diferentes tipos de memória. Não consegui encontrar nenhuma informação aberta sobre, por exemplo, reserva tripla de gatilhos ou uma árvore de relógio, portanto, vamos supor que, do ponto de vista da tolerância a falhas de arquitetura, 1986 8 esteja entre ERC32 e LEON-FT.

Figura 14. BCD SOI de seção transversal com transistor LDMOS de alta tensão em um bolso isoladoA base tecnológica para a maioria dos chips Milander resistentes a radiantes são as bibliotecas e um conjunto IP proprietário da tecnologia de processo BCD SOI de 180 nm da fábrica alemã XFAB. Essa tecnologia, diferentemente da SOI convencional, possui uma espessa camada de instrumento de silício (da ordem de um mícron) e, na maioria dos casos, se comporta como uma tecnologia convencional a granel. A presença de óxido latente permite organizar o isolamento dielétrico dos elementos um do outro e, assim, garantir a ausência de um efeito tiristor, e o fato de ele estar em grande profundidade permite que você não se preocupe com vazamentos na interface do silício e de um dielétrico oculto, o que reduz a resistência à dose da tecnologia SOI convencional.

Figura 15. Comparação de dois elementos OR.

A figura mostra dois elementos lógicos idênticos (OR de duas entradas) das bibliotecas Milander feitas usando métodos diferentes de aumentar a resistência à radiação. À esquerda, você pode ver transistores de anel n-canal que neutralizam completamente o vazamento do transistor. No entanto, essa medida radical é muitas vezes excessiva, uma vez que os transistores lineares convencionais (às vezes com pequenas alterações) são suficientes para doses moderadas de radiação e, devido à sua aplicação, resistência suficiente pode ser alcançada com uma área menor e um consumo de energia - o que é claramente mostrado na figura.

Uma característica importante da tecnologia escolhida por Milander é a presença de transistores e outros elementos projetados para operação com altas tensões de até 200 V. A integração da lógica digital e dos dispositivos de energia em um único chip permite criar conversores CC / CC altamente eficientes, drivers principais, microcontroladores com drivers e muitas outras coisas em demanda. No momento, essas oportunidades não são usadas, mas quando elas começarem, Milander terá sérias vantagens competitivas em relação a outros desenvolvedores, porque não há análogos diretos dessa tecnologia na Rússia; ou 180 nm a uma tensão de 3,3 V ou altas tensões nos padrões de projeto de 1-3 mícrons. Os trabalhos sobre o tópico LDMOS de alta tensão (e até a alegria deles) foram publicados pelo NIIIS nos últimos dois anos, mas até agora são apenas publicações científicas e não se fala em produção em massa.

Na primavera, havia notícias de que os padrões de projeto de 500 nm "para microcircuitos de fontes de energia secundárias" eram dominados em Bryansk "Silicon-L", mas nenhum detalhe foi fornecido.Figura 16. Roteiro para o desenvolvimento de desenvolvimentos resistentes a radiantes de Milander usando a tecnologia BCD SOI 180 nm. E sim, você vê corretamente a palavra "FPGA" no canto inferior direito, eles já a possuem e funciona.Centro de Pesquisa Científica da Instituição Federal do Estado para Pesquisa de Sistemas da Academia Russa de Ciências

O NIISI explora sistematicamente a computação, incluindo microprocessadores radiantes para aplicações espaciais. A pesquisa sistemática, como convém a um instituto acadêmico, implica em KPI no número de publicações, portanto, monitorar o progresso do instituto é muito mais fácil do que para empresas comerciais. Estamos interessados na parte "espaço" da linha "COMDIV" (também há uma parte de "alto desempenho").A arquitetura do KOMDIV é uma revisão criativa do MIPS32, licenciada pela NIIIS no início dos anos 90. Inicialmente, o instituto trabalhou com fábricas estrangeiras e, após o surgimento de sua própria produção, começou a trabalhar em duas frentes, movendo a maior parte da linha resistente à alegria para casa. A fábrica da NIIIS está localizada em Moscou, no Instituto Kurchatov; Foi lançado em 2003 e é uma produção piloto de pequena escala localizada em clusters selados em uma área muito modesta. De fato, os esforços dos acadêmicos Betelin, Valiev e Velikhov perceberam o conceito Minimal Fab que está na moda hoje, que só funcionava normalmente quinze anos antes que os japoneses (e o primeiro foi inventado em Minsk por V.A. Labunov em 1983). Inicialmente, a fábrica trabalhou com padrões de projeto de 500 nm, depois os padrões de 350 e 250 nm foram dominados,bem como silício na tecnologia de isoladores, que se tornou a base da linha resistente a radiações NIIIS.Duas vantagens principais do processador 1890VM1T (tecnologia volumétrica de 500 nm, 50 MHz) - ele funciona e é doméstico. Mas os microcircuitos russos são tão severos que, para uma órbita baixa (principalmente para computadores de bordo das novas naves espaciais "digital" Soyuz-TMA e Progress-M), isso é suficiente, apesar da completa ausência de proteção especial contra radiação. Para operação normal, o 1890BM1T precisa de um chip complementar responsável por trabalhar com interfaces externas (semelhante à maneira como o ERC32 foi fabricado em três chips). Para condições mais graves, foram desenvolvidos análogos (séries 5890, 1900 e 1907) usando a tecnologia SOI para se livrar do efeito do tiristor. Ao mesmo tempo, nos chips da série 1907, o controlador de interface já está no mesmo chip que o próprio processador.Como eu disse um pouco acima, uma das vantagens de estudar os produtos NIISI é a abundância de publicações. Como exemplo, vamos dar dois artigos publicados no IEEE Transactions on Nuclear Science em 2011 e 2013. O primeiro é MS Gorbunov et al., "Análise da sensibilidade SEE do microprocessador SOI CMOS: correlação dos resultados obtidos por diferentes métodos de teste". Ele descreve um processador SOI de 500 nm com uma frequência de clock de 33 MHz. Das medidas arquiteturais declaradas para aumentar a tolerância a falhas, apenas paridade de cache, onde um erro causa a mesma interrupção que uma falta de cache. Além disso, foi aplicada uma topologia especial de transistores, que suprime o efeito bipolar do parasita e, portanto, aumenta o limiar de mau funcionamento (e, ao mesmo tempo, por razões não relacionadas, aumenta a resistência à dose total de radiação). Relativamente fácilmas se o objetivo principal é tolerância a falhas, é exatamente isso que você precisa. E então, quando o problema das falhas for resolvido, você poderá começar a pensar na tolerância a falhas.O segundo artigo é PN Osipenko et al., “Microprocessador SOI tolerante a falhas para aplicações espaciais”. Aqui já vemos 350 nm em vez de 500 e 50-66 MHz em vez de 33 (desempenho 8,9 MFLOPS a 50 MHz). Isso ainda não é de 150 MHz, como o RAD750 americano voando ao mesmo tempo no espaço, mas o progresso é evidente. Ainda mais interessante é a estrutura interna detalhada do chip. Todo o núcleo é triplicado - não disparadores, como no LEON-FT, mas toda lógica combinacional. Obviamente, isso aumenta a área e o consumo em três vezes (1,8 W a 66 MHz), mas ajuda a evitar falhas não apenas nos elementos de armazenamento, mas também nos combinados. Eles são muito menores do que na memória, porque precisam coincidir no tempo com a frente do sinal do relógio para afetar algo (e também há um efeito de mascaramento quando a falha não passa pela lógica, mas isso é particular),mas se você já começou a fazer tudo corretamente, precisará se livrar deles.

E agora finalmente abaixo dos 100

Figura 19. Várias falhas de memória usando o cristal de teste de 65 nm como exemplo.A figura mostra os resultados da obtenção de uma partícula carregada de um tipo diferente (quase todos os gases nobres foram observados) em uma matriz de memória criada usando a tecnologia de 65 nm. À esquerda, há memória comum, à direita, uma memória radiante especialmente projetada. Dez falhas de um hit! Não dois, não três - dez. Esse efeito é causado pelo fato de as dimensões dos elementos do microcircuito estarem diminuindo constantemente, mas o tamanho da região da qual a carga em excesso é coletada quando uma partícula carregada entra permanece o mesmo (cerca de 2-2,5 mícrons) - porque esse tamanho depende da difusão da carga sobre o cristal. E agora a tecnologia chegou ao ponto em que a célula de memória se tornou pequena o suficiente para que qualquer ocorrência cubra muitas células ao mesmo tempo. O fato de que isso é difusão é evidente a partir da forma específica das áreas afetadas - exatamente duas colunas, e não há propagação para a direita e esquerda.Separadamente, preste atenção à coluna da direita - essas são falhas dos prótons, que constituem a maior parte da radiação solar. Eles são a razão pela qual você não deve apenas usar chips comerciais modernos atrás dos cinturões de radiação da Terra (Ilon Mask, estou olhando para você e seu voo para Marte agora). No lado direito da figura - dados em uma memória semelhante, mas radostoykoy. Como você pode ver, uma parte significativa dos problemas com várias falhas (e ao mesmo tempo com todo o resto) foi resolvida - apenas a área dessa célula de memória é várias vezes maior que o normal. E eu nem vou começar sobre como montar uma célula DICE de 65 nm com todos os transistores espaçados no espaço, misturando simultaneamente duas ou quatro dessas células para economizar espaço e não ficar emaranhadas no macarrão de metalização de vários níveis resultante. No entanto, entre as publicações do NIIIS, existem também esses trabalhos.compondo a maior parte da radiação solar. Eles são a razão pela qual você não deve apenas usar chips comerciais modernos atrás dos cinturões de radiação da Terra (Ilon Mask, estou olhando para você e seu voo para Marte agora). No lado direito da figura - dados em uma memória semelhante, mas radostoykoy. Como você pode ver, uma parte significativa dos problemas com várias falhas (e ao mesmo tempo com todo o resto) foi resolvida - apenas a área dessa célula de memória é várias vezes maior que o normal. E nem vou começar sobre como montar uma célula DICE de 65 nm com todos os transistores espaçados no espaço, misturando simultaneamente duas ou quatro dessas células para economizar espaço e não se enredar no macarrão de metalização de vários níveis resultante. No entanto, entre as publicações do NIIIS, existem também esses trabalhos.compondo a maior parte da radiação solar. Eles são a razão pela qual você não deve apenas usar chips comerciais modernos para os cinturões de radiação da Terra (Ilon Mask, estou olhando para você e seu voo para Marte agora). No lado direito da figura - dados em uma memória semelhante, mas radostoykoy. Como você pode ver, uma parte significativa dos problemas com várias falhas (e ao mesmo tempo com todo o resto) é resolvida - apenas a área dessa célula de memória é várias vezes maior que o normal. E nem vou começar sobre como montar uma célula DICE de 65 nm com todos os transistores espaçados no espaço, misturando simultaneamente duas ou quatro dessas células para economizar espaço e não se enredar no macarrão de metalização de vários níveis resultante. No entanto, entre as publicações do NIIIS, existem também esses trabalhos.nas quais você não deve apenas usar chips comerciais modernos para os cinturões de radiação da Terra (Ilon Mask, estou olhando para você e seu voo para Marte agora). No lado direito da figura - dados em uma memória semelhante, mas radostoykoy. Como você pode ver, uma parte significativa dos problemas com várias falhas (e ao mesmo tempo com todo o resto) foi resolvida - apenas a área dessa célula de memória é várias vezes maior que o normal. E nem vou começar sobre como montar uma célula DICE de 65 nm com todos os transistores espaçados no espaço, misturando simultaneamente duas ou quatro dessas células para economizar espaço e não se enredar no macarrão de metalização de vários níveis resultante. No entanto, entre as publicações do NIIIS, existem também esses trabalhos.nas quais você não deve apenas usar chips comerciais modernos para os cinturões de radiação da Terra (Ilon Mask, estou olhando para você e seu voo para Marte agora). No lado direito da figura - dados em uma memória semelhante, mas radostoykoy. Como você pode ver, uma parte significativa dos problemas com várias falhas (e ao mesmo tempo com todo o resto) foi resolvida - apenas a área dessa célula de memória é várias vezes maior que o normal. E nem vou começar sobre como montar uma célula DICE de 65 nm com todos os transistores espaçados no espaço, misturando simultaneamente duas ou quatro dessas células para economizar espaço e não se enredar no macarrão de metalização de vários níveis resultante. No entanto, entre as publicações do NIIIS, existem também esses trabalhos.No lado direito da figura - dados em uma memória semelhante, mas radostoykoy. Como você pode ver, uma parte significativa dos problemas com várias falhas (e ao mesmo tempo com todo o resto) foi resolvida - apenas a área dessa célula de memória é várias vezes maior que o normal. E nem vou começar sobre como montar uma célula DICE de 65 nm com todos os transistores espaçados no espaço, misturando simultaneamente duas ou quatro dessas células para economizar espaço e não se enredar no macarrão de metalização de vários níveis resultante. No entanto, entre as publicações do NIIIS, existem também esses trabalhos.No lado direito da figura - dados em uma memória semelhante, mas radostoykoy. Como você pode ver, uma parte significativa dos problemas com várias falhas (e ao mesmo tempo com todo o resto) foi resolvida - apenas a área dessa célula de memória é várias vezes maior que o normal. E nem vou começar sobre como montar uma célula DICE de 65 nm com todos os transistores espaçados no espaço, misturando simultaneamente duas ou quatro dessas células para economizar espaço e não se enredar no macarrão de metalização de vários níveis resultante. No entanto, entre as publicações do NIIIS, existem também esses trabalhos.como montar uma célula DICE a 65 nm com todos os transistores espaçados no espaço, misturando simultaneamente duas ou quatro dessas células para economizar espaço e não se enredando nos macarrões de metalização de vários níveis resultantes. No entanto, entre as publicações do NIIIS, existem também esses trabalhos.como montar uma célula DICE de 65 nm com todos os transistores espaçados no espaço, misturando simultaneamente duas ou quatro dessas células para economizar espaço e não se enredar nos macarrões de metalização de vários níveis resultantes. No entanto, entre as publicações do NIIIS, existem também esses trabalhos.

Figura 21. Redundância modular tripla e redundância modular dupla com votação automática. No artigo de J.Teufel, “Circuitos de redundância dupla modulares com auto-voto para

Mitigação transitória de evento único ”, IEEE Transactions on Nuclear Science, 2008 (Sandia Labs ainda está conosco, ou melhor, ainda está com eles)

O diagrama da figura remonta a 2008 e mostra que nossos amigos juramentados também usam muitas coisas interessantes em produtos menos públicos do que o RAD750 (e o principal campo de atividade da Sandia Labs é o programa nuclear militar americano). Em particular, no artigo mencionado acima e em várias outras publicações recentes, a questão de como usar redundância modular tripla e dupla em conjunto em diferentes partes do chip é discutida em detalhes. A propósito, se o elemento de votação tiver um atraso suficientemente grande, no esquema de dupla redundância ele filtrará falhas únicas na lógica, e o resultado será tão estável quanto a redundância tripla.

Agora vamos ver como são os elementos da biblioteca na tecnologia de 65 nm. Cito novamente o trabalho da NIISI - Yu.B. Rogatkin et al., “Desenvolvimento de uma biblioteca de elementos resistentes à radiação usando a tecnologia CMOS de 65 nm”, Proceedings of the NIISI RAS, 2018. Como a preocupação com a tolerância a falhas é quase completamente transferida para outros níveis de desenvolvimento - arquitetura e síntese automática de topologia, levando em consideração as restrições na localização dos elementos - as principais tarefas dos desenvolvedores das bibliotecas de elementos tornaram-se novamente a proteção contra a dose total absorvida e o efeito tiristor.

Figura 22. Células lógicas produzidas usando a tecnologia de 65 nm.

O elemento mais à esquerda na figura é um inversor de biblioteca comum.

O segundo elemento é sua versão radiante, equipada com anéis de proteção que evitam o efeito do tiristor. É importante que o anel tenha contatos com o metal apenas de um lado, e devemos ter em mente a resistência da camada de silício, que pode ser grande o suficiente para afetar a eficácia desta solução.

O terceiro é o mesmo inversor, no qual os lados do anel de proteção são cortados para economizar espaço.

O quarto é o mesmo, mas com contatos na parte externa dos anéis de proteção, a fim de controlar bem sua resistência e não se preocupar com a forma como são montados em blocos.

Quinto - um bloco de dois inversores e um elemento 2INE com as partes de fechamento dos anéis de proteção mostradas.

Quanto à dose total de radiação, aqui nos padrões abaixo de 100 nm, tudo é ainda mais simples e compreensível do que nas tecnologias mais antigas. As correntes de vazamento nelas já estão sem radiação, tudo é colocado sobre elas e, portanto, resta apenas introduzir uma correção adicional pelo fato de que elas crescerão ainda mais. As tecnologias típicas desse nível geralmente oferecem três opções para transistores - com baixa tensão limiar (rápida, mas com grandes vazamentos), com média tensão limiar e com alta tensão limiar (lenta, mas com pequenos vazamentos), e o usuário pode combiná-las se necessário. As bibliotecas padrão também são feitas em três versões e, ao projetar uma resistente a radiantes, é necessário fazer um compromisso entre velocidade e vazamentos, considerando que os transistores são conectados em série ou em paralelo.

Figura 23. Esquemas dos elementos lógicos 2I-NOT e 2OR-NOT.

No elemento 2, OU NÃO, os transistores de canal n são conectados em paralelo, o que duplica o vazamento, o que significa que faz sentido usar transistores com uma tensão limite mais alta neste local. E em 2I-NOT eles estão conectados em série, e aí você pode deixar o limiar usual de transistores. E esse raciocínio (de preferência suportado por dados de medição) precisa ser aplicado a todas as centenas de elementos da biblioteca e depois pensar no que fazer com os elementos de armazenamento para que eles fiquem menos confusos e vaze pelas chaves analógicas comumente usadas nos acionadores modernos, eles não quebraram tudo, e assim por diante.

Atualmente, o NIIIS possui uma plataforma completa para desenvolvimento com padrões de projeto de 65 nm, incluindo bibliotecas, blocos IP, compiladores de memória, interfaces de alta velocidade, etc. Também é importante que essa plataforma seja licenciada para outras empresas russas, o que ajuda a acelerar a superação da lacuna com os americanos e praticamente alcança os europeus. Se a fábrica não fosse a TSMC, mas a sua, como na América e na Europa ... Mas essa é outra história que se desenrola diante de nossos olhos. Depois de 2014, a tecnologia de processo da Micron da Mikron congelou no status de “aprovação na qualificação e domínio da produção” após 2014, e não há notícias sobre isso há algum tempo; mas nos últimos meses houve notícias suficientes sobre planos de longo prazo para criar produção na Rússia com padrões de 28 nm. Quando esses planos serão implementados e se serão, é uma grande questão.

Resumindo esta parte, observamos como, com uma diminuição nos padrões de design, as tarefas enfrentadas pelos desenvolvedores mudaram novamente. As tecnologias profundamente submicrônicas são resistentes a uma dose total de radiação, suficiente para a maioria das aplicações, e permitem organizar a proteção contra o efeito tiristor e falhas únicas / múltiplas no estágio de desenvolvimento do chip, sem modificar a tecnologia de processo original. Isso ajuda a reduzir o custo de produção e acelerar o desenvolvimento de novas tecnologias. Os principais obstáculos ao progresso são econômicos: o desenvolvimento e o estudo abrangente dos chips de teste e de "combate" estão se tornando mais caros a cada nova geração de tecnologia, e as escassas circulações dos chips espaciais não nos permitem compensar adequadamente esses custos. Portanto, os desenvolvedores procuram maximizar os recursos de cada tecnologia usada e usá-la o máximo possível, seguindo em frente somente quando for absolutamente necessário e criando plataformas de desenvolvimento e permitindo que você crie uma ampla variedade de microcircuitos. Os desenvolvedores russos hoje estão um pouco atrás dos colegas ocidentais, e as razões para esse atraso não são científicas ou de engenharia, mas organizacionais e econômicas.

Forçosamente uma breve análise de todos os outros

Japão

A agência espacial japonesa JAXA está moderadamente envolvida em atividades internacionais, e a maior parte de sua pesquisa espacial é realizada pelos japoneses por conta própria. As missões impressionam com ambição e histórias impressionantes sobre a superação bem-sucedida das dificuldades que surgem em órbita. Se Matt Damon pudesse interpretar uma sonda espacial, já veríamos filmes sobre Hayabusa nas bilheterias (a propósito, os japoneses já filmaram três peças) e sobre a Akatsuki. Microprocessadores para o espaço, como todo o resto, os japoneses têm suas próprias arquiteturas, e mesmo seus padrões de design de produção não são os mesmos do resto do mundo (300 e 200 nm, por exemplo). Eu ficaria muito satisfeito em escrever sobre isso em detalhes, mas há pouca informação e quase não existe em não-japonês, então terei que me limitar a uma breve visão geral.

Figura 24. Uma fonte típica de informação sobre processadores japoneses resistentes a radiações.

Os principais fornecedores de instrumentos da JAXA são Hitachi, NEC e MHI (Mitsubishi Heavy Industries). Nos anos 80, a indústria japonesa era apaixonada pelo projeto TRON, que oferecia um design de infraestrutura de rede de ponta a ponta. Os japoneses usam o sistema operacional TRON em tempo real na indústria e no espaço até agora, mas a arquitetura dos microprocessadores TRON foi rapidamente abandonada (apesar de chips resistentes a radiações terem sido feitos nele e, provavelmente, eles voaram) em favor do MIPS64 (no caso da NEC) e outro Arquitetura japonesa SuperH de 32 bits (H é Hitachi; sua versão SH2 pode ser encontrada em carros japoneses e SH4 nos produtos automotivos Sega Dreamcast e Hitachi e Renesas).

Figura 25. Microprocessadores espaciais japoneses. HR5000 - MIPS64, SOI-SOC - SH4.

Figura 26. Ilustração dos aplicativos SOI-SOC2.

"SOI" no SOI-SOC, é claro, significa "silício no isolador". O nível tecnológico do SOI-SOC3 é de 200 nm, a próxima geração em desenvolvimento terá menos. Também uma citação pequena, mas importante, da JAXA: “Há um grande problema de erros leves nos processadores de consumo / industriais devido aos nêutrons atmosféricos no nível do solo. A MPI SOI-SOC será entregue como peças de alta confiabilidade aos usuários desses processadores ". O problema dos nêutrons atmosféricos está relacionado principalmente à aviação, mas isso é outra história. Isso é tudo com os japoneses, vá para os vizinhos.

China

O programa espacial chinês é o que mais cresce e é uma das informações mais fechadas sobre processadores japoneses em comparação com os chineses apenas no mar. É difícil dizer algo concreto, exceto que os chineses começaram com a cópia camada por camada de tudo em sequência, e que em 2014 eles tinham muitas posições para a Rússia que sofreram sanções. Recentemente, no entanto, muito dinheiro foi investido na astronáutica chinesa e na microeletrônica chinesa, e os dispositivos mais recentes voam em processadores compatíveis com MIPS desenvolvidos pela Academia Chinesa de Ciências (não se parece com nada?) Loongson. Os civis de Loongson constroem PCs, tablets e até um supercomputador; esse processo acelerou significativamente após o início da guerra comercial entre os Estados Unidos e a China.

Israel

A Agência Espacial de Israel foi fundada em 1981, o primeiro satélite próprio foi lançado de Israel em 1988. Agora Israel está desenvolvendo e lançando (independentemente e de espaçoporto estrangeiro) várias famílias de veículos civis e científicos civis. Não consegui encontrar informações sobre o enchimento, mas me atrevo a sugerir que pelo menos os primeiros veículos de reconhecimento desenvolvidos por um dos principais contratados de aviação israelense voaram nos chips da arquitetura 1750A. Na engenharia civil moderna, as empresas israelenses colaboram muito com seus colegas europeus, por isso é lógico assumir o uso de LEONs. Confirmação disso é que o satélite privado Bereshit voou no ano passado no GR712, uma versão do LEON desenvolvida e fabricada em Israel.

Índia

Na Índia, não há produção de microcircuitos, apenas uma fábrica experimental da Academia de Ciências local (isso não lembra nada?) Com os padrões de 180 nm. Os índios realizam algumas pesquisas sobre a alegria, mas nada importante é ouvido deles. De acordo com informações fragmentárias de várias fontes, eles usaram / estão usando as opções de processador ERC32 e LEON para seus satélites, e a magnífica missão marciana "Mangalyan" foi completamente controlada pelos processadores de arquitetura Mil-Std-1750A (novamente europeus).

Brasil

A microeletrônica brasileira é quase como um programa espacial brasileiro: você não sabe nada, mas existe. Em particular, os brasileiros são fortes especialistas na correção de falhas únicas em hardware comum usando métodos de software (por exemplo, executando parte dos comandos várias vezes e verificando os resultados) e na tolerância a falhas do FPGA. Grupos universitários especializados participam ativamente de conferências científicas internacionais e fazem projetos conjuntos com colegas europeus e americanos.

Isso parece ser tudo. O resto dos países não desenvolve microprocessadores ou sistemas espaciais baseados neles, adquirindo componentes, blocos ou satélites importantes montados ao lado, como o Paquistão, que está desenvolvendo sua própria indústria de satélites em estreita cooperação com os chineses. Bem, está claro que o preenchimento de dispositivos iranianos e norte-coreanos é conhecido apenas por seus criadores e, se tiver sorte, por alguns serviços de inteligência. Não somos inteligência, então vamos para a próxima parte.

O futuro próximo - um exemplo de todos juntos

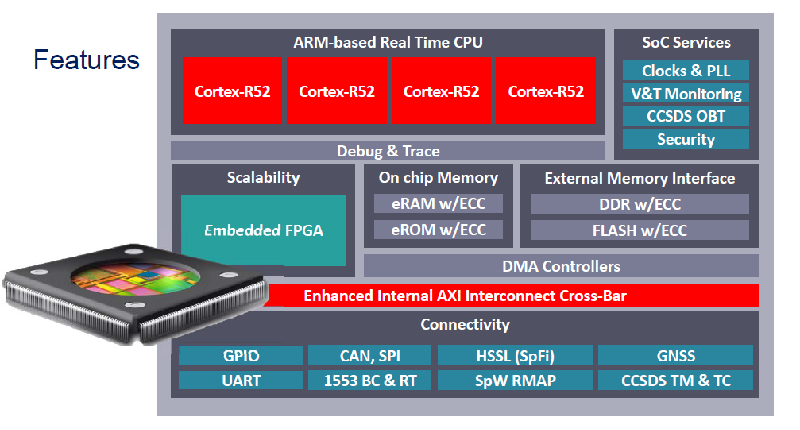

O nível tecnológico dos mais recentes microprocessadores espaciais é de 45 nm para os EUA (RAD5500), 65 nm para a Europa (GR740) e 65 nm para a Rússia (eles prometem lançar algo já este ano). Além disso, nos dois primeiros casos, podemos observar uma mudança geracional - nos EUA, a próxima geração de processadores espaciais (HPSC) será feita não pelo atual monopolista da BAE Systems na arquitetura PowerPC, mas pela Boeing no ARM (de acordo com os padrões de projeto de 32 nm na tecnologia SOI), mas na Europa Paralelamente ao lançamento do próximo SPARC LEON, está sendo desenvolvido um processador multi-core DAHLIA com uma arquitetura ARM com padrões de design de 28 nm (também SOI). Paralelamente, a Agência Espacial Européia, em seu desejo habitual de não depender de licenças de outras pessoas, começou a desenvolver a nova arquitetura RISC-V, que está rapidamente ganhando impulso no setor comercial e crescendo em um ecossistema de software. Os primeiros protótipos de chips RISC-V modificados por TMR já foram demonstrados em 2018 pela colaboração Antmicro e Thales. Apesar da popularidade do LEON (como se costuma dizer, em círculos estreitos), em relação à SPARC há muito que se questiona sobre o suporte a software, e os concorrentes têm pressa em tirar vantagem disso. Os concorrentes estão especialmente com pressa com o ARM, porque o acesso praticamente gratuito a uma enorme quantidade de software de aplicativos industriais e comerciais é um trunfo muito importante nas conversas com os desenvolvedores de naves espaciais, cuja importância está crescendo rapidamente em comparação com o desejo de ter compatibilidade retroativa com projetos antigos.

Além dos microprocessadores e DSP, onde a velocidade é uma prioridade óbvia, há uma demanda por microcontroladores. Existem chips na maioria das arquiteturas sonoras - European GR716 (SPARC / LEON), American RAD EMC (PowerPC), ARM de diferentes fabricantes (Vorago, Microchip, Milander, Angstrom), versões à prova de chuva do MSP430 da Texas Instruments, MCS- 96 e MCS-51 da NIIET e assim por diante. Os microcontroladores geralmente são mais simples de proteger do que seus "grandes" colegas, com ênfase na ausência de falhas (efeito tiristor) e com correção mínima dos núcleos adquiridos (ou sem correção e síntese usando gatilhos troyed e bibliotecas de elementos especiais). Voltando aos processadores, vamos ver quais plataformas de desenvolvimento abaixo de 100 nm existem ou são anunciadas agora.

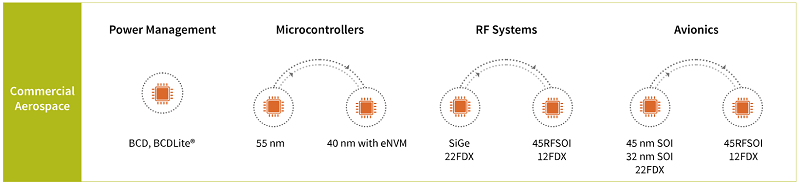

Figura 27. Plataforma de desenvolvimento abaixo de 100 nm para circuitos integrados resistentes a radiantes.

65 nm para os desenvolvedores da Europa e da Rússia já é "hoje", e os americanos geralmente saltaram de 150 imediatamente para 45 nm. Muito provavelmente, nos próximos dez anos, essas tecnologias serão as principais e os padrões mais sutis já mostrados neste diagrama passarão dos estágios iniciais para os estágios finais de desenvolvimento. No entanto, o que é mostrado na figura são apenas grandes colaborações públicas; de fato, nada (exceto tempo e dinheiro) não interfere no desenvolvimento de chips resistentes a radiações em outros processos técnicos sem muito ruído. Por exemplo, a GlobalFoundries oferece para criar chips aeroespaciais uma linha completa de tecnologias para diferentes gostos e orçamentos. É em suas instalações que os RAD5545s mais recentes são produzidos, e o HPSC também será produzido neles; isso não é surpreendente, porque as fábricas da GloFo são certificadas pela Trusted Foundry desde o momento em que pertenciam à IBM. E é improvável que todos os processos declarados estejam sem clientes americanos.

Figura 28. Ofertas da GlobalFoundries para o setor aeroespacial.

Na GlobalFoundries, embora não seja americana, mas alemã (em Dresden), eles planejam produzir seus futuros chips IMEC resistentes a radiantes (o que significa que toda a Europa menos STM) e Milander.

Figura 29. O roteiro de Milandra para o desenvolvimento de chips resistentes a radiantes com base na tecnologia 22 nm. Como você pode ver, existem muitos planos, incluindo FPGAs grandes e ADCs rápidos para SDR (Software Defined Radio). O primeiro chip de teste já foi produzido, por isso esperamos boas notícias.

O que é o FDSOI? O DF está totalmente esgotado, completamente esgotado; a fina camada de silício ativo entre o óxido de porta e o óxido latente está completamente esgotada e todo o canal do transistor a ocupa. Isso permite que você elimine completamente a capacitância perdida do dreno e da fonte, além de remover a distância de fluência ao longo da profundidade do silício, o que é típico para tecnologias a granel semelhantes, e reduz o consumo de energia estática. Além disso, em vez de usar vários tipos de transistores, como na tecnologia volumétrica, o FDSOI pode fornecer localmente tensão negativa ou positiva a um óxido oculto, alterando assim o limiar do transistor (e com ele a velocidade e o consumo de energia) - dependendo se o chip está em uso. ativo ou no modo de suspensão. Juntos, isso torna o FDSOI extremamente atraente, por exemplo, para a Internet das coisas. Ou para circuitos espaciais de baixa potência, o benefício da tecnologia SOI alivia automaticamente o desenvolvedor de uma dor de cabeça com falhas catastróficas devido ao efeito do tiristor.

Figura 30. Vista em corte transversal dos transistores surround e FDSOI.

A principal desvantagem do FDSOI em termos de resistência à radiação é o caminho de vazamento adicional ao longo dos limites do canal e do óxido latente. A carga acumulada no óxido oculto desempenha o papel de uma tensão positiva aplicada ao óxido oculto e, em vez de controlar o comportamento dos transistores através do portão inferior, o efeito da radiação deve ser compensado. E para fazer isso, uma grande tensão negativa deve ser aplicada - o que aumentará o processo de acúmulo de carga no óxido latente e piorará a resistência à dose. Em geral, é obtido um círculo vicioso, cuja saída pode não ser trivial. É verdade que muitas pessoas querem procurá-lo, para que você possa estocar pipoca. A primeira pipoca será útil em breve - o projeto europeu DAHLIA está quase completo.

Figura 31. Diagrama de blocos do DAHLIA. FDSOI de 28 nm, quatro núcleos ARM-Cortex R52 (promessa 4000 DMIPS a 600 MHz), aprimorados para aplicativos em tempo real com separação avançada de poderes, memória integrada, interfaces mais populares e até um FPGA integrado para 500 mil LUT, para que um chip seja preciso cobrir as necessidades de todos os usuários por muitos anos.

Enquanto isso, a tecnologia volumétrica não vai desistir.

Ele pode oferecer aos desenvolvedores a ausência de um caminho de vazamento "extra" e, a longo prazo, padrões de design mais baixos. Além disso, nos transistores FinFET, o portão começa a cobrir o canal cada vez mais densamente, e o óxido isolante se afasta do forte campo elétrico, o que também deve afetar positivamente a resistência à dose total de radiação. O IMEC já está começando a desenvolver bibliotecas de 16nm resistentes a radiantes, e a indústria comercial continua adotando novas tecnologias.Figura 32. Diferentes gerações de transistores MOS.A longo prazo, o GAA da Samsung (Gate All Around) promete ser resistente a uma dose total de radiação, liberando completamente os desenvolvedores de problemas com ela - eles simplesmente não têm nenhum caminho lateral da fonte para drenar, além do canal principal e do obturador principal e um isolador de portão tão sutil que a mudança na tensão limiar será insignificante mesmo em doses muito grandes. Mas, é claro, certamente haverá novas dificuldades - não apenas com falhas únicas, mas também, por exemplo, com efeitos de polarização, que já são uma preocupação total para os projetistas de transistores de nitreto de gálio HEMT. Em dispositivos feitos de semicondutores complexos, os efeitos quânticos e em nanoescala não são novos e, em breve, os desenvolvedores de silício precisarão de conhecimento sobre eles,Assim, nos próximos anos, trabalhar para garantir a resistência à radiação dos microchips para o espaço será suficiente. Mas também existem coletores de hádrons, energia atômica e termonuclear; o progresso é implacável e ele não vai parar - mas eu vou parar com essa nota positiva. Obrigado por ler até o fim, espero que tenha sido interessante.