MEPhI MIPSfpga研讨会的照片,材料和曲折

10月底,在MEPhI举行了关于MIPSfpga的研讨会-俄罗斯大学与Imagination Technologies,Microchip Technology,Gamma St.Petersburg,Macro Group,Xilinx的代表合作组织的一系列研讨会之一,来自MathWorks和NIISI的发言人参加了研讨会。下面是照片,材料链接,有关研讨会准备和神话文化的注释的混合。

下面是外面的MEPhI图片。 “核”这个词提醒我们,莫斯科工程物理研究所里有一个核反应堆,所以很难到达那里,尤其是持美国护照的时候-我获得了两周的通行证,校长签署了研讨会的订单。在入口处,有一名卡拉什尼科夫机枪手(!) (我没有为机

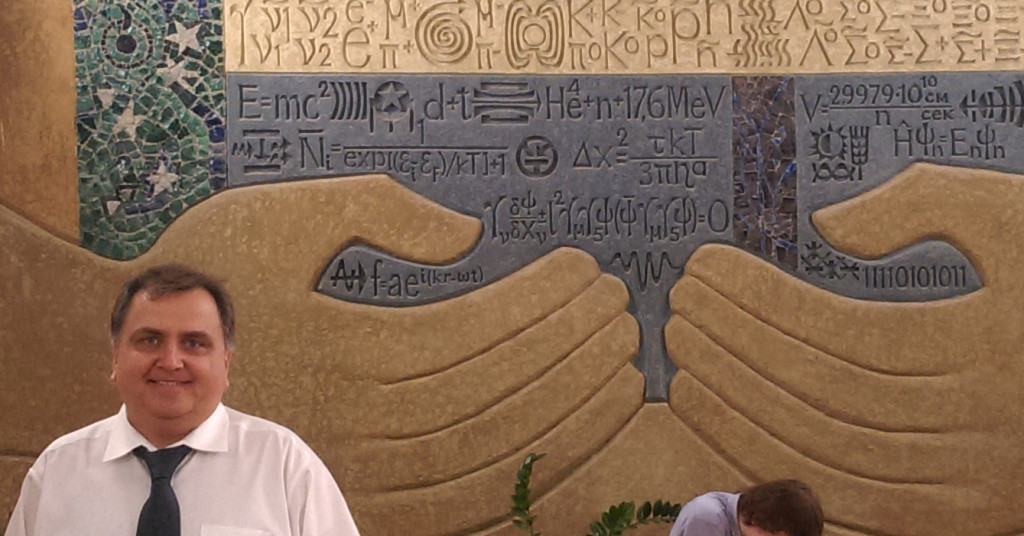

枪手拍照)在这里,我(与研讨会的其他组织者一起)(Yuri Panchul)-Igor Ivanovich Shagurin和Maxim Gorbunov:

Igor Ivanovich Shagurin,代理。该负责人微系研院 -对微处理器的英特尔,摩托罗拉和PowerPC,书籍和文章的作者在MIPS实验室工作。

UPD:NIIIS同志的澄清:

(我没有为机

枪手拍照)在这里,我(与研讨会的其他组织者一起)(Yuri Panchul)-Igor Ivanovich Shagurin和Maxim Gorbunov:

Igor Ivanovich Shagurin,代理。该负责人微系研院 -对微处理器的英特尔,摩托罗拉和PowerPC,书籍和文章的作者在MIPS实验室工作。

UPD:NIIIS同志的澄清:

«, -32 -64 MIPS- — ( :) ). , — MIPS- . RISC , . MIPS-I. , , MIPS- , . , „ MIPS“ MIPS- . „

有趣的是,伊戈尔·伊万诺维奇·沙古林(Igor Ivanovich Shagurin)代表苏联电子业参加了1970年代在旧金山召开的一次会议,当时苏联是一个相当孤立的国家。 1970年代VLSI会议的参与者被带到地球上红杉最高的地区Muir Woods,NIIIS / SRISA的研究员Maxim Gorbunov,该研究所还参与了具有MIPS架构的俄罗斯微处理器的开发-COMDIV-32和委员会64。

Maxim专长于设计抗辐射VLSI的拓扑结构,并且是在莫斯科举行的国际RADECS会议之一的联席主席:

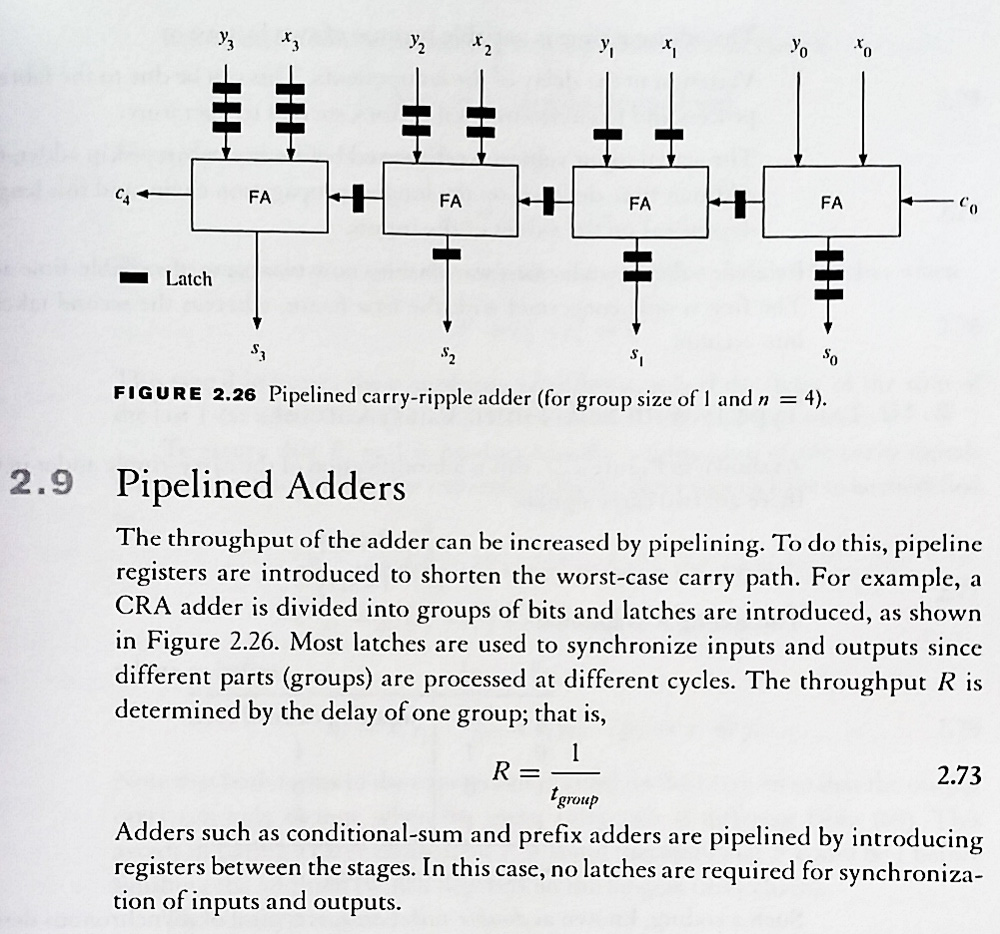

在MEPhI举行的MIPSfpga研讨会之前,一位讲师Yegor Kuzmin开始向我询问有关一项学生项目的特定专业计算方案中的竞赛条件。我不确定自己是否理解正确,但表示在组织合理的同步设计中不会出现此类问题,并承诺将“数字算术”一书的一页图片作为示例发送给您。,它了解流水线加法器的结构,其中包含少量组合逻辑(与带顺序进位的加法器相同),但同时放置寄存器(D触发器)的方式使得加法器可以在每个时钟周期以一个频率开始一个新的加法运算时钟信号,由一个位的完整组合加法器的延迟确定:Milos D. Ercegovac和TomásLang的Digital Arithmetic 1st Edition 同时,我拍摄了几页有关自时异步电路的页面,这也与此问题有关。

在MEPhI举行的MIPSfpga研讨会之前,一位讲师Yegor Kuzmin开始向我询问有关一项学生项目的特定专业计算方案中的竞赛条件。我不确定自己是否理解正确,但表示在组织合理的同步设计中不会出现此类问题,并承诺将“数字算术”一书的一页图片作为示例发送给您。,它了解流水线加法器的结构,其中包含少量组合逻辑(与带顺序进位的加法器相同),但同时放置寄存器(D触发器)的方式使得加法器可以在每个时钟周期以一个频率开始一个新的加法运算时钟信号,由一个位的完整组合加法器的延迟确定:Milos D. Ercegovac和TomásLang的Digital Arithmetic 1st Edition 同时,我拍摄了几页有关自时异步电路的页面,这也与此问题有关。 然后向我介绍了弗拉基米尔·德门蒂耶夫(Vladimir Dementiev),他与Andrei Andrianov,德米特里·科兹洛夫斯基(Dmitry Kozlovsky)在MEPhI进行了实验室课程,以对Microchip PIC32MX微控制器进行编程。我告诉弗教授亚历克斯·迪恩的的北卡罗莱纳大学合作与想象,微芯片和Digilent公司,目前正在开发的编程Microchip的PIC32MZ微控制器新课程本课程包括RTOS和微控制器到云的新型连接。 PIC32MZ微控制器基于MIPS microAptiv UP微处理器内核,与MIPSfpga中使用的内核相同。因此,我开始激起MEPhI同志参加该课程的评估和(如果他们愿意)beta测试:

但是回到我们的研讨会。研讨会的主题是MIPSfpga。这是什么:

然后向我介绍了弗拉基米尔·德门蒂耶夫(Vladimir Dementiev),他与Andrei Andrianov,德米特里·科兹洛夫斯基(Dmitry Kozlovsky)在MEPhI进行了实验室课程,以对Microchip PIC32MX微控制器进行编程。我告诉弗教授亚历克斯·迪恩的的北卡罗莱纳大学合作与想象,微芯片和Digilent公司,目前正在开发的编程Microchip的PIC32MZ微控制器新课程本课程包括RTOS和微控制器到云的新型连接。 PIC32MZ微控制器基于MIPS microAptiv UP微处理器内核,与MIPSfpga中使用的内核相同。因此,我开始激起MEPhI同志参加该课程的评估和(如果他们愿意)beta测试:

但是回到我们的研讨会。研讨会的主题是MIPSfpga。这是什么:

MIPSfpga — MIPS microAptiv UP. Microchip PIC32MZ, « » — Samsung Artik 1.

MIPS microAptiv UP 25 , Verilog, , .

MIPS microAptiv UP — MIPSfpga — : (), () Field Programmable Gate Array (FPGA).

因此,我首先谈到并谈论:1. Imagination Technologies及其MIPS业务部门2. Imagination Technologies的教育计划3.为没有Verilog / VHDL的受众刷新RTL到GDSII流程的概念专门化:IP块和片上系统(SoC)的设计方式。4.我简要介绍了三行MIPS微处理器内核,并详细介绍了微控制器类内核,其中一个是基于MIPS microAptiv UP创建的MIPSfpga5 软件包,由于其中一个练习还包括演示缓存,我说了两句。单词以及有关MIPS microAptiv UP中的缓存的信息

在我的第一篇演讲之后,MathWorks的发言人Mikhail Peselnik进行了演讲:

Mikhail Peselnik 在Simulink上实现了MIPS的一部分,并获得了编辑奖,这是MATLAB本周精选:

Michael的例子表明,对于学生而言,处理器内核的体系结构和微体系结构可以通过不同的方式进行研究-至少在Verilog和VHDL上,至少在C模型的帮助下,至少在Simulink的帮助下。

但是,在学习了架构和微架构的基础知识之后,学生应该尝试使用工业处理器,并且在这里MIPSfpga进入了现场,其中:

在我的第一篇演讲之后,MathWorks的发言人Mikhail Peselnik进行了演讲:

Mikhail Peselnik 在Simulink上实现了MIPS的一部分,并获得了编辑奖,这是MATLAB本周精选:

Michael的例子表明,对于学生而言,处理器内核的体系结构和微体系结构可以通过不同的方式进行研究-至少在Verilog和VHDL上,至少在C模型的帮助下,至少在Simulink的帮助下。

但是,在学习了架构和微架构的基础知识之后,学生应该尝试使用工业处理器,并且在这里MIPSfpga进入了现场,其中:

- 学生可以在芯片上构建自己的系统原型,将他们设计的微处理器核心,存储器和I / O设备结合在一起

- , . « ».

- , , .

但是,为了试验SoC开发和内核,他们需要对工具/实现工具有很好的掌握。因此,在赛灵思在俄罗斯的正式代表,来自Macro Group的应用工程师Mikhail Mikhail Filippov之后发表了讲话。Xilinx是曾经发明FPGA的公司,至今仍是最高速FPGA的第一名。亚历山大·菲利波夫(Alexander Filippov)发表了两项报告:- 新型7系列FPGA和MPSoC UltraScale-适用于强大可编程芯片系统的XILINX产品

- XILINX VIVADO设计环境,用于在芯片上创建系统

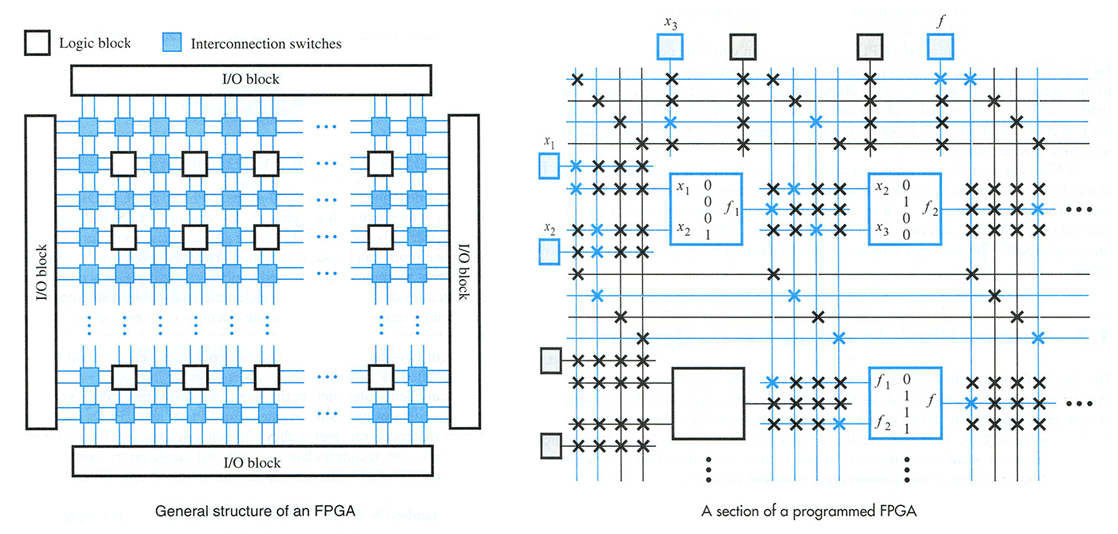

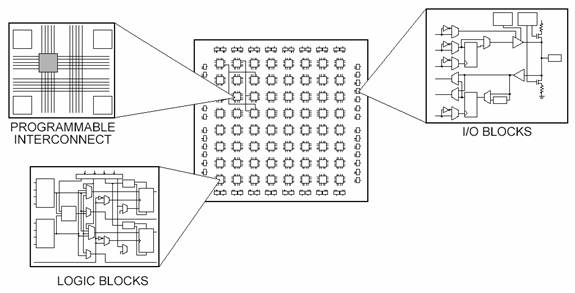

我在Habr的另一篇文章中用手指解释了什么FPGA / FPGA- 如何开始使用FPGA进行铁开发-逐步说明。但是,让我们再次重复此信息:在最简单的版本中,FPGA由同质单元矩阵组成,可以使用连接到配置存储器位的多路复用器将每个单元更改为功能。一个单元可以成为具有四个输入和一个输出,另一个-一位寄存器等的AND门。我们将一系列位从存储器中加载到配置存储器中-给定的电子电路在FPGA中形成,FPGA可以是处理器,显示控制器等。FPGA / FPGA不是处理器;通过对FPGA进行“编程”(填充FPGA的配置存储器),您可以创建电路(硬件),而在对处理器(固定硬件)进行编程时,您可以滑入一串顺序的程序指令(软件)。下面是最简单的FPGA单元的示意图,其中包括一个查找表(LUT)和触发器。没错,在此方案中,未显示更改单元功能以及与配置存储器的连接的多路复用器。

我在Habr的另一篇文章中用手指解释了什么FPGA / FPGA- 如何开始使用FPGA进行铁开发-逐步说明。但是,让我们再次重复此信息:在最简单的版本中,FPGA由同质单元矩阵组成,可以使用连接到配置存储器位的多路复用器将每个单元更改为功能。一个单元可以成为具有四个输入和一个输出,另一个-一位寄存器等的AND门。我们将一系列位从存储器中加载到配置存储器中-给定的电子电路在FPGA中形成,FPGA可以是处理器,显示控制器等。FPGA / FPGA不是处理器;通过对FPGA进行“编程”(填充FPGA的配置存储器),您可以创建电路(硬件),而在对处理器(固定硬件)进行编程时,您可以滑入一串顺序的程序指令(软件)。下面是最简单的FPGA单元的示意图,其中包括一个查找表(LUT)和触发器。没错,在此方案中,未显示更改单元功能以及与配置存储器的连接的多路复用器。 图示FPGA结构的图:

图示FPGA结构的图: 还有一个:

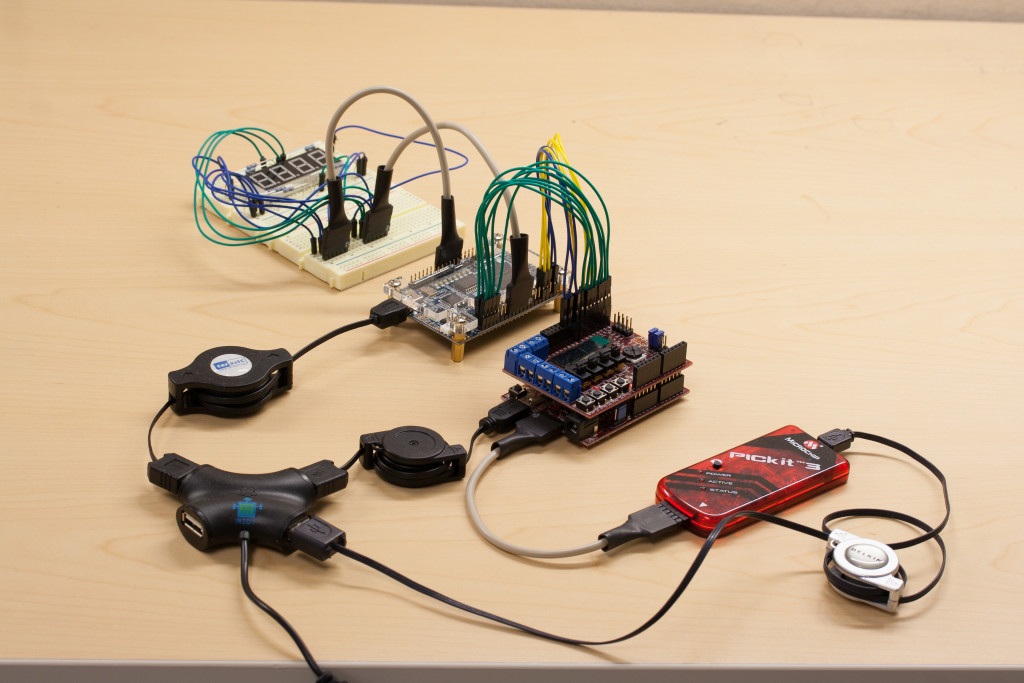

还有一个: 在莫斯科工程物理研究所的饭厅吃完午餐后,我们开始了实际部分。最初,当Imagination Technologies和Xilinx在洛杉矶举行这样的研讨会时,他们使用了来自加利福尼亚南部的David和Sarah Harris教授准备的幻灯片。最初看起来,您可以在视频中看到:洛杉矶研讨会的所有8个视频在俄罗斯的研讨会上,必须对Harris的核心和实验室绑定进行大量修改。可以在https://github.com/MIPSfpga/mipsfpga-plus上找到修改内容。区别包括:1.所有东西都是从Altera便宜的主板上分类的,可以在俄罗斯使用,没有进出口引擎2.仅通过UART即可将程序加载到合成系统中,而无需使用BusBlaster。3.将光传感器用作外设,而不是LCD显示器4.可切换超低频时钟信号,允许实验室可视化任何处理器内部的操作5.添加了一个简单的实验室可视化高速缓存未命中+每件事物和化妆品-更紧凑的Bootloader / Bootloader,将不可缓存的交易范围缩小到内存的可能性等。更多详细信息:1.在Altera下移植首先,Harris幻灯片显示了Xilinx的所有内容,最近,从Xilinx FPGA到俄罗斯的运输板已经变成相当复杂的官僚程序,需要3-4个月的时间。即使有免费许可证,用于合成软件的许可证和Xilinx Vivado布局布线也发生了同样的事情。一些俄罗斯大学没有Xilinx董事会或Vivado许可证。其他人仅拥有Vivado的前身的旧许可证-2013 ISE软件,该软件不支持我在俄罗斯运输的板上的FPGA。简而言之,在俄罗斯举办的研讨会上,我和同志在加利福尼亚州将MIPSfpga移植到了Xilinx竞争对手Altera(该公司正在与Intel合并)的俄罗斯廉价主板上。 Zelenograd公司SPC Elvis为会议的需要捐赠了Alter板。 MEPhI,MIPT和SSAU的主板是基于Altera Cyclone V的Terasic DE0-CV:

另一块主板是Terasic DE0- Nano- 一种非常紧凑的披肩,适合飞行机器人之类的项目,但板上

装有少量外围设备:Terasic DE0-劣势Nano是板卡本身上的少量外围设备,但这也是一个优势,因为DE0-Nano可以作为设计人员与其他板卡连接并内置在不同的设备中:

在莫斯科工程物理研究所的饭厅吃完午餐后,我们开始了实际部分。最初,当Imagination Technologies和Xilinx在洛杉矶举行这样的研讨会时,他们使用了来自加利福尼亚南部的David和Sarah Harris教授准备的幻灯片。最初看起来,您可以在视频中看到:洛杉矶研讨会的所有8个视频在俄罗斯的研讨会上,必须对Harris的核心和实验室绑定进行大量修改。可以在https://github.com/MIPSfpga/mipsfpga-plus上找到修改内容。区别包括:1.所有东西都是从Altera便宜的主板上分类的,可以在俄罗斯使用,没有进出口引擎2.仅通过UART即可将程序加载到合成系统中,而无需使用BusBlaster。3.将光传感器用作外设,而不是LCD显示器4.可切换超低频时钟信号,允许实验室可视化任何处理器内部的操作5.添加了一个简单的实验室可视化高速缓存未命中+每件事物和化妆品-更紧凑的Bootloader / Bootloader,将不可缓存的交易范围缩小到内存的可能性等。更多详细信息:1.在Altera下移植首先,Harris幻灯片显示了Xilinx的所有内容,最近,从Xilinx FPGA到俄罗斯的运输板已经变成相当复杂的官僚程序,需要3-4个月的时间。即使有免费许可证,用于合成软件的许可证和Xilinx Vivado布局布线也发生了同样的事情。一些俄罗斯大学没有Xilinx董事会或Vivado许可证。其他人仅拥有Vivado的前身的旧许可证-2013 ISE软件,该软件不支持我在俄罗斯运输的板上的FPGA。简而言之,在俄罗斯举办的研讨会上,我和同志在加利福尼亚州将MIPSfpga移植到了Xilinx竞争对手Altera(该公司正在与Intel合并)的俄罗斯廉价主板上。 Zelenograd公司SPC Elvis为会议的需要捐赠了Alter板。 MEPhI,MIPT和SSAU的主板是基于Altera Cyclone V的Terasic DE0-CV:

另一块主板是Terasic DE0- Nano- 一种非常紧凑的披肩,适合飞行机器人之类的项目,但板上

装有少量外围设备:Terasic DE0-劣势Nano是板卡本身上的少量外围设备,但这也是一个优势,因为DE0-Nano可以作为设计人员与其他板卡连接并内置在不同的设备中:

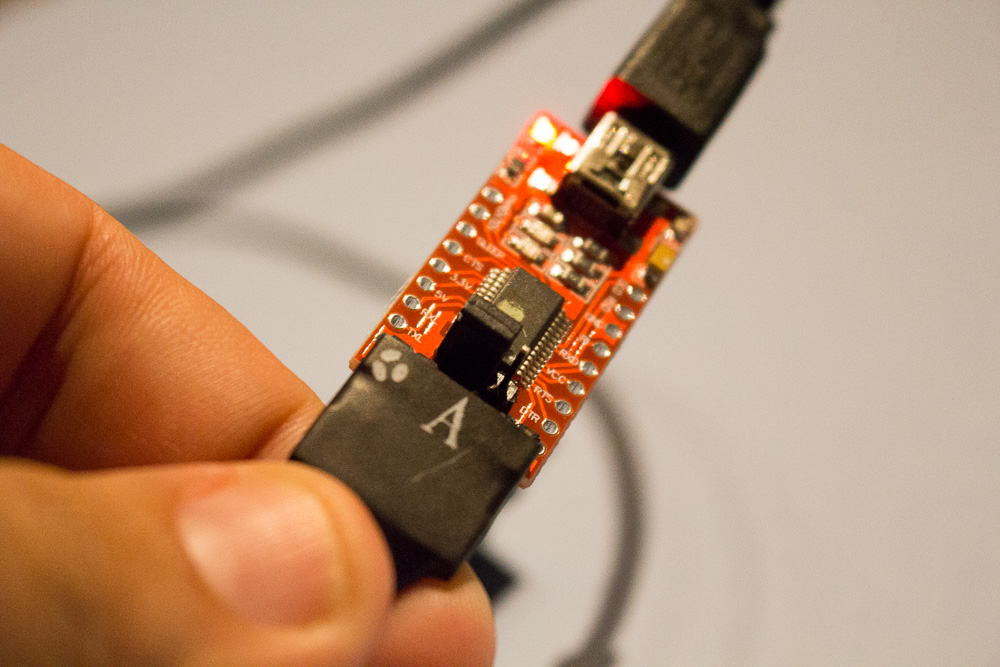

2.通过UART下载Harris 遇到的第二个问题是使用Bus Blaster调试适配器和称为OpenOCD的软件。基本上,BusBlaster / OpenOCD是同类解决方案。它不仅允许将程序加载到FPGA内部综合的系统中,还可以通过EJTAG接口进行远程调试,该接口是JTAG接口上的更高级别的插件。同时,BusBlaster仅售43美元,比工业调试EJTAG适配器便宜得多。不幸的是,BusBlaster / OpenOCD组合非常粗糙,我担心它不能在俄罗斯的某些意外计算机配置上运行(我是对的-它在MIPT和SSAU上不起作用)。除了,在出售用于MIPS的BusBlaster / OpenOCD组合的站点上,有时板用光了。由于这个和其他原因,我开始寻找将软件加载到系统中的其他方法(在FPGA中,您需要分别加载处理器的配置/硬件和软件(在具有处理器的综合系统中)。匿名互联网巨魔Alexey试图使我长期处于弱势地位,以便我可以通过Altera USB Blaster来实现EJTAG引导程序,但是由于我不是EJTAG专家,所以我选择了一个自苏联时代以来就一直有效的简单解决方案-通过串行端口/ UART加载程序。没错,在苏联时代,有一个RS-232C端口,在1990年代出现了FTDI的芯片,这使得通过连接到PC的USB电缆进行所有操作成为可能。可以在莫斯科以5美元的价格购买这种适配器的不同版本,而从中国通过互联网以不到2美元的价格购买:

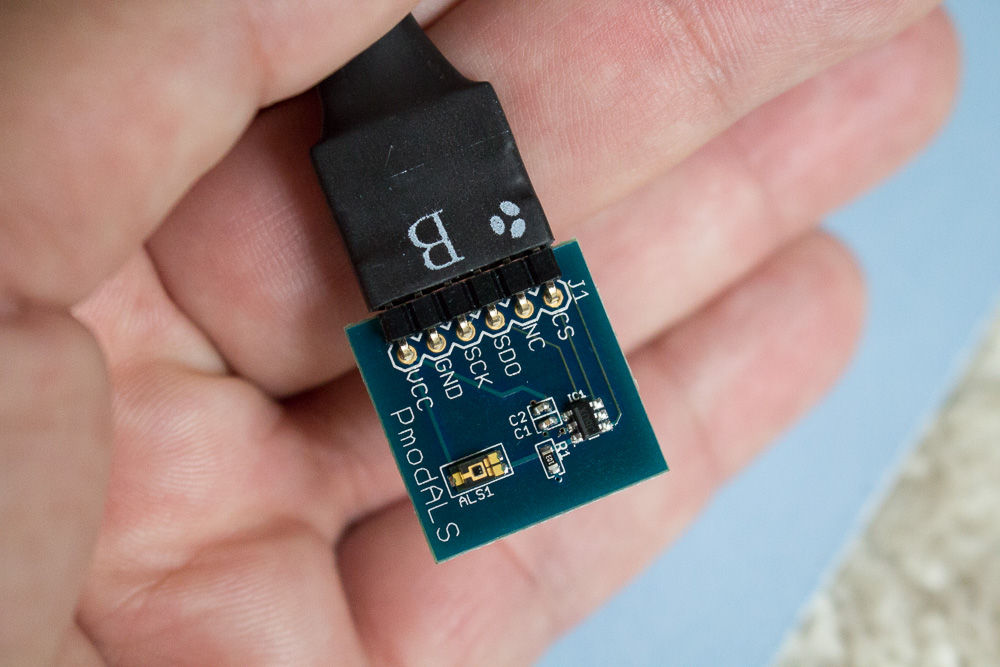

2.通过UART下载Harris 遇到的第二个问题是使用Bus Blaster调试适配器和称为OpenOCD的软件。基本上,BusBlaster / OpenOCD是同类解决方案。它不仅允许将程序加载到FPGA内部综合的系统中,还可以通过EJTAG接口进行远程调试,该接口是JTAG接口上的更高级别的插件。同时,BusBlaster仅售43美元,比工业调试EJTAG适配器便宜得多。不幸的是,BusBlaster / OpenOCD组合非常粗糙,我担心它不能在俄罗斯的某些意外计算机配置上运行(我是对的-它在MIPT和SSAU上不起作用)。除了,在出售用于MIPS的BusBlaster / OpenOCD组合的站点上,有时板用光了。由于这个和其他原因,我开始寻找将软件加载到系统中的其他方法(在FPGA中,您需要分别加载处理器的配置/硬件和软件(在具有处理器的综合系统中)。匿名互联网巨魔Alexey试图使我长期处于弱势地位,以便我可以通过Altera USB Blaster来实现EJTAG引导程序,但是由于我不是EJTAG专家,所以我选择了一个自苏联时代以来就一直有效的简单解决方案-通过串行端口/ UART加载程序。没错,在苏联时代,有一个RS-232C端口,在1990年代出现了FTDI的芯片,这使得通过连接到PC的USB电缆进行所有操作成为可能。可以在莫斯科以5美元的价格购买这种适配器的不同版本,而从中国通过互联网以不到2美元的价格购买: 我将立即指出,您可以通过不同的方式将程序加载到合成SoC中。在其中一种较为传统的系统中,系统在内存中有一个小型固定程序(引导程序),该程序在系统复位后启动并通过UART /串行端口加载较大的程序。 NIIIS的安东·帕夫洛夫(Anton Pavlov)使用了这种方法,他在莫斯科国立大学和莫斯科工程物理研究所的研讨会上演示了该方法,并且还在极客时代写了关于他的“ MIPSfpga:教规之外”。我以另一种方式进行了加载,其中内存中填充了状态机,状态机完全在硬件中实现。本机通过UART从PC接受Motorola S-Record格式的文本文件,当处理器处于复位状态时,解析它(硬件中的所有内容)并用数据填充内存。然后,处理器唤醒并开始从系统内存中读取程序。在PC端需要做的就是将可执行的ELF文件转换为Motorola S-Record格式,然后使用“ type” windows-shell命令将其发送到虚拟COM端口。3.以光传感器作为外围设备,而不是LCD显示器在最初的哈里斯实验室中,他们使用一个七段指示器和一个SPI LCD显示器作为外围设备的示例。一个带有七段指示灯的例子很无聊-任何学生都知道,如果您知道如何用一个灯闪烁,那么您就会知道如何用七个灯闪烁。 SPI示例要好一些,特别是对于初学者来说,但是如果已经有一个7段指示器,为什么我们需要第二个显示呢?简而言之,在去俄罗斯之前,我购买了20个带有SPI接口的光传感器,并使用它们代替了显示器:

同时,它的接口非常简单-这是我编写的接口模块(注意:此代码不包括用于与之配对的所有系统修改AHB-Lite总线,以便软件看到该值):

我将立即指出,您可以通过不同的方式将程序加载到合成SoC中。在其中一种较为传统的系统中,系统在内存中有一个小型固定程序(引导程序),该程序在系统复位后启动并通过UART /串行端口加载较大的程序。 NIIIS的安东·帕夫洛夫(Anton Pavlov)使用了这种方法,他在莫斯科国立大学和莫斯科工程物理研究所的研讨会上演示了该方法,并且还在极客时代写了关于他的“ MIPSfpga:教规之外”。我以另一种方式进行了加载,其中内存中填充了状态机,状态机完全在硬件中实现。本机通过UART从PC接受Motorola S-Record格式的文本文件,当处理器处于复位状态时,解析它(硬件中的所有内容)并用数据填充内存。然后,处理器唤醒并开始从系统内存中读取程序。在PC端需要做的就是将可执行的ELF文件转换为Motorola S-Record格式,然后使用“ type” windows-shell命令将其发送到虚拟COM端口。3.以光传感器作为外围设备,而不是LCD显示器在最初的哈里斯实验室中,他们使用一个七段指示器和一个SPI LCD显示器作为外围设备的示例。一个带有七段指示灯的例子很无聊-任何学生都知道,如果您知道如何用一个灯闪烁,那么您就会知道如何用七个灯闪烁。 SPI示例要好一些,特别是对于初学者来说,但是如果已经有一个7段指示器,为什么我们需要第二个显示呢?简而言之,在去俄罗斯之前,我购买了20个带有SPI接口的光传感器,并使用它们代替了显示器:

同时,它的接口非常简单-这是我编写的接口模块(注意:此代码不包括用于与之配对的所有系统修改AHB-Lite总线,以便软件看到该值):

4.时钟切换到超低频当MIPSfpga出现并且俄罗斯大学教授开始研究它时,一些人开始抱怨原始形式的软件包对于高级学生而言不是很有趣,因为David和Sarah Harris所准备的实验室使用了处理器。就像一个“黑匣子”,只需将设备连接到它。换句话说,哈里斯完全忽略了源代码中给出了处理器,因此可以使用它来实现实验,从而允许从任意处理器寄存器(不仅对程序员可见的寄存器,而且通常从任何D触发器)输出连接。例如LED,观察执行某些程序时处理器发生了什么。如您所知,为了使这种观察“实时”进行,有必要使处理器以非常低的时钟频率(例如每秒时钟)工作。怎么做?以28 nm技术在ASIC中实现的MIPS microAptiv UP内核可以在500 MHz以上的频率下工作,并在300 MHz以上的65 nm技术下工作。当在FPGA上实现时,频率要低得多,但仍然很高-50-60 MHz。在板上的时钟信号发生器的频率为50-100兆赫,随着增加或使用降低频率的可能性锁相环(PLL) / 锁相环(PLL) 。不幸的是,使用PLL,您可以将频率降低到〜100 KHz,但是您需要通过另一种方式将频率降低到1 Hz。最初,我尝试使用Altera的一个名为ALTCLKCTRL,但是由于某种原因它不起作用。然后我尝试使用计数器对时钟信号进行分频,但是(我已经知道)该解决方案本身不起作用,因为合成器无法理解输出信号是时钟信号并开始不正确地对其进行分频,结果导致处理器无法正常工作。我咨询了几个同志,然后我们开始使用Alter宏“ global”(以及Xilinx BUFG的等效宏)。

5.添加了一个简单的缓存未命中可视化实验室

4.时钟切换到超低频当MIPSfpga出现并且俄罗斯大学教授开始研究它时,一些人开始抱怨原始形式的软件包对于高级学生而言不是很有趣,因为David和Sarah Harris所准备的实验室使用了处理器。就像一个“黑匣子”,只需将设备连接到它。换句话说,哈里斯完全忽略了源代码中给出了处理器,因此可以使用它来实现实验,从而允许从任意处理器寄存器(不仅对程序员可见的寄存器,而且通常从任何D触发器)输出连接。例如LED,观察执行某些程序时处理器发生了什么。如您所知,为了使这种观察“实时”进行,有必要使处理器以非常低的时钟频率(例如每秒时钟)工作。怎么做?以28 nm技术在ASIC中实现的MIPS microAptiv UP内核可以在500 MHz以上的频率下工作,并在300 MHz以上的65 nm技术下工作。当在FPGA上实现时,频率要低得多,但仍然很高-50-60 MHz。在板上的时钟信号发生器的频率为50-100兆赫,随着增加或使用降低频率的可能性锁相环(PLL) / 锁相环(PLL) 。不幸的是,使用PLL,您可以将频率降低到〜100 KHz,但是您需要通过另一种方式将频率降低到1 Hz。最初,我尝试使用Altera的一个名为ALTCLKCTRL,但是由于某种原因它不起作用。然后我尝试使用计数器对时钟信号进行分频,但是(我已经知道)该解决方案本身不起作用,因为合成器无法理解输出信号是时钟信号并开始不正确地对其进行分频,结果导致处理器无法正常工作。我咨询了几个同志,然后我们开始使用Alter宏“ global”(以及Xilinx BUFG的等效宏)。

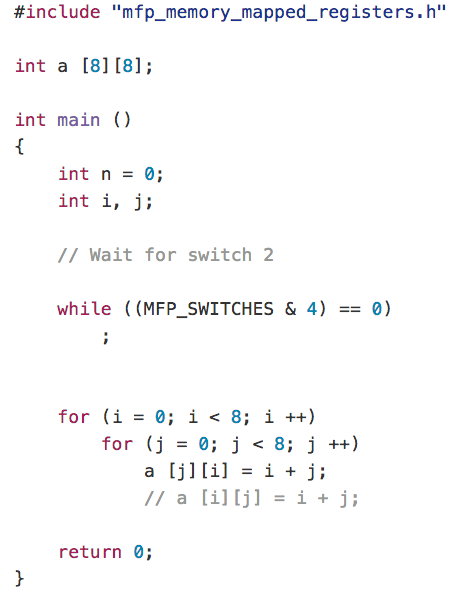

5.添加了一个简单的缓存未命中可视化实验室 现在,您可以进行有趣的实验-例如,使高速缓存未命中时LED闪烁,然后实时观察填充二维数组时高速缓存的命中和未命中。如果一行一行地填充数组,则闪烁将与填充列不同:请

注意,并非一切都顺利:

现在,您可以进行有趣的实验-例如,使高速缓存未命中时LED闪烁,然后实时观察填充二维数组时高速缓存的命中和未命中。如果一行一行地填充数组,则闪烁将与填充列不同:请

注意,并非一切都顺利: 1. DE0-Nano中的GPIO与DE0-CV和Xilinx板上的GPIO不同。特别是由于某种原因,我无法将整个GPIO端口声明为一个inout,然后将其各个位用作输入或输出。尽管在DE0-CV上可以正常运行。我没有时间在不同的逻辑(在Verilog上)信号之间分配不同的GPIO输出,所以我只是没有在DE0-Nano上用光传感器对实验室进行分类。由于相同的原因,我没有将Bus Blaster的接口导出到DE0-CV。2.更糟糕的是,通过UART下载DE0-Nano在MEPhI上不起作用,尽管之前在莫斯科国立大学和我的笔记本电脑上都可以。原因仍然不是100%清楚:2.1。 Windows版本(带补丁的7)和用于DE0-Nano的USB-to-UART电缆可能不兼容。该电缆是基于PL2303TA芯片组的廉价中国电缆克隆,尽管在研讨会之前我没有尝试过。众所周知,基于PL2303HX芯片组的此类电缆的先前版本存在与Windows 8的兼容性问题(请参阅参考资料)。我带给我的最令人发指的是一台装有Windows 7版本的笔记本电脑和一台装有Windows 8版本的笔记本电脑,以及各种替代品。但是我没有在研讨会之前检查所有组合,尽管我可以在前一天晚上做完-las。2.2。研讨会的前两天,我对时钟分频器进行了更改。这也不值得。2.3。好吧,至少在DE0-CV上一切正常。3.在MEPhI,我展示了比莫斯科国立大学更复杂的缓存示例版本。这是一个错误-在一个复杂的示例中,编译器优化了某些内容,并且灯光的图案不像最初的简单示例那样明显。

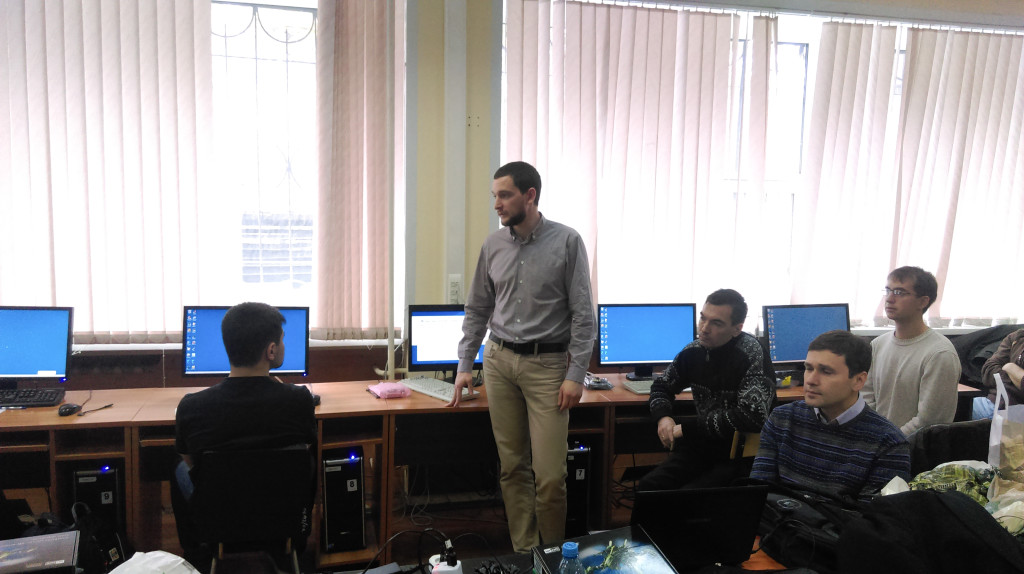

NIIMI邀请的另外一位发言人安东·帕夫洛夫(Anton Pavlov)挽救了局势,尽管他没有在MEPhI工作,但他展示了一些自己的MIPSfpga绑定版本,称为myMIPSfpga,他在笔记“ MIPSfpga:教规之外”中对此进行了描述。除其他外,安东已将MIPSfpga移植到俄罗斯火星探测器3

1. DE0-Nano中的GPIO与DE0-CV和Xilinx板上的GPIO不同。特别是由于某种原因,我无法将整个GPIO端口声明为一个inout,然后将其各个位用作输入或输出。尽管在DE0-CV上可以正常运行。我没有时间在不同的逻辑(在Verilog上)信号之间分配不同的GPIO输出,所以我只是没有在DE0-Nano上用光传感器对实验室进行分类。由于相同的原因,我没有将Bus Blaster的接口导出到DE0-CV。2.更糟糕的是,通过UART下载DE0-Nano在MEPhI上不起作用,尽管之前在莫斯科国立大学和我的笔记本电脑上都可以。原因仍然不是100%清楚:2.1。 Windows版本(带补丁的7)和用于DE0-Nano的USB-to-UART电缆可能不兼容。该电缆是基于PL2303TA芯片组的廉价中国电缆克隆,尽管在研讨会之前我没有尝试过。众所周知,基于PL2303HX芯片组的此类电缆的先前版本存在与Windows 8的兼容性问题(请参阅参考资料)。我带给我的最令人发指的是一台装有Windows 7版本的笔记本电脑和一台装有Windows 8版本的笔记本电脑,以及各种替代品。但是我没有在研讨会之前检查所有组合,尽管我可以在前一天晚上做完-las。2.2。研讨会的前两天,我对时钟分频器进行了更改。这也不值得。2.3。好吧,至少在DE0-CV上一切正常。3.在MEPhI,我展示了比莫斯科国立大学更复杂的缓存示例版本。这是一个错误-在一个复杂的示例中,编译器优化了某些内容,并且灯光的图案不像最初的简单示例那样明显。

NIIMI邀请的另外一位发言人安东·帕夫洛夫(Anton Pavlov)挽救了局势,尽管他没有在MEPhI工作,但他展示了一些自己的MIPSfpga绑定版本,称为myMIPSfpga,他在笔记“ MIPSfpga:教规之外”中对此进行了描述。除其他外,安东已将MIPSfpga移植到俄罗斯火星探测器3 作为一名遭受进出口折磨的男人(Scylla:美国出口管制+ Charybdis:俄罗斯习俗),我将尝试在俄罗斯进行以下教育活动:

休息时间和研讨会结束后,Maxim Gorbunov向我展示了各种神话般的景象,包括根据仙女座星系和红色和白色多册分子咖啡馆的时代精神,三个面板来自1960年:

UPD:正如评论中开始讨论mifishnuyu教堂一样,我会做一下(我未插入l此片段最初是因为他不确定是否适合极客时间而创建的):

作为一名遭受进出口折磨的男人(Scylla:美国出口管制+ Charybdis:俄罗斯习俗),我将尝试在俄罗斯进行以下教育活动:

休息时间和研讨会结束后,Maxim Gorbunov向我展示了各种神话般的景象,包括根据仙女座星系和红色和白色多册分子咖啡馆的时代精神,三个面板来自1960年:

UPD:正如评论中开始讨论mifishnuyu教堂一样,我会做一下(我未插入l此片段最初是因为他不确定是否适合极客时间而创建的):

我去了一个神话般的教堂,大约三年前,那里的互联网上有那么多尖叫声,因此,员工甚至离开莫斯科工程物理研究所进行抗议。作为中立的人 我是一位真正的信徒,而不是冲突的一方或另一方的激进支持者,我必须说:1)神话中的教堂相当谦虚而不庸俗,其精神类似于旧金山的东正教大教堂;2)MEPhI不是第一所有宗教信仰的俄罗斯大学,正教课程最早出现在1988年的莫斯科物理技术学院(当时整个物理技术学院都来到他身边,学生们听了第一堂课的演讲,但是三个月后,不超过十二名学生); 3)许多美国大学都有教堂。

未完待续。

我去了一个神话般的教堂,大约三年前,那里的互联网上有那么多尖叫声,因此,员工甚至离开莫斯科工程物理研究所进行抗议。作为中立的人 我是一位真正的信徒,而不是冲突的一方或另一方的激进支持者,我必须说:1)神话中的教堂相当谦虚而不庸俗,其精神类似于旧金山的东正教大教堂;2)MEPhI不是第一所有宗教信仰的俄罗斯大学,正教课程最早出现在1988年的莫斯科物理技术学院(当时整个物理技术学院都来到他身边,学生们听了第一堂课的演讲,但是三个月后,不超过十二名学生); 3)许多美国大学都有教堂。

未完待续。

Source: https://habr.com/ru/post/zh-CN387157/

All Articles