大象分销:带有MIPSfpga的用于教育项目的FPGA板

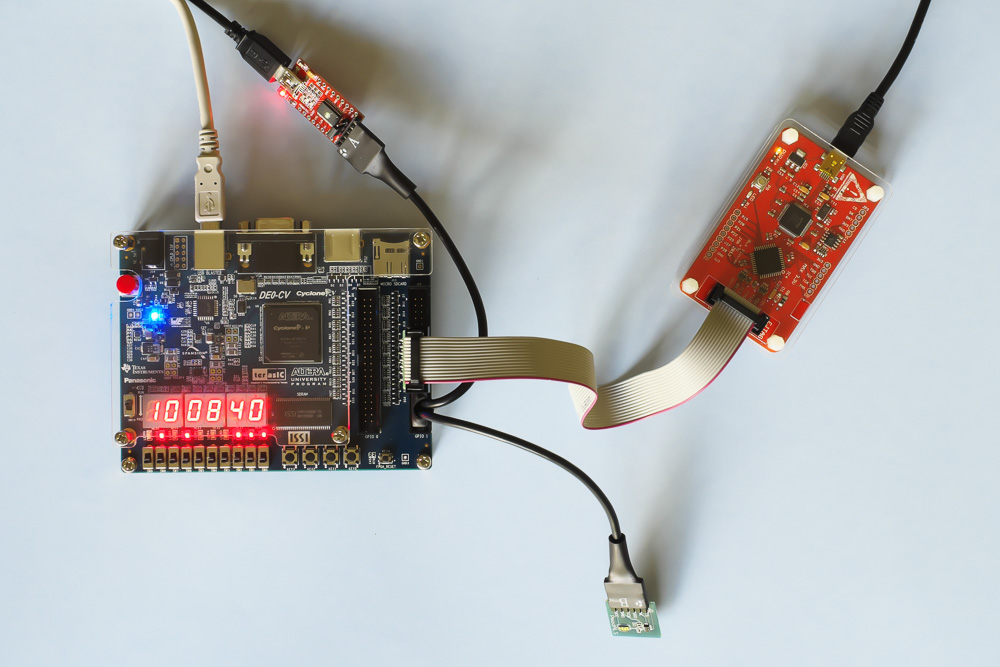

一个月前在俄罗斯的大学,研讨会举行MIPSfpga(1,2,3,4),并NIISI名为安东·巴甫洛夫dzhentlemen写了关于他自己的改进MIPSfpga记«MIPSfpga:佳能之外”。自从教授们普遍为积极地为电子学学生提供教学的新产品以来,这个想法就出现了,以帮助从董事会开始,并同时为多个人和组织提供帮助。特别是为了纪念新年,我与univeda.ru的 Vitaliy Kravchenko合作我们正计划分发少量大象,即免费的Terasic DE0-CV板和FPGA Altera CycloneV。因此,您可以重复Anton Pavlov的壮举。由于这种特殊的分发不是用Imagination Technologies的钱而不是用Altera的钱,不是猫王科学与生产中心的钱来完成的,而是由包括我本人在内的私人捐助者的钱来完成的,因此这些大象将按照以下所述的特定条件进行分发。

此次活动的目的:

1.提高俄罗斯大学对处理器微体系结构,SoC和异构多核系统领域的世界研究的参与度

2.增加MIPS Insider上的俄语文本数量,以便来自国际电子行业和学术界的参观者开始了解俄罗斯即将到来 3.代表社区制作有关MIPSfpga的一堆培训资料,俄罗斯大学的老师和其他国家(美国,日本,中国等)的大学教授均可使用。条款:1.收款人最好是老师,研究生或俄罗斯大学的学生。2.最好这所大学不是莫斯科国立大学,莫斯科物理技术学院,MEPhI,MIET和ITMO,它们可以从其他来源收取这些费用。3.非常理想的是,一个有创造力的朋友在收到董事会之前,不仅要给我发送项目说明,还要给我发送Verilog或VHDL,C和/或汇编程序中的代码,他用该代码在ModelSim或Icarus环境中模拟未来的综合系统的原型。也欢迎时序图。4.完成后,项目代码将上传到http://github.com/MIPSfpga-例如,请参见http://github.com/MIPSfpga/mipsfpga-plus5 ,并在Wiki部分中进行了描述:5.1。每个文件中有什么5.2。硬件模块的层次结构5.3。如何模拟-屏幕截图说明5.4。仿真时序图5.5。如何合成-屏幕截图5.6的说明。综合结果-大小和最大频率5.7。软件部分5.8的说明。工作中的FPGA6的照片。它以第

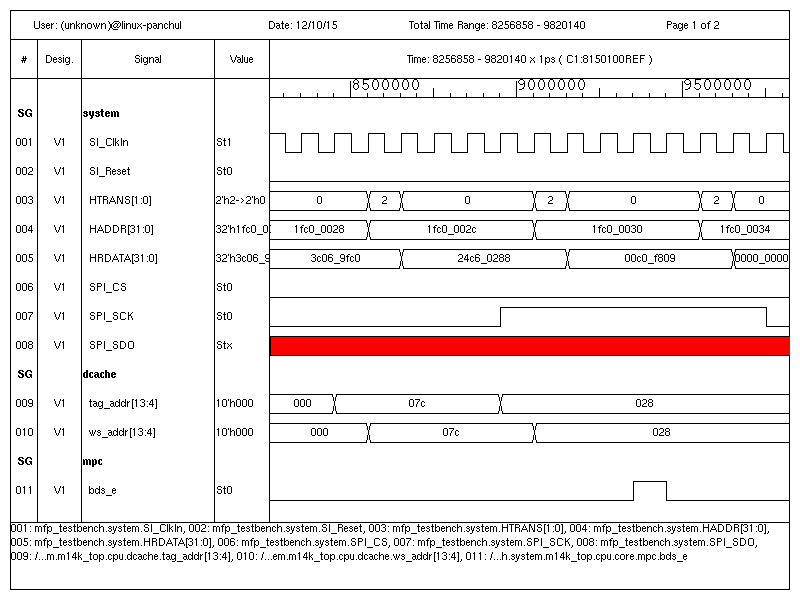

7 条的形式放在http://geektimes.ru上。同样在http://silicon-russia.com8 上列出。同样在http://community.imgtec.com上列出。/论坛/ cat / mips-insider / mipsfpga9.语言(6),(7),(8)可以是俄语或英语10.如果您在一个月内没有对董事会做任何事情,该董事会将从您撤回并转移给其他人。11.如果我们(I和UnivEDA)将在俄罗斯进行任何活动,例如比赛或培训,我们也会向您收取费用花点时间回溯一下带有板卡的项目示例:1. MIPSfpga与具有SPI,I2C,UART等接口的传感器之间的接口。湿度,温度,声音,指南针,测距仪等传感器2. MIPSfpga与FPGA存储器-SDRAM,DDR等外部接口。 (在当前示例中,系统存储器是从FPGA内部的块存储器构建的)。3. MIPSfpga与较大设备之间的接口是VGA显示器,鼠标,键盘,操纵杆。4.通过以每秒1个时钟的频率运行处理器并输出与事务相关的信号(请求,未命中等)来可视化缓存。5.通过以每秒1个时钟的频率启动处理器并输出传送带的控制信号等来可视化传送带和算术设备的操作。6.使用CorExtend /用户定义指令(UDI)界面将命令添加到处理器。一个示例是特殊的加密命令。7.实验室工作,演示不同模式下的中断操作以及中断处理程序。8. AHB-Lite总线与其他总线之间的桥梁-AXI,APB,OCP,Wishbone,PLB等。9.多处理器系统,它们不具有一级缓存的一致性,并且(对于最高级的)具有一致性的缓存和诸如MESI之类的协议的实现。10.移植到MIPSfpga的各种程序和操作系统-从简单的RTOS到各种Linux变体(MIPSfpga支持TLB MMU)。请将建议与yuri@panchul.com的副本发送至yuri.panchul@imgtec.com

3.代表社区制作有关MIPSfpga的一堆培训资料,俄罗斯大学的老师和其他国家(美国,日本,中国等)的大学教授均可使用。条款:1.收款人最好是老师,研究生或俄罗斯大学的学生。2.最好这所大学不是莫斯科国立大学,莫斯科物理技术学院,MEPhI,MIET和ITMO,它们可以从其他来源收取这些费用。3.非常理想的是,一个有创造力的朋友在收到董事会之前,不仅要给我发送项目说明,还要给我发送Verilog或VHDL,C和/或汇编程序中的代码,他用该代码在ModelSim或Icarus环境中模拟未来的综合系统的原型。也欢迎时序图。4.完成后,项目代码将上传到http://github.com/MIPSfpga-例如,请参见http://github.com/MIPSfpga/mipsfpga-plus5 ,并在Wiki部分中进行了描述:5.1。每个文件中有什么5.2。硬件模块的层次结构5.3。如何模拟-屏幕截图说明5.4。仿真时序图5.5。如何合成-屏幕截图5.6的说明。综合结果-大小和最大频率5.7。软件部分5.8的说明。工作中的FPGA6的照片。它以第

7 条的形式放在http://geektimes.ru上。同样在http://silicon-russia.com8 上列出。同样在http://community.imgtec.com上列出。/论坛/ cat / mips-insider / mipsfpga9.语言(6),(7),(8)可以是俄语或英语10.如果您在一个月内没有对董事会做任何事情,该董事会将从您撤回并转移给其他人。11.如果我们(I和UnivEDA)将在俄罗斯进行任何活动,例如比赛或培训,我们也会向您收取费用花点时间回溯一下带有板卡的项目示例:1. MIPSfpga与具有SPI,I2C,UART等接口的传感器之间的接口。湿度,温度,声音,指南针,测距仪等传感器2. MIPSfpga与FPGA存储器-SDRAM,DDR等外部接口。 (在当前示例中,系统存储器是从FPGA内部的块存储器构建的)。3. MIPSfpga与较大设备之间的接口是VGA显示器,鼠标,键盘,操纵杆。4.通过以每秒1个时钟的频率运行处理器并输出与事务相关的信号(请求,未命中等)来可视化缓存。5.通过以每秒1个时钟的频率启动处理器并输出传送带的控制信号等来可视化传送带和算术设备的操作。6.使用CorExtend /用户定义指令(UDI)界面将命令添加到处理器。一个示例是特殊的加密命令。7.实验室工作,演示不同模式下的中断操作以及中断处理程序。8. AHB-Lite总线与其他总线之间的桥梁-AXI,APB,OCP,Wishbone,PLB等。9.多处理器系统,它们不具有一级缓存的一致性,并且(对于最高级的)具有一致性的缓存和诸如MESI之类的协议的实现。10.移植到MIPSfpga的各种程序和操作系统-从简单的RTOS到各种Linux变体(MIPSfpga支持TLB MMU)。请将建议与yuri@panchul.com的副本发送至yuri.panchul@imgtec.com

Source: https://habr.com/ru/post/zh-CN387803/

All Articles