英特尔放弃滴答滴答策略

现在,处理器将执行“过程架构优化”循环

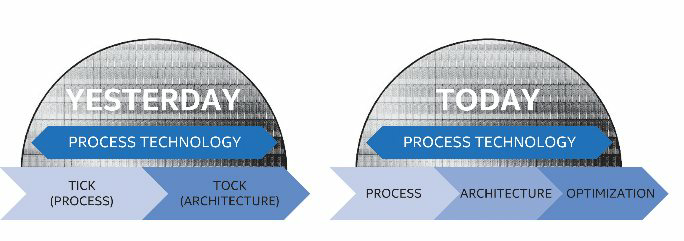

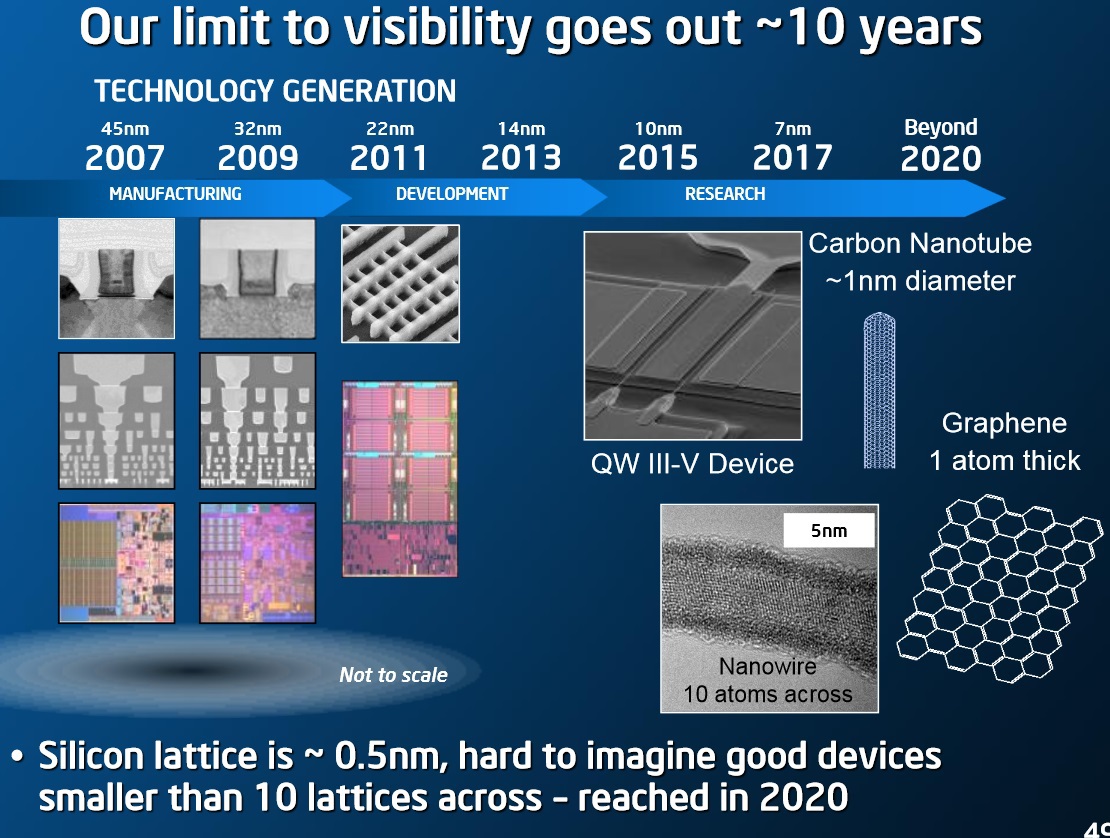

作为一家拥有500多家股东拥有超过1000万美元资产的上市公司,英特尔已向美国证券交易委员会提供了年度10-K报告。在150页的文档中,特别令人感兴趣的是第14页,英特尔在该页上承认,它放弃了逐笔策略,而采用了新的流程体系结构优化概念。Tick-Tock是英特尔自2007年以来一直使用的微处理器开发模型。该技术使您可以在一定的间隔内减小板上元件的尺寸,从而降低功耗,并在相同尺寸的芯片上安装更多数量的晶体管。如果可以容纳更多的元素,那么新的微体系结构是可能的:添加新命令,改进工作逻辑,增加不同元素的数量。逐笔策略将这两个过程分开。在“刻度”上,晶体管变得更小。微体系结构中有一些变化,但是它们并不重要。 “如此”是指创建新的微体系结构,即进行大规模的,有时是根本性的更改,以实现较大的生产率增长。英特尔近十年来一直在采取这样的措施。他们每个人都需要一年到一年半的时间。但是最近,减少制造过程变得越来越困难。当从22纳米切换到14纳米时,会出现6–9个月的延迟。此时,有必要将可加工芯片从晶片的输出百分比增加到成本可接受的水平。摩尔定律要求每24个月将芯片上的晶体管数量增加一倍,因此必须进行调整。将来,计划过渡到10纳米,然后过渡到7纳米和5纳米。实现新的领域意味着可以在深紫外线,自对准四重图案(SAQP)中使用平版印刷技术,支持III-V半导体,碳纳米管和石墨烯的硅排斥技术。

作为一家拥有500多家股东拥有超过1000万美元资产的上市公司,英特尔已向美国证券交易委员会提供了年度10-K报告。在150页的文档中,特别令人感兴趣的是第14页,英特尔在该页上承认,它放弃了逐笔策略,而采用了新的流程体系结构优化概念。Tick-Tock是英特尔自2007年以来一直使用的微处理器开发模型。该技术使您可以在一定的间隔内减小板上元件的尺寸,从而降低功耗,并在相同尺寸的芯片上安装更多数量的晶体管。如果可以容纳更多的元素,那么新的微体系结构是可能的:添加新命令,改进工作逻辑,增加不同元素的数量。逐笔策略将这两个过程分开。在“刻度”上,晶体管变得更小。微体系结构中有一些变化,但是它们并不重要。 “如此”是指创建新的微体系结构,即进行大规模的,有时是根本性的更改,以实现较大的生产率增长。英特尔近十年来一直在采取这样的措施。他们每个人都需要一年到一年半的时间。但是最近,减少制造过程变得越来越困难。当从22纳米切换到14纳米时,会出现6–9个月的延迟。此时,有必要将可加工芯片从晶片的输出百分比增加到成本可接受的水平。摩尔定律要求每24个月将芯片上的晶体管数量增加一倍,因此必须进行调整。将来,计划过渡到10纳米,然后过渡到7纳米和5纳米。实现新的领域意味着可以在深紫外线,自对准四重图案(SAQP)中使用平版印刷技术,支持III-V半导体,碳纳米管和石墨烯的硅排斥技术。 从一年前的演示幻灯片。证券交易委员会的一篇论文论述了英特尔的整体发展历程。该公司解释说,当前工艺技术的产品总使用时间将增加到14纳米,将来将增加到10纳米。但是新产品发布的市场步伐将继续。如何实现?英特尔给出了图像,该图像在这篇文章中发布在kat之前。其中,“ tick-tock”被称为昨天的技术,而三步循环的“过程体系结构优化”(PAO)被宣布为当前现实。22纳米Haswell的追随者Broadwell帮助设计了14纳米。英特尔当前的微体系结构是第六代Core处理器Skylake,即“ so” 14nm工艺技术。它的追随者Kaby Lake也将采用14纳米制程,但将“在第六代Core处理器系列上提供显着的性能改进”。该文件提到的与ASML的合作可以帮助达到10纳米,以研究深紫外光刻技术,包括适用于直径为300和450毫米的板。英特尔仍然保持领先地位:2014年8月推出了14纳米工艺,三星和台积电后来又挺身而出。预计将于今年发布14nm Kaby Lake。根据目前的计划,在10纳米Cannonlake微体系结构上的产品应该在2017年出现。在三步循环中,很容易看到最终用户的明显优势:同一块主板可以适用于两代或更多代产品。

从一年前的演示幻灯片。证券交易委员会的一篇论文论述了英特尔的整体发展历程。该公司解释说,当前工艺技术的产品总使用时间将增加到14纳米,将来将增加到10纳米。但是新产品发布的市场步伐将继续。如何实现?英特尔给出了图像,该图像在这篇文章中发布在kat之前。其中,“ tick-tock”被称为昨天的技术,而三步循环的“过程体系结构优化”(PAO)被宣布为当前现实。22纳米Haswell的追随者Broadwell帮助设计了14纳米。英特尔当前的微体系结构是第六代Core处理器Skylake,即“ so” 14nm工艺技术。它的追随者Kaby Lake也将采用14纳米制程,但将“在第六代Core处理器系列上提供显着的性能改进”。该文件提到的与ASML的合作可以帮助达到10纳米,以研究深紫外光刻技术,包括适用于直径为300和450毫米的板。英特尔仍然保持领先地位:2014年8月推出了14纳米工艺,三星和台积电后来又挺身而出。预计将于今年发布14nm Kaby Lake。根据目前的计划,在10纳米Cannonlake微体系结构上的产品应该在2017年出现。在三步循环中,很容易看到最终用户的明显优势:同一块主板可以适用于两代或更多代产品。Source: https://habr.com/ru/post/zh-CN392041/

All Articles