4月24日至29日,一系列针对学童的研讨会将在基辅举行,这看起来不像Lego / Arduino / Rasberry Pye标准使用的内置处理器的普通班级。 研讨会的主要重点不是讲授如何对处理器进行编程,而是展示如何在内部设计处理器的原理。 就像“教如何驾驶汽车”和“教如何设计引擎”之间的区别一样。 在研讨会上,学生将使用Verilog设备描述语言和逻辑综合-苹果,三星和其他电子公司的数字芯片开发人员使用的技术。

研讨会的官方页面,请在

此处进行注册 。

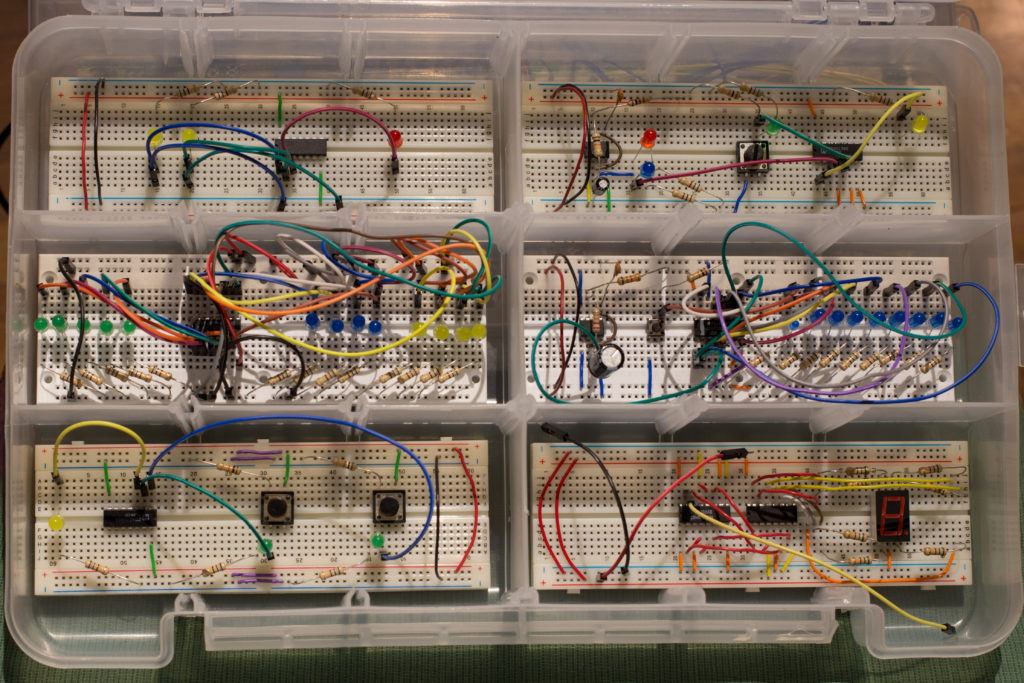

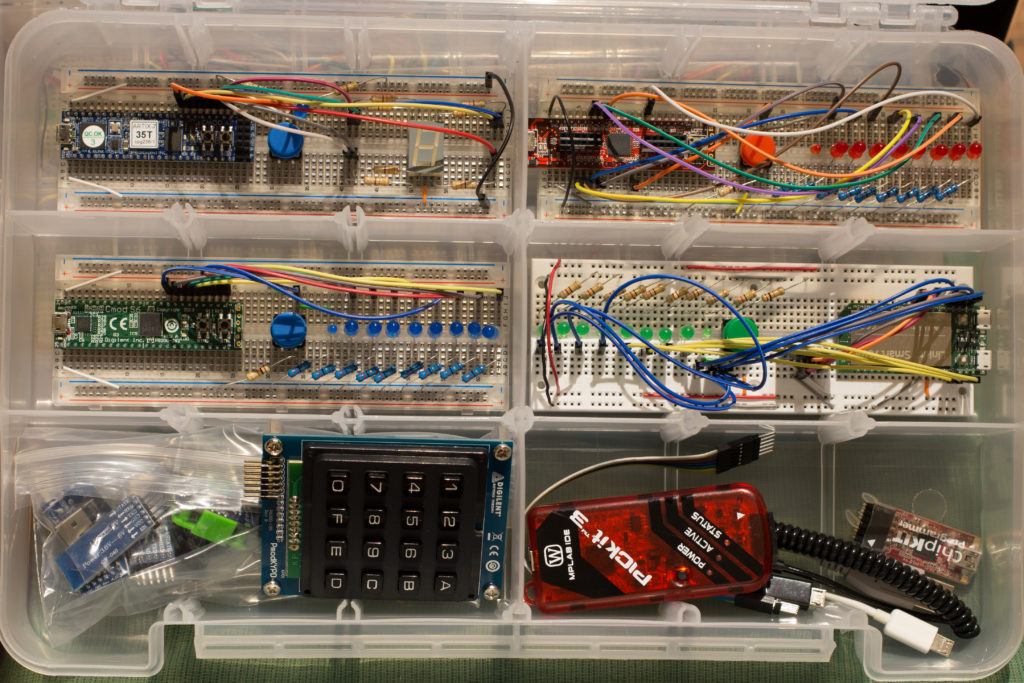

在练习中,使用带有FPGA的板-具有可变功能的逻辑元素矩阵(这不是普通的“处理器+存储器”)。 长期以来,FPGA一直被用来在斯坦福大学和麻省理工学院教授学生如何设计电子产品,最近在俄罗斯和乌克兰的大学中也是如此。 使用FPGA教育学童是一个实验,您有机会参与其中。 为了方便进入Verilog和FPGA,我们将首先在无焊接原型板上进行微集成度很小的微电路练习。 然后,我们将讨论FPGA,在研讨会的最后一天,我们将FPGA设计与用于物联网的微处理器编程进行比较。

您将最终看到在学生很少看的地方晶体管和Arduino之间发生了什么!

高中生和初中生课程4月24日,星期一。 我们开始使用FPGA:小集成度微电路上的组合逻辑和二进制算术

高中生和初中生课程4月24日,星期一。 我们开始使用FPGA:小集成度微电路上的组合逻辑和二进制算术地点:Belka KPI学生空间

- 16:00-17:00亚历山大·巴拉巴诺夫(KNU) 从物理到逻辑。

- 什么是电流,电压和电阻。

- 面包板如何工作?

- 练习1.第一个电路由电池,LED和电阻组成。 为什么要用LED将电阻器连接到电路上。

- 什么是晶体管以及如何从中构建逻辑元件。

- 练习2.观察晶体管的操作。

- 17:00-18:00 Yuri Panchul,Imagination Technologies。 逻辑的布尔代数,逻辑元素“与非”。

- 练习3.向每个学生提供了CMOS 4000系列的个人逻辑芯片,制造商提供了技术说明,其任务是绘制真值表,演示其工作并口头描述该功能。 逻辑元素AND,OR,XOR,NOR,NAND具有不同数量的输入。

- 练习4:我们研究什么是上拉电阻以及为什么需要它们。 在练习中添加3个按钮和上拉电阻。

- 18:00-19:00二进制算术,加法和乘法。

- 练习5.向每个学生提供一个加法器CMOS4008。演示在面包板上的加法器。

- 19:00-21:00为那些完成了练习1-5并且不想回家的人提供的额外练习。

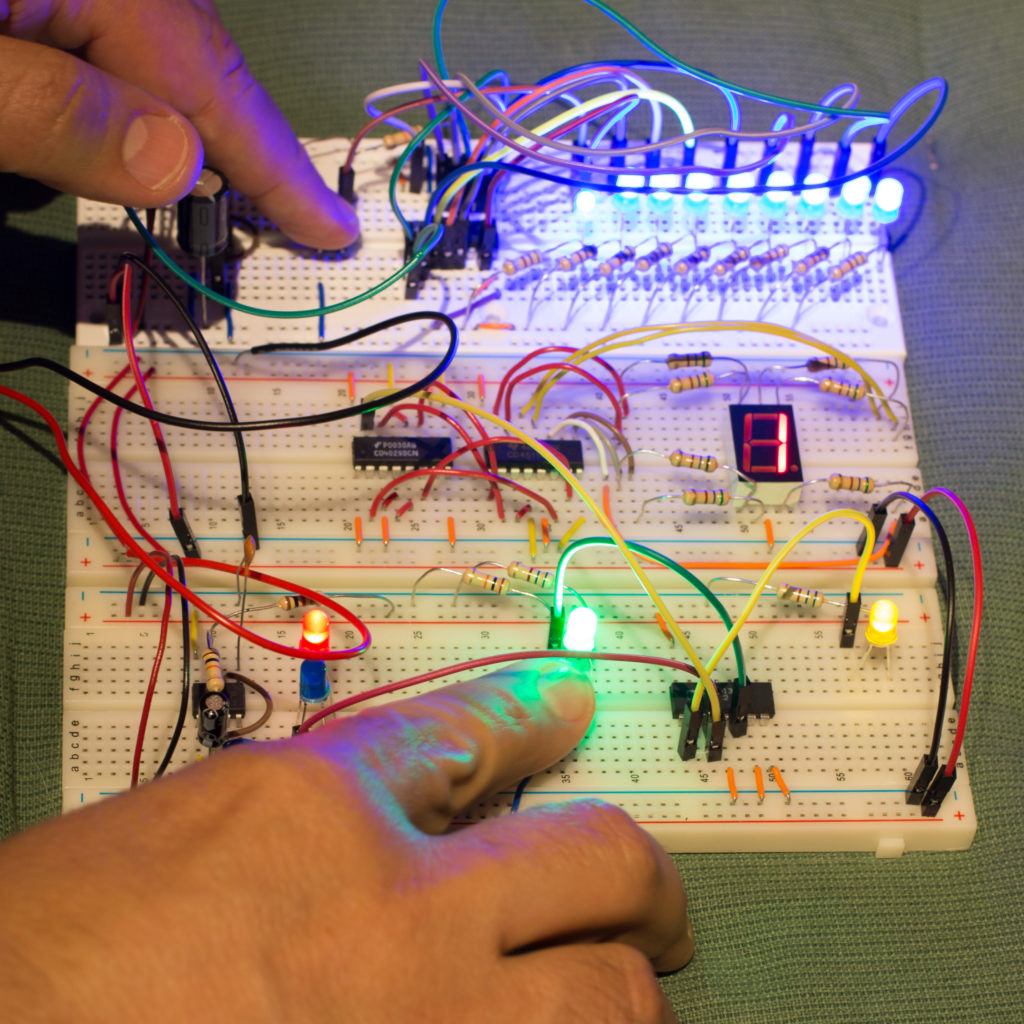

- 练习6:一个七段指示器及其驱动器,以组合电路为例。 七段指标加法器结果的结论。

4月25日,星期二。 增加内存:微电路上的顺序逻辑,集成度小。

4月25日,星期二。 增加内存:微电路上的顺序逻辑,集成度小。- 16:00-16:30尤里·潘丘(Yuri Panchul)。 顺序逻辑是使计算机“智能”的原因,它赋予其内存和重复操作的能力。

- 16:30-17:00 Yuri Panchul和KPI的讲师。

- 什么是D触发器。

- 练习7.我们基于D触发器中的555定时器连接时钟发生器,并检查编译电路的操作。

- 17:00-19:00顺序逻辑的更复杂元素。

- 练习8.移位寄存器和移动灯。

- 练习9:在七段指标上得出结论。

- 19:00-21:00尤金·科洛特基(KPI)。 对于已经完成练习6-8并不想回家的人来说,还可以进行其他练习。

- 练习10。我们检查基于555芯片计时器的时钟发生器。 我们观察到时钟频率的周期如何根据电阻器的电阻和电容器的电容而变化。

4月26日,星期三。 Verilog和FPGA上的组合逻辑和二进制算术。

4月26日,星期三。 Verilog和FPGA上的组合逻辑和二进制算术。地点:贝尔卡KPI学生空间。

- 16:00-16:30 Yuri Panchul,以及KPI,KNU的讲师。 快速介绍Verilog硬件描述语言以及在FPGA / FPGA中使用逻辑综合。 我们仅考虑组合逻辑。

- 16:30-17:00 KNU,KNU的讲师。 Verilog上的拉曼逻辑。

- 练习11。使用Digilent CMOD A7 35T:可面包板上的Artix-7 FPGA模块,在FPGA上重复练习2(逻辑元素)。

- 练习12.我们在一个七段的指示器上显示我们名字和姓氏的首字母,然后使用按钮在它们之间切换。

- 练习13.在FPGA上重复练习3(加法器)。 结果显示在七段指示器上。

- 19:00-21:00。 精通9-11练习并且不想回家的人的其他练习。

- 练习14.模块的层次结构。 带子模块的多路复用器的构造。

- 练习15.不使用FPGA建模Verilog代码。 我们创建了一个环境,用于检查Verilog中描述的电路的运行情况。 我们使用Icarus Verilog模拟器进行建模,并使用GTKWave程序查看时间图。

Verilog硬件描述语言中的示例代码,该代码被翻译(合成)为电路:

module counter ( input clock, input reset_n, output reg [31:0] count ); always @(posedge clock or negedge reset_n) begin if (! reset_n) count <= 32'b0; else count <= count + 32'b1; end endmodule //---------------------------------------------------------------------------- module seven_segment_display_driver ( input [3:0] number, output reg [6:0] abcdefg ); // abcdefg dp // 7 6 4 2 1 9 10 5 7- // 7 6 5 4 3 2 1 pio // --a-- // | | // fb // | | // --g-- // | | // ec // | | // --d-- always @* case (number) 4'h0: abcdefg = 7'b1111110; 4'h1: abcdefg = 7'b0110000; 4'h2: abcdefg = 7'b1101101; 4'h3: abcdefg = 7'b1111001; 4'h4: abcdefg = 7'b0110011; 4'h5: abcdefg = 7'b1011011; 4'h6: abcdefg = 7'b1011111; 4'h7: abcdefg = 7'b1110000; 4'h8: abcdefg = 7'b1111111; 4'h9: abcdefg = 7'b1111011; 4'ha: abcdefg = 7'b1110111; 4'hb: abcdefg = 7'b0011111; 4'hc: abcdefg = 7'b1001110; 4'hd: abcdefg = 7'b0111101; 4'he: abcdefg = 7'b1001111; 4'hf: abcdefg = 7'b1000111; endcase endmodule //---------------------------------------------------------------------------- module top ( input CLK, // 12 MHz inout [48:1] pio // GPIO, General-Purpose Input/Output ); wire reset_n = ! pio [8]; wire [31:0] count; counter counter_i ( .clock ( CLK ), .reset_n ( reset_n ), .count ( count ) ); seven_segment_display_driver display_driver_i ( .number ( count [26:23] ), .abcdefg ( pio [ 7: 1] ) ); endmodule

4月27日,星期四。 Verilog和FPGA上的顺序逻辑和状态机。地点:贝尔卡KPI学生空间。

- 16:00-17:00。 尤里·潘丘(Yuri Panchul)。 Verilog上的顺序逻辑,状态机,RTL方法论的概念(寄存器传输级别),信号传播延迟以及对数字电路合成的限制,确定了数字电路的最大可能时钟频率。

- 17:00-19:00。 KNU,KNU的讲师。 Verilog上的顺序逻辑。

- 练习16:在七段指标上得出一个状态结论。 在FPGA上实现练习9。

- 练习17.移位寄存器和移动灯。 在FPGA上实现练习8。

- 练习18.产生各种频率的声音及其叠加。

- 19:00-21:00。 那些适合参加练习17-18并希望继续锻炼的人的补充练习。

- 练习19:“蜗牛微笑”:有限状态机的一个例子。

- 练习20.构建算术传送带。 我们使用Icarus Verilog仿真器来设置时序电路。

4月28日,星期五。 电路设计与嵌入式微处理器编程的比较。

4月28日,星期五。 电路设计与嵌入式微处理器编程的比较。地点:贝尔卡KPI学生空间。

- 16:00-16:30。尤里·潘丘(Yuri Panchul)。 编程与电路的不同之处。 冯·诺依曼机器是电子电路的特例。 程序像冯·诺依曼机器的指令链一样。 MediaTek MT7688和Microchip PIC32MZ中使用的微处理器内核概述。

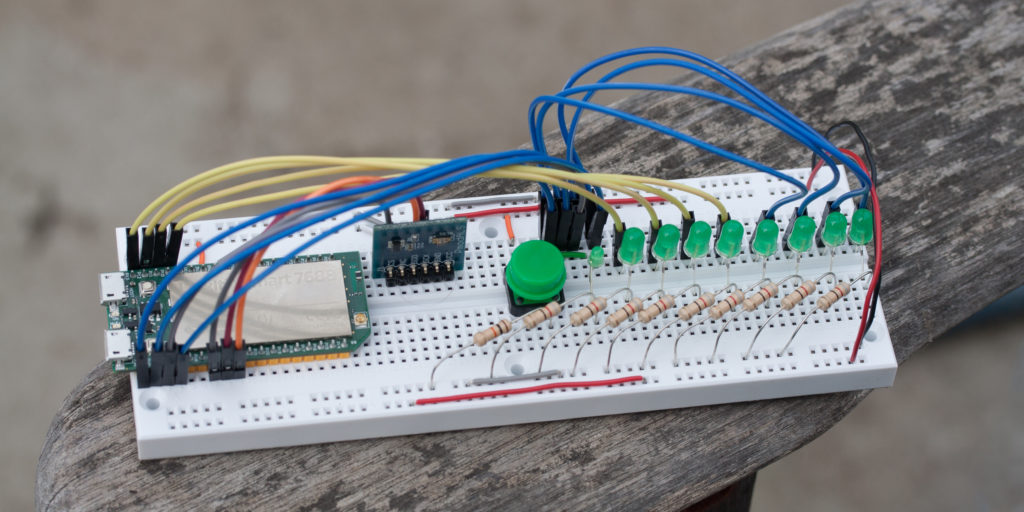

- 16:30-19:00尤金·科洛特基(Eugene Korotky)。 示例:由联发科MT7688支持的LinkIt Smart 7688物联网平台。

- 练习21.使用Python程序使LED闪烁。

- 练习22.使用SPI协议从Digilent PMOD ALS环境光传感器读取数据。

- 练习23.中断概念的介绍。

- 19:00-21:00。 对于已经掌握LinkIt Smart 7688上的练习并希望继续工作的人员,还可以进行其他练习。 示例:Microchip PIC32单片机。

- 练习24.使用C程序使LED闪烁。

- 练习25.使用SPI协议从Digilent PMOD ALS光传感器读取数据。

- 练习26.使用中断卸载主程序。 计时器的中断触发SPI事务; SPI的中断表示收到数据包。

4月29日,星期六。 黑客马拉松

4月29日,星期六。 黑客马拉松地点:国立大学“基辅-莫哈拉学院”

- 集成度较小的微电路项目:“土壤水分检测器”,“警笛”

- 带有FPGA的项目:传感器接口,“密码锁”类型的状态机

- 具有用于物联网的微控制器和嵌入式微处理器的项目:与传感器和执行器的连接

小学生课程四月精读“电子学概论”4月24日,星期一。

小学生课程四月精读“电子学概论”4月24日,星期一。 熟悉以下基本知识:欧姆定律,无源电子元件(电阻器和电容器)

地点:乌克兰射电乌克兰办事处,乔科洛夫斯基大道,42-A

时间: 17:00-19:00

讲师: Sergey Chenash

- 什么是电流,电压和电阻,欧姆定律

- 面包板怎么样

- 如何使用万用表

- 电阻及其应用

- 电容器作为电荷存储装置及其应用

4月25日,星期二。 有源电子元件:二极管和晶体管的结构和工作原理

地点:乌克兰射电乌克兰办事处,乔科洛夫斯基大道,42-A

时间: 17:00-19:00

讲师: Sergey Chenash

- 半导体的特性,pn结的结构

- 二极管及其分类如何工作

- 晶体管的工作原理及其应用

4月27日,星期四。 光电元件的研究:LED,光敏电阻,光电晶体管,光耦合器

地点:乌克兰射电乌克兰办事处,乔科洛夫斯基大道,42-A

时间: 17:00-19:00

讲师: Sergey Chenash

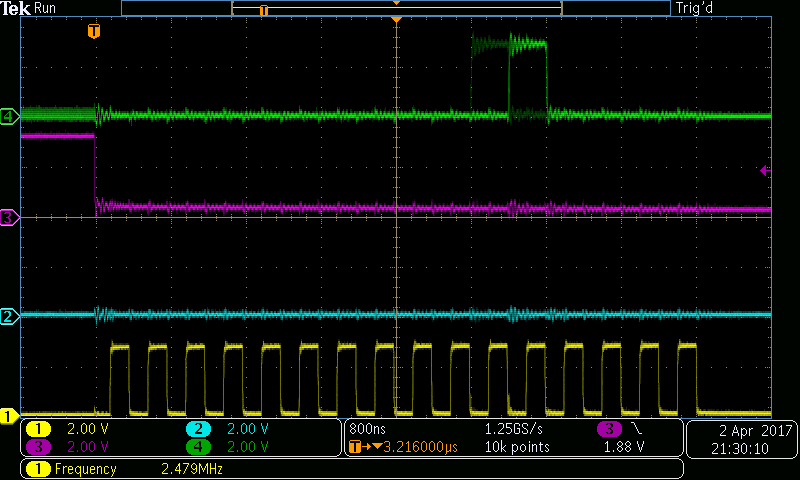

4月28日,星期五。 推出NE555芯片

地点:乌克兰射电乌克兰办事处,乔科洛夫斯基大道,42-A

时间: 17:00-19:00

讲师: Sergey Chenash

- 什么是微电路及其分类

- 电子设备中的信号类型

- 熟悉NE555芯片,创建了一个生成器

- 使用示波器

4月29日,星期六。 奖金焊接

地点:乌克兰射电乌克兰办事处,乔科洛夫斯基大道,42-A

时间: 11:00-12:30

在研讨会上见!

- 乌克兰国立技术大学电子Lampa和学生空间Belka开放实验室“以Igor Sikorsky命名的基辅理工学院”

- 基辅国立塔拉斯·舍甫琴科大学

- 国立大学“基辅-莫哈拉学院”

- 乌克兰小科学院

- LLC“乌克兰的Radiomag”

- 想象技术

研讨会的官方页面,请在

此处进行注册 。