美国奥斯汀的三星半导体工厂

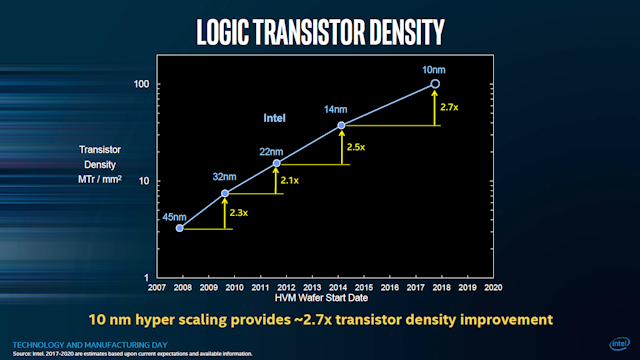

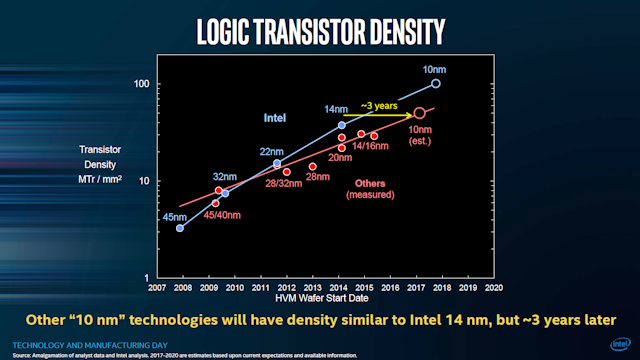

美国奥斯汀的三星半导体工厂从14 nm到10 nm的转变将是历史上晶体管密度最大的技术飞跃。 密度立即增加2.7倍。 因此,摩尔定律将在未来几年继续有效。 AnandTech出版物

收集了有关多家公司计划建设10、7、6和5 nm工艺的新一代工厂计划的信息。

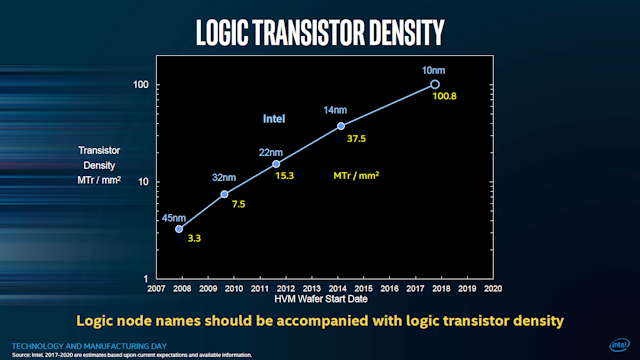

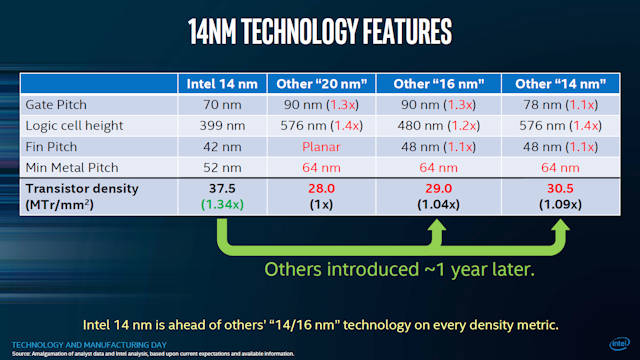

首先应该注意,通过一个晶体管的尺寸来测量晶体管的密度并不是一个完全正确的指标。 例如,英特尔估计其14纳米可以容纳比“其他公司”的14纳米多23%的晶体管。 之所以形成这种差异,是因为逻辑单元的高度较小,门之间的距离更短,肋间距也更小(请参见表)。

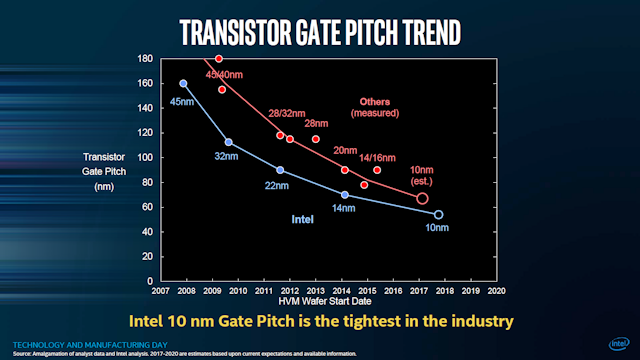

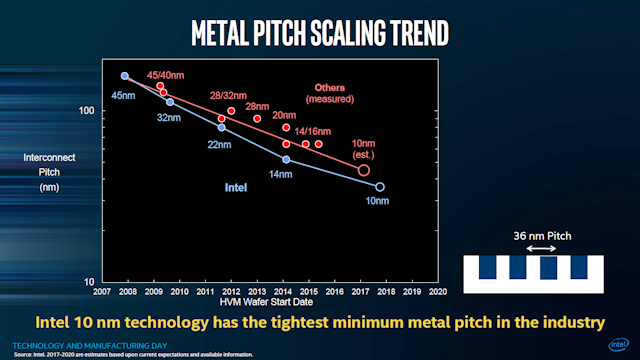

例如,英特尔的栅极间距(栅极间距,即相邻晶体管的栅极之间的距离,包括栅极本身的宽度)要比其他制造商的栅极间距小得多。 在22纳米制程技术上,它与目前竞争对手的14/16 nm大致相同。

就互连间距(互连间距,在线连接各层之间的最小距离)而言,英特尔没有这种基本优势,但竞争对手仍未接近英特尔已经达到14纳米的数字。

因此,“其他工厂”延迟了三年达到晶体管的“英特尔”密度:为此,他们需要实施与英特尔的14纳米相当的10纳米制程技术,然后领导者本人将走得更远。 至少英特尔本身有这样的计划。

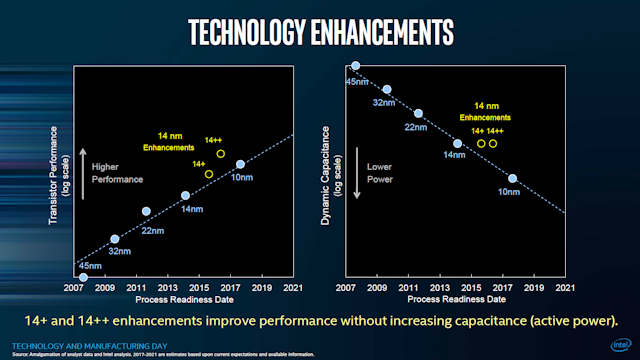

有趣的是,英特尔当前经过多次改进的14 nm ++第三代技术将比前10 nm芯片更好。 公司本身就认识到这一点。 没有什么可做的-新技术仍然需要测试和测试。 也就是说,我们可以等到2020年左右14 nm ++技术的实际改进,而我们只能寄希望于Intel,因为尽管宣布了10和7 nm的计划,但竞争者在技术上仍然落后(同样,我们重复一遍,这是英特尔的话,但实际上竞争对手的技术滞后以及它是否存在尚不清楚)。

实际上,考虑晶体管的密度实际上是更正确的:将微电路的面积除以晶体管的数量。 但是,如果工厂本身尚未开始工作,该如何做。 通过分析公司的计划,只能相互比较建设周期,将一个公司的相同工艺处理速度等同于另一个公司的相同参数:14 nm至14 nm,10 nm至10 nm等。

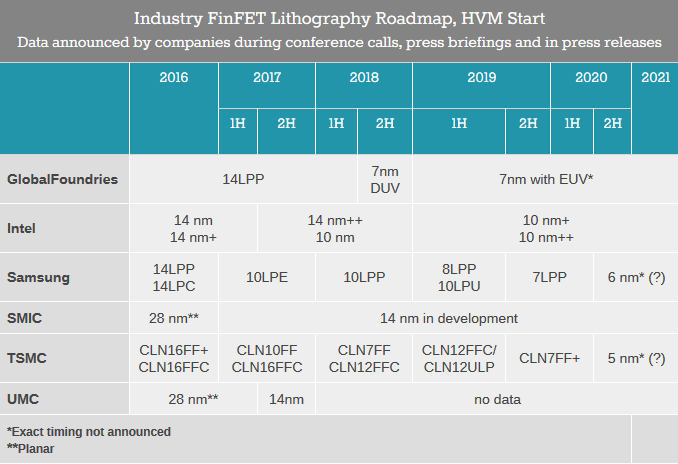

AnandTech已收集了计划投资进行现代化生产和建造新工厂的半导体行业所有主要参与者的信息。 它们是GlobalFoundries(美国),Intel(美国),Samsung(韩国),Semiconductor Manufacturing International Corporation(中国SMIC),Taiwan Semiconductor Manufacturing Company(台湾TSMC)和United Microelectronics(台湾UMC)。 下表总结了他们未来几年的计划。

从表中可以看出,GlobalFoundries将在来年继续制造14LPP制造工艺,但到2018年底它将开始批量生产7 nm芯片。 大规模生产的开始和成品销售的开始是不同的。 这两个事件可以分开进行4-7个月。 首先,GlobalFoundries打算将传统光刻技术与深紫外光(Deep Ultra Violet,DUV)结合使用,后者使用波长为193 nm的光源,然后将转换为波长小于20倍的先进EUV技术(Extreme Ultra Violet)。 在这样的规模下,波长大约是几十个原子,因此EUV从根本上打开了半导体行业的新机遇。

英特尔今年将开始为移动设备发布10纳米芯片,尽管台式机处理器将保持在14纳米。 到今年年底,计划建立第三代14 nm ++的生产。 英特尔是最早投资EUV研究的公司之一,但尚未就此技术的使用发表具体声明。 据了解,英特尔不会使用5nm以下的EUV。

在推出10 nm之后,台积电计划迅速切换到7 nm,而三星则计划在2019年前发布10 nm芯片。 晶体管的密度不仅取决于其尺寸,还取决于技术的完善程度。 三星的10nm可能提供与台积电7nm大致相同的密度。 这里的情况与英特尔的技术优势相同。

三星计划在2019-2020年引入EUV下一代光刻技术,以生产CLN7FF +晶体管。

目前正在进行许多EUV实验,但仍无法确定这种先进技术是否能够行驶。 到目前为止,表中所有公司关于EUV的计划都可以更多地视为“需求”。