前几天,我见了面,并接受了来自

Arduino美国运营副总裁Kathy Giori的简短视频采访。 我们与Katie讨论了已经触动Arduino社区的一种新趋势:由于已经或多或少地学习了借助Arduino进行微控制器编程的知识,因此是时候采取下一步了:教小学生使用该语言来描述Verilog设备和FPGA / FPGA微电路,逻辑矩阵具有可变功能的元素。 而且,为了使FPGA的掌握更加容易,有必要以小规模的集成芯片(在1970年代很流行)作为现代FPGA的前传,重新进行练习。 所有这些将缩小物理与编程,分立元件和微控制器,晶体管和Arduino之间的差距。

可以从任何制造商(Xilinx,Altera,Lattice,Digilent,Terasic)使用FPGA和开发板,我在下面编写的所有内容都与特定公司无关。

斯坦福大学老师Svetlana Khutka参加了与Katya的对话,后者

在来自基辅几所大学的热情教师的帮助下,向Katy讲述了

免费教育学童如何在基辅使用FPGA的

实验 。 之后,我与Katie

在新西伯利亚的年轻程序员暑期学校分享了下一个类似实验的计划,该计划自苏联时代就闻名,并且还与来自Arduino社区的其他同志讨论了FPGA在两所学校和一所硅谷学院的实施情况。

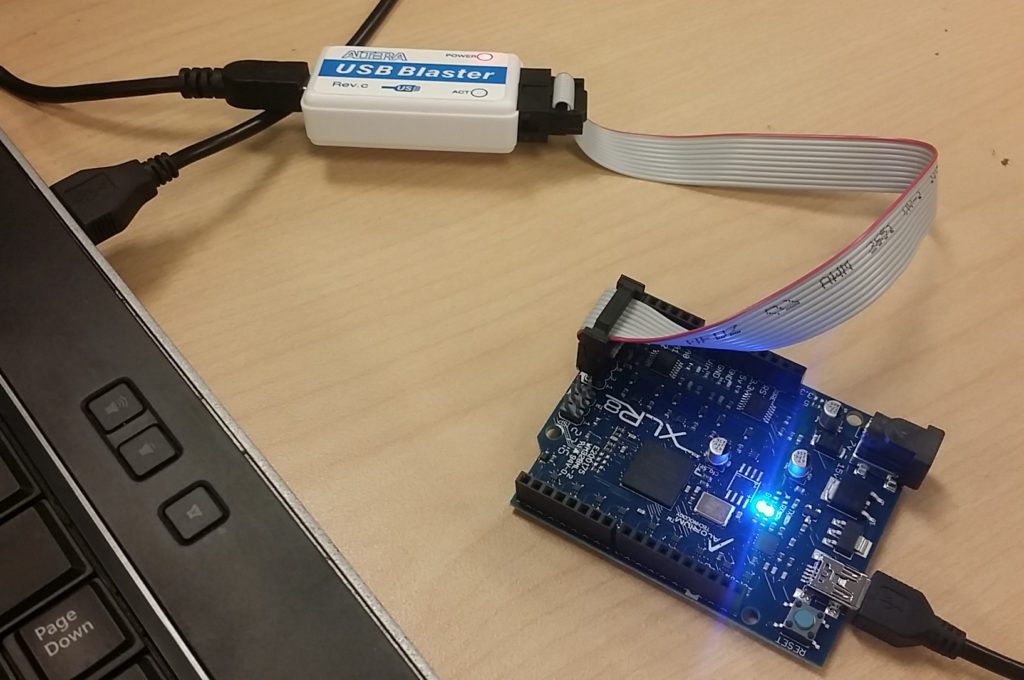

Katya现在建议使用带FPGA的主板,我正在做一些重做以适应我的需要(有关此问题,将另作文章):

下面我将提供有关基辅实验结果的信息,以及激进主义者正在制定的一些未来计划的信息-在基辅,切尔尼戈夫,新西伯利亚,莫斯科,下诺夫哥罗德,萨马拉,圣彼得堡,阿拉木图和其他城市的体育学校和大学的教师。 在基辅研讨会上,与会人员进入了创建密码锁状态机以及与简单外围设备(16键键盘,扬声器)集成的阶段。 在新西伯利亚的暑期学校,我们将有更多的时间,我们将尝试与学生一起建立处理器。 将来,计划在体育学校开设关于FPGA上数字电子基础知识的年度课程,这可以丰富学校教育,因为在1980年代,由于引入了编程元素而使课程变得更加丰富。

我们将对此进行详细讨论:

1.为什么要教小学生如何描述硬件以及如何使用FPGA? 程序的合理性。在以学校教育为代表的世界图中,在物理和程序设计之间的数字电子设计原理领域存在一个“盲点”。 机器人技术和arduino的课程并没有解决这个盲点,因为它们只能归结为对现成的芯片进行编程。 尽管可以有效地介绍基本原理,但使用离散程度很小的集成度很小的电路和微电路进行的练习是基于1960-1970年代的技术,与现代设计没有任何联系。 盲点可以通过引入可用于学校实验的硬件描述语言(NLA)和FPGA(可编程逻辑集成电路)芯片(可重配置逻辑元素矩阵)来封闭。 因此,世界的情况变得不可或缺,并为创建一个年轻的工程师创造了一个环境,这些工程师对现代微电路的各个方面都有自己的见解,例如无人驾驶汽车,并且能够在将来专门设计此类设备的一个或另一个方面。

将NLA和FPGA引入学校课程也与物理和数学学校的数学和物理课程紧密相关-布尔代数,算术方案,有限状态机。

请注意,尽管与编程表面上相似,但NLA和FPGA使用其他基本概念:

编程:顺序执行,选择分支,循环,变量,表达式,数组(使用平面可寻址内存模型),函数(基于堆栈的使用),递归。

数字逻辑设计:组合逻辑元件; 从这些云元素中构建组合逻辑,包括使用多路复用器的选择原语以及用于实现算术表达式的模块; 用于同步计算和重复的时钟信号的概念;用于存储小节之间的当前状态的D触发器的概念; 状态机 并行操作,模块层次结构,流水线的概念(不仅适用于处理器,还适用于算术单元)。

2.此类课程的总体计划:

2.此类课程的总体计划:第1节。与物理的联系,以及分立组件上的实验室。

第2节。数字逻辑和算术的基础知识,以及集成度较小的实验室微电路。

第3节。基于硬件描述语言的综合设计电路,并在Xilinx或Altera FPGA上进行实验室设计。

第4节。处理器体系结构:从程序员的角度出发,在实验室使用RISC处理器模拟器进行教学,例如MARS MIPS。

第5章微体系结构:构建处理器。

单个项目:将传感器或其他外围设备与FPGA中实现的电路集成在一起。

3.基辅实验的结果。

3.基辅实验的结果。由基辅理工学院的叶夫根尼·科罗特基(Yevgeny Korotky)的老师撰写了

详细的基辅实验结果文字。 我将以我的个人结论作为补充。 背景-Habré和Geektimes上的帖子-1,2,3,4)。 在这些帖子中,有人提出了问题。 答案如下:

小学生可以使用Verilog的假设已得到确认

事实证明,Verilog对足够多的学生也很有趣(直到基辅,一些同事对此表示怀疑,认为孩子们对诸如带微控制器的机械臂这样的项目更感兴趣)

在使用Verilog之前,有必要在小集成度的微电路上显示学童的逻辑元件和D触发器,这种想法不仅有用,而且得到了更多的证明。

总体而言,在经历了一天的练习后,一些学生开始提出一些可理解的问题-例如,何时使用阻止和何时使用非阻止作业。

让学童从零开始一周之内就可以实现像SPI这样的协议的状态机,但是又可以带一个代码锁或交通信号灯的状态机,这显然是不现实的。

花费一周的时间来设计处理器也是不现实的,但是我们将在新西伯利亚尝试在两周内完成。

在基辅实验期间,我们尝试谈论FPGA和嵌入式处理器(MediaTek MT7688,就性能而言,它位于Arduino和Intel Galileo或Rasbery Pye之间的中间位置)。 然后,我们在基辅-莫哈拉学院(Kiev-Mohyla Academy)举办了一次黑客马拉松,观察了多少学生选择了黑客马拉松的FPGA项目,以及有多少个集成处理器的项目。 原来是50到50。有趣的是,在黑客马拉松之前,我不知道崩溃会发生什么。

我担心小学生可能会对Xilinx Vivado中的用户界面以及大量的选项和界面元素感到困惑。 但是事实证明,学生并不在乎-复杂的GUI并没有吓到他们。

大多数学生使用Windows。 与我的同事Alexander Belits一起,我有一个主意,就是为这样的事件做准备,准备了几十个带有Linux(Ubuntu或CentOS)的可引导SSD驱动器,并在每个事件之间使用它们。 Alex甚至编写了一个脚本来克隆此类驱动器。 Ubuntu更为友好,但FPGA电路设计自动化工具(尤其是Xilinx Vivado和Altera Quartus)更正式地支持CentOS。 在夏令营期间,可以同时制作Linux教育程序和Verilog / FPGA教育程序吗? 尚不清楚,但可以尝试。

事实证明,如果您使用廉价的,屏蔽不良的micro-USB电缆,则Xilinx Vivado在配置Artix-7 FPGA时会毫不留情地进行故障检查。 一次神秘的涌入,在去基辅之前,我在手提箱里放了十几根高质量的绳索,这节省了研讨会的时间。

我的想法是,使用Digiboard Cmod A7 35T等可面包板上的FPGA模块(粘贴在面包板上的FPGA板)可以使学生更轻松地从使用小型集成芯片的练习转换为使用FPGA的练习。 这个想法是否正确,我听不懂。 也许使用带有丰富外围设备的大型主板,例如Terasic DE10-Lite ,不会更糟。 无论如何,当从低集成度的微电路(CMOS 4000或74HC)切换到FPGA时-您需要更改电源电压(从9 V或5 V更改为3.3 V),因此您不能将Cmod A7粘在同一面包板上,而不是说CMOD 4013带有指示灯和按钮,并希望一切都会继续进行。

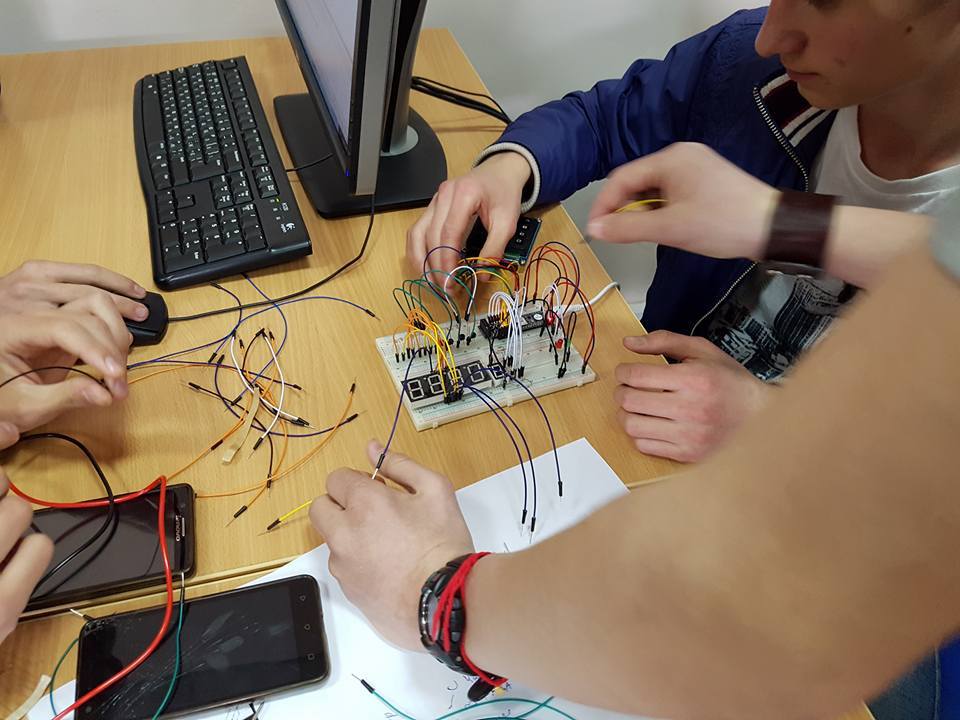

我证实了自己的观察,为了进行短期(1周)的教育活动,至关重要的是,要有来自当地大学的学生团队来指导学童。 在基辅案件中,由基辅理工学院的尤金·科罗特基 ( Eugene Korotky)的老师提供了这样的团队。

在什么情况下以及在什么程度上值得在这种事件的程序中包括与晶体管的电平和微电路的制造有关的部分,已经变得或多或少地变得清楚了。 这部分内容由基辅国立大学副教授亚历山大·巴拉巴诺夫 ( Alexander Barabanov)教授,该课程是面向学生的“ 纳米ASIC ”课程的材料翻译。 显然,这些材料应该以一年级的形式完全包含在学童的年度课程中,以夏令营的形式,在为期两周的课程中,但是持续时间少于一周,您应该立即进行小积分的微电路(在开始后1小时内)。 (例如CMOS 4000)并提及晶体管,其形式为“如果C中的电压C为1(或0),则晶体管是电流从A点流向B点的器件。 从晶体管可以构建逻辑元件AND,OR,NOT(如图所示)。”

在大量观众面前的演讲中,可以向学生展示集成度低的微电路组装在面包板上的电路。 这是直观的,引起了人们的兴趣,并且不需要将设计连接到计算机-仅使用9 V电池。我展示了其中三个对于理解至关重要的电路-XOR逻辑元件,频率为1赫兹的4位组合D触发器加法器(即每秒测量一次)。

是否有可能向学生传授流水线的想法仍然是个问题,流水线的想法是数字设计和一般计算组织中最强大的想法之一。 为此,不需要构建输送机处理器;您可以制造输送机算术设备 。 也许这可以在课程的最后提到,当孩子们通过简单的组合和顺序电路以及状态机玩够了。 对于一小部分小学生来说,这很有可能会很有趣,但是值得一试。

对于更真实的事件,您可以使用单个项目和验证工作 。

GitHub上用于基辅活动的代码 4.今后编写材料的信息来源。

4.今后编写材料的信息来源。在对乌克兰,俄罗斯和硅谷的学生进行初步实验后,体育学校教师的信息源很可能会开发大多数详细材料:

大卫·哈里斯(David Harris)和莎拉·哈里斯(Sarah Harris)的教科书“数字电路和计算机体系结构”,第二版,俄语翻译。 该教科书可以免费下载,请参阅有关Habré的文章-1、2、3。 最近,还发布了具有改进的彩色打印功能的新纸版 。

除教科书《 Harris&Harris》外,还为教师提供幻灯片。 免费下载。

从NAND到俄罗斯方块课程的资料,该课程在以色列创建,并在美国的一些大学中介绍。 同时,恕我直言,该课程应使用思想和框架,但应在“成人”设计工具的子集上进行实施,而不是像课程那样在人工“孩子”工具上进行。 关键部件是免费下载的。

查尔斯·彼得佐德(Charles Petzold)的书《密码》(Code),充分解释了手指上的许多概念,并且其水平与学校水平相对应(该想法由基辅ORT学校谢尔盖·德祖巴的老师提出)。 同样,从我的角度来看,值得使用书中的思想和构架,但是大多数材料应替换为更正确的材料(而不是使用锁存器(D-latch),使用D触发器(D-flip-flop))和例如代替累加器的现代方法。基于6800和过时的8080使用RISC体系结构的子集。

来自美国公司ETron Circuit Labs,俄罗斯公司Cyberfizika,乌克兰公司Radiomag的基于离散化组件和集成度较小的微电路在面包板上构造电路的套件(如果您有兴趣的话,我可以在评论中解释这些套件之间的差异)。

FPGA制造商(Xilinx,Altera)和带有FPGA的教学卡(Digilent,Terasic)的材料。

由Anton Moiseev,Yuri Panchul,Eugene Korotkiy,Alexander Barabanov和其他公司工程师和大学教授针对加利福尼亚,哈萨克斯坦,俄罗斯和乌克兰的各种活动开发的代码示例,测试和项目建议。

5.未来问题的计划1. 35学时的年度课程格式,以学年为单位,每周一小时

5.未来问题的计划1. 35学时的年度课程格式,以学年为单位,每周一小时从物理到离散元素

什么是电流,电压和电阻。 面包板如何工作? 练习:第一个电路由电池,LED和电阻组成。 为什么要用LED将电阻器连接到电路上。 读取电阻器标签。 可变电阻,光敏电阻。

什么是晶体管? 从继电器,无线电管,分立晶体管到微电路晶体管的开关元件概述。 使用晶闸管(SCR-可控硅整流器-比晶体管更清楚),双极pnp和npn晶体管进行练习。

验证工作。

从离散元素到组合逻辑

布尔代数和逻辑代数。 运算,表达,公理和身份,包括de Morgan法律。 真相表。

组合逻辑元素AND,OR,NOT,AND-NOT,OR-NOT,异或(AND,OR,NOT,NAND,NOR,XOR)。 晶体管如何构成组合元件。 练习:从离散元素构建AND,NAND或NOR。

集成度很小的微电路中的逻辑元素。 个性化练习:每个学生都将得到CMOS 4000系列的个人逻辑芯片,带有制造商的技术说明,其任务是绘制真值表,演示其工作并口头描述该功能。 芯片包含逻辑元素AND,OR,XOR,NOR,NAND,具有不同数量的输入。 什么是上拉电阻,为什么需要它们。 在上一个练习中添加按钮和上拉电阻。

验证工作。

二进制算术及其实现

二进制数 从二进制转换为十进制,反之亦然。 加法和乘法运算。 负数和其他代码。

使用逻辑元素实现半加法器和全加法器。 迁徙 具有顺序进位的多位加法器。 在面包板上锻炼。 提到了长时间的延迟以及具有最佳延迟的方案。

使用4位全加法器CMOD4008。从中构建8位加法器和减法方案。 面向高级学生的作业:学习并介绍如何通过快速的小组转移来实现快速加法器。

验证工作。

顺序逻辑

基于芯片555构建时钟发生器。研究电容器和电阻对高低电平的频率和持续时间的影响。

由于捆扎带555中包括电容器,因此可能需要关于什么是电容器,捆扎带555中为何需要它们以及如何标注电容器的附加说明。 带有不同容量的充电和放电电容器的辅助练习也可能会有用。

具有内部状态的方案。 从“与非”门构建RS锁存器。 D- CMOS 4013 555 1 .

— (CMOS 4029) (4015). 4511. .

.

—

( ) — . Verilog, , , . : .

Verilog. , , . Always- . : , .

Verilog. . : . : .

Verilog . / . . : , Verilog. Icarus Verilog GTKWave .

: , ( ).

Verilog

Verilog, D- . : always-. Icarus Verilog.

: D-, . . : .

. . : .

. ( ) c . : , : , .

. , .

.

: , RISC- , MARS MIPS .

- . : , , , . . . — MARS MIPS. .

, , . : . .

. . . : , . .

.

:

Verilog MIPS , , . , , . . .

9.1

6. 2.

6. 2., .

, . . .

. CMOS 4000, , , . AND, OR, XOR, NOR, NAND . , .

2 , .

4- CMOD 4008.

8- 4-.

-a == ~ a + 1

555. .

D- CMOS 4013 555 1 .

“ ” CMOS 4015.

(CMOS 4029) 4511.

( ) — . Verilog, , , . Verilog, , . Always- .

.

, .

Verilog. . Verilog . / . .

: .

, Verilog. Icarus Verilog , GTKWave .

Verilog. Verilog, D- . : always-. Icarus Verilog. .

.

.

.

2 3 .

. . . ( ) c .

“ ”.

.

.

: . - . MARS MIPS .

: , , , . . . .

, , . .

. . . , . .

: .

Verilog MIPS , , . , , . . .

.

附录A。什么是Verilog硬件描述语言,以及它与微电路设计之间的关系,摘自Geektimes Microelectronics Scammers上的一篇文章。旧金山电子设计会议的视频报告。

附录A。什么是Verilog硬件描述语言,以及它与微电路设计之间的关系,摘自Geektimes Microelectronics Scammers上的一篇文章。旧金山电子设计会议的视频报告。25 Verilog ( — VHDL), (logic synthesis) , (static timing analysis) , , (place-and-route) .

: , , , , static timing analysis, floorplanning, place-n-route, parasitics extraction .. — GDSII, , . Taiwan Semiconductor Manufacturing Company TSMC.

附录B.什么是FPGA / FPGA以及为什么不能通过对Arduino或Rasberry Pye的更深入研究来代替对FPGA的研究。选自Habr。如何开始使用FPGA开发铁-逐步说明:

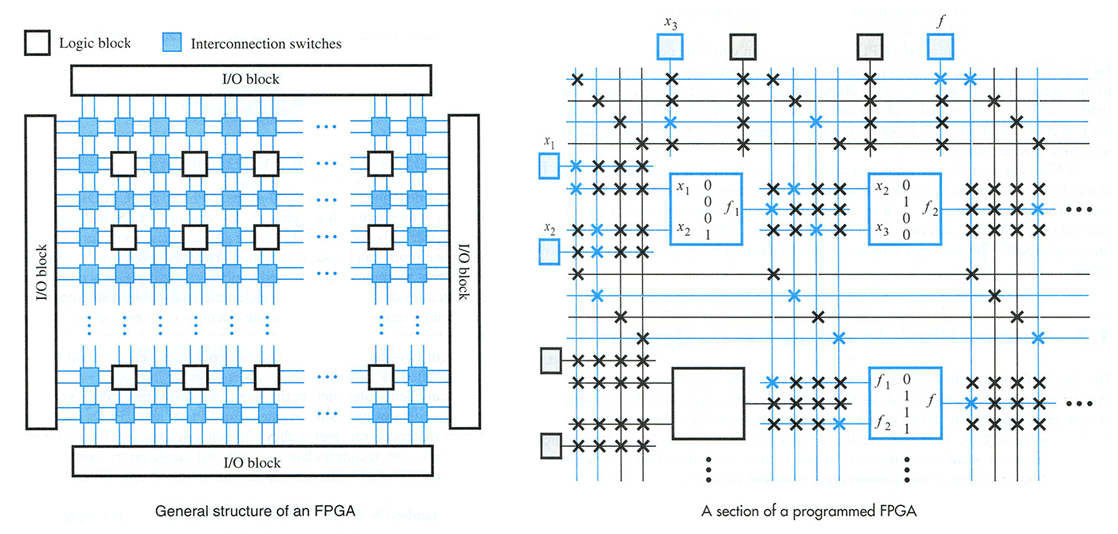

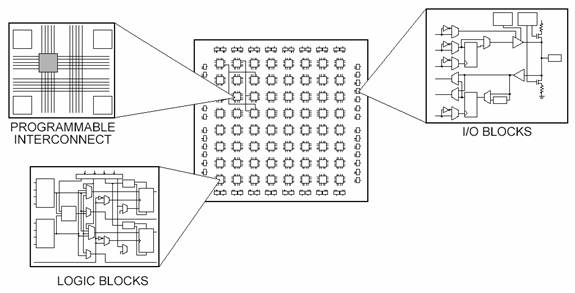

附录B.什么是FPGA / FPGA以及为什么不能通过对Arduino或Rasberry Pye的更深入研究来代替对FPGA的研究。选自Habr。如何开始使用FPGA开发铁-逐步说明:FPGA , , . AND , — .. — FPGA , , ..

- / FPGA — , «» ( -) (), ( ) ().

— FPGA, look-up table (LUT) flip-flop. , , .

, FPGA:

:

C. ,

C. ,(system on chip, SoC), IP- (CPU, GPU, DSP) — , . ADAS (advanced driver-assistance systems) .

, , , ( 1980- — 1990- ). (hardware description languages — HDL), (register transfer level — RTL), RTL-to-GDSII, Verilog VHDL , FPGA (field-programmable gate arrays). , -, -. HDL RTL , , , , 1980- .

除了在托木斯克举行的会议以及计划在7月举行的下一个实验以及新西伯利亚青年程序员暑期班支持的新西伯利亚外,还有一个较早的计划在哈萨克斯坦组织这样的实验(这对维纳斯·扎纳利纳(Venus Zhanalina)参加基辅研讨会特别感兴趣)。 附录D.简单Verilog代码示例以及由其生成的方案

附录D.简单Verilog代码示例以及由其生成的方案module adder

(

input a,

input b,

input carry_in,

output reg sum,

output reg carry_out

);

reg p, q;

always @*

begin

p = a ^ b;

q = a & b;

sum = p ^ carry_in;

carry_out = q | (p & carry_in);

end

endmodule

module counter

(

input clock,

input resetn,

input load,

input [15:0] load_data,

output reg [15:0] count

);

always @ (posedge clock or negedge resetn)

begin

if (! resetn)

count <= 0;

else if (load)

count <= load_data;

else

count <= count + 1;

end

endmodule

它

它 是如何工作的:在文本“针对从未使用过此技术的程序员介绍Harver芯片组的设计简介”中有详细的解释。如果您是老师,并且想参与此类材料的开发(全部是自愿的,无需与特定公司进行交流),请在评论中告知我。任何批评也很有趣。

是如何工作的:在文本“针对从未使用过此技术的程序员介绍Harver芯片组的设计简介”中有详细的解释。如果您是老师,并且想参与此类材料的开发(全部是自愿的,无需与特定公司进行交流),请在评论中告知我。任何批评也很有趣。