前言

我很高兴详细介绍我的第一个集成电路,并分享我在过去一年中从事的这个项目的曲折。 我希望我的成功能够激励其他人,并帮助掀起家用芯片生产的一场革命。 当我开始这个项目时,我不知道自己参与了什么,但是最终我学到了比物理,化学,光学,电子和许多其他领域更多的知识。

此外,我的努力仅伴随着来自世界各地的最积极的评价和支持。 我衷心感谢所有为我提供帮助,提出建议和受到启发的人。 特别是对我那些了不起的父母来说,他们不仅总是会尽快支持和鼓励我,而且还提供了一个工作场所并承担了电费……谢谢!

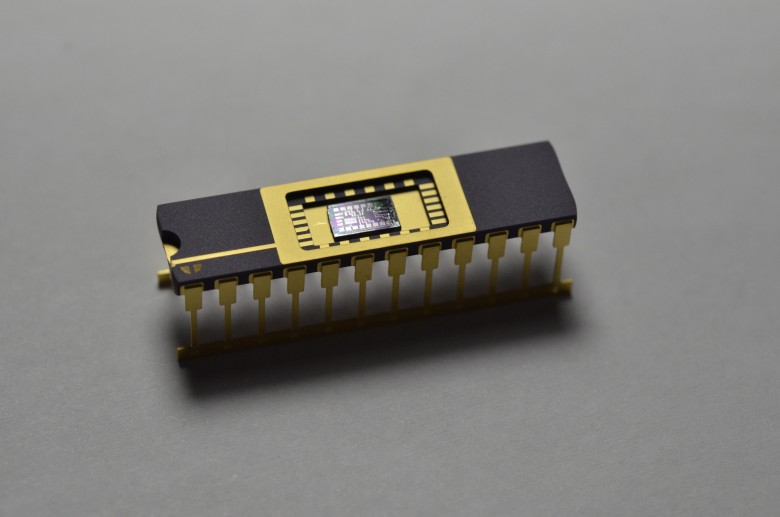

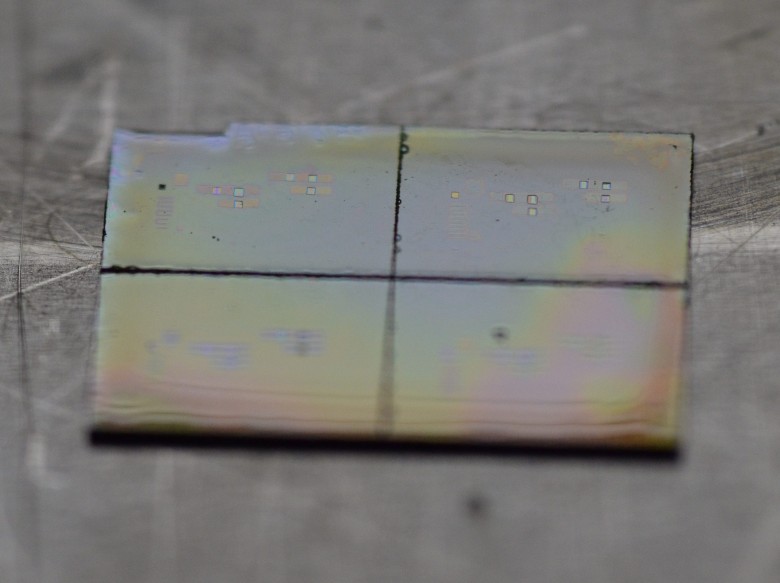

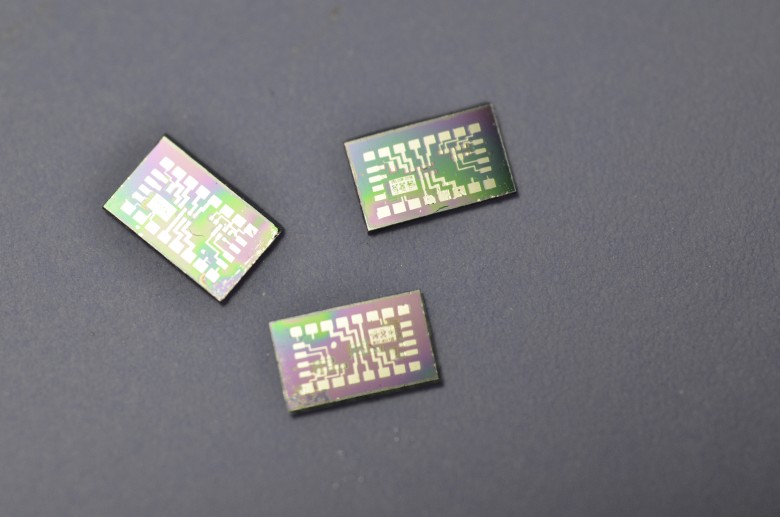

事不宜迟,我介绍了在家庭(车库)条件下通过光刻方法制造的第一个集成电路(IC)-Z1双差分放大器的PMOS芯片。

我之所以说“用光刻法制造”,是因为杰里·埃尔斯沃思(Jerry Ellsworth)制造了第一批晶体管和逻辑门(其连接由手工导电环氧树脂精心铺设),并向世界展示了这是可能的。 受她工作的启发,我介绍了由可扩展的标准光刻工艺创建的集成电路。 不用说,与我以前的工作相比,这是合乎逻辑的进步,在我以前的工作中,我

复制了杰里场效应晶体管 。

设计方案

我在寻找一种简单的芯片来测试和调整过程时

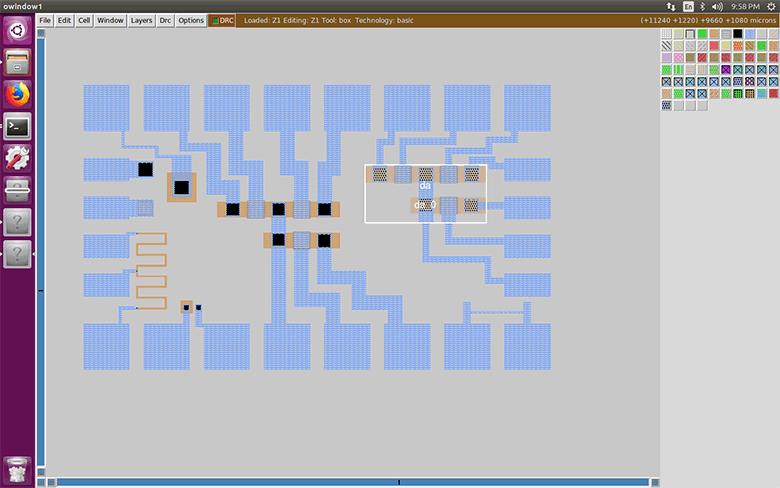

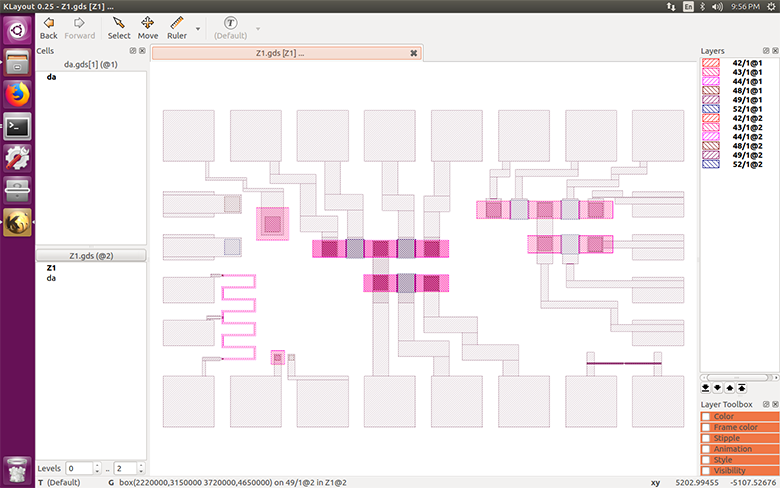

开发了Z1放大器 。 该布局是在

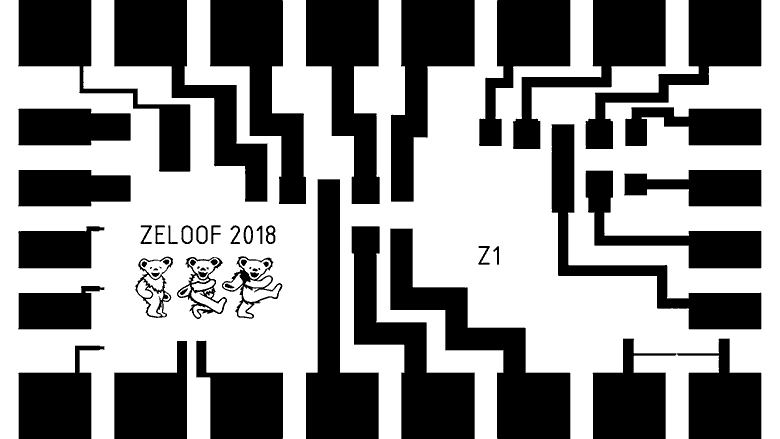

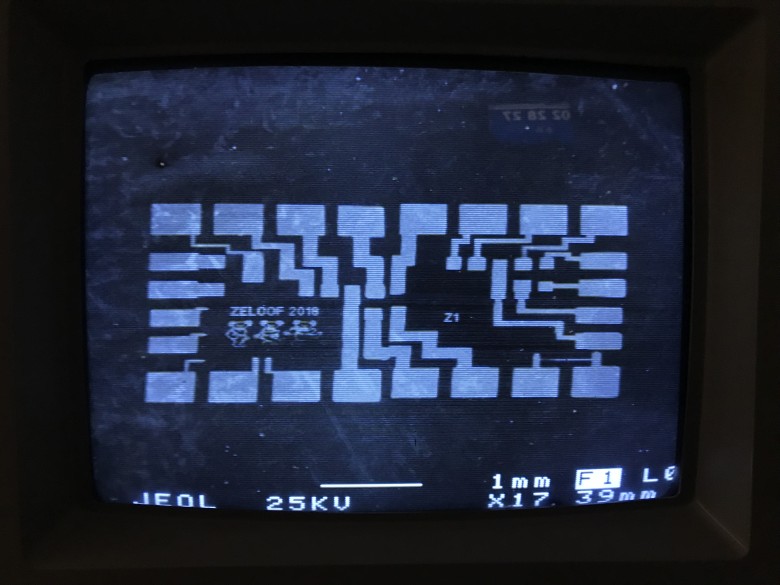

Magic VLSI中为PMOS工艺制成的,具有四个掩模(有源/掺杂区,栅氧化层,接触窗和顶部金属层)。 当考虑由于在车库中制造而导致的离子杂质时,PMOS优于NMOS。 蒙版的宽高比为16:9,以简化投影。

魔术VLSI布局

魔术VLSI布局 面膜生成

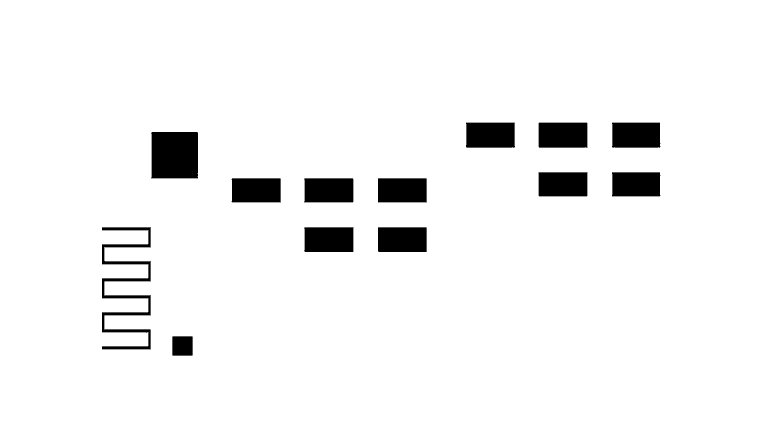

面膜生成 活动区域

活动区域 百叶窗

百叶窗 联络方式

联络方式 金属制品

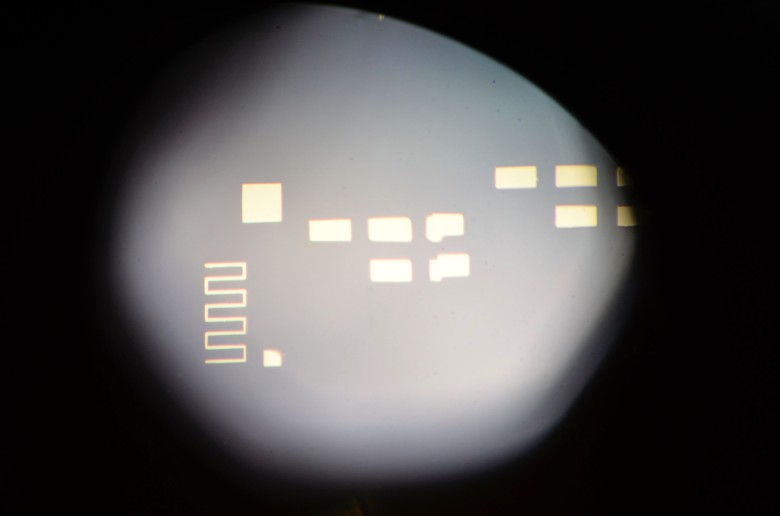

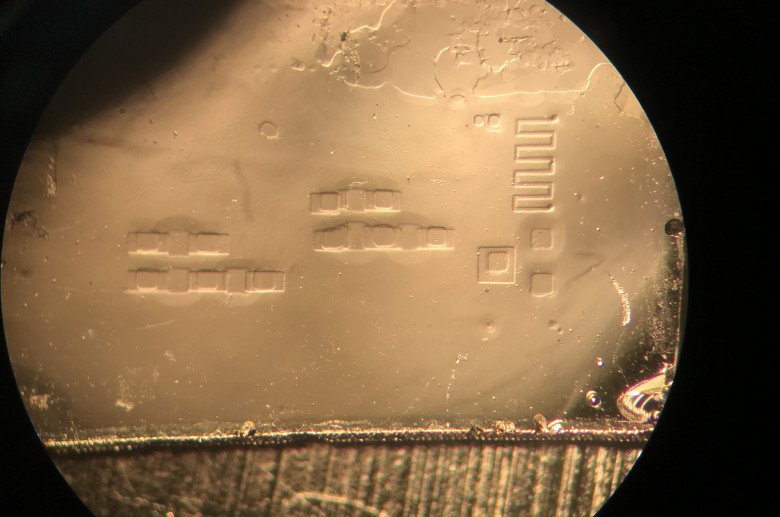

金属制品快门尺寸约为175微米,尽管在芯片上制作了尺寸最大为2微米的元件用于验证。 每个放大器部分(中央和右侧)包含三个晶体管(两个用于

具有公共阴极电阻的推挽电路,另一个作为电流源/负载电阻器),这意味着每个IC总共六个晶体管。 左侧的电阻器,电容器,二极管等测试元件用于研究过程特性。 差分对的每个节点在输出框架上都有单独的引脚,因此可以对其进行研究,并在必要时添加一个外部偏移。

制造业

制造过程包括66个单独的步骤,大约需要12个小时。 大型产品的收率达到80%,但在很大程度上取决于您在特定日期喝的咖啡量。 我还在YouTube上录制了一段有关

微电路生产理论以及

分别制造MOS晶体管的视频 。

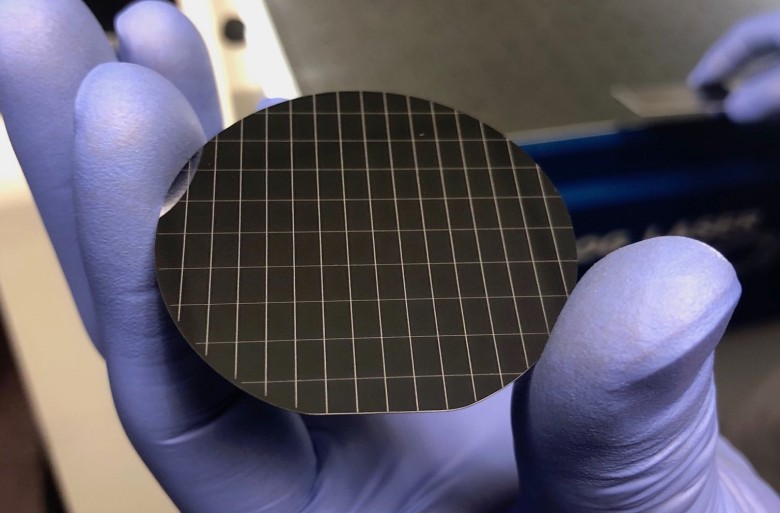

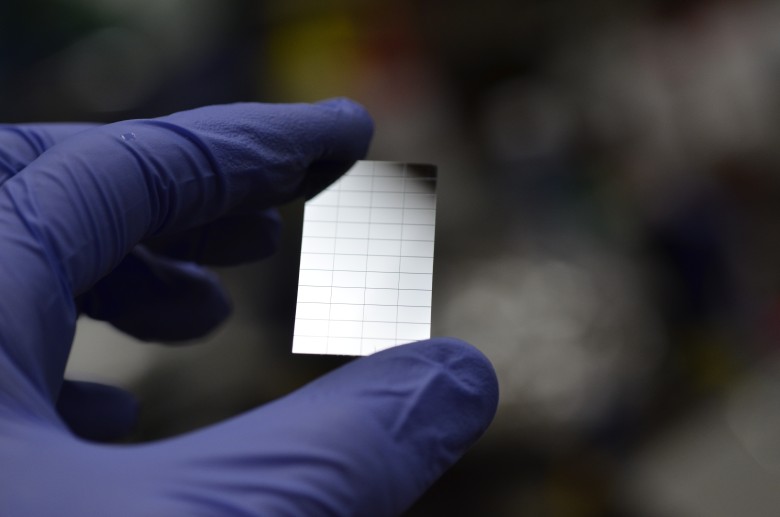

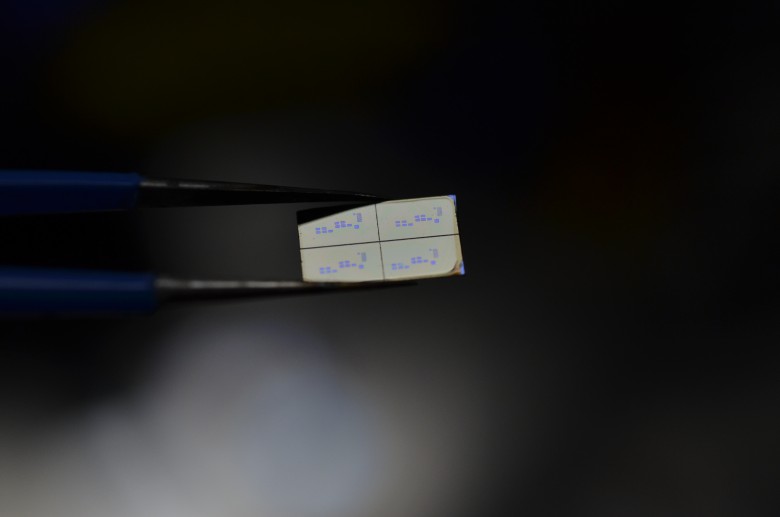

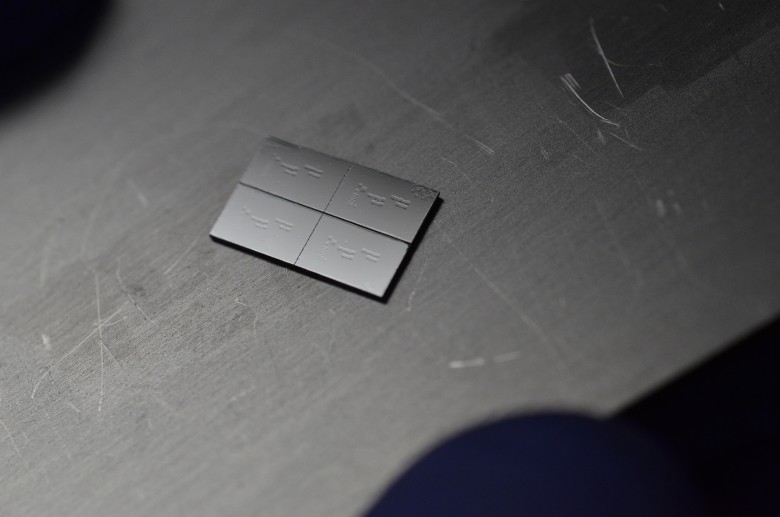

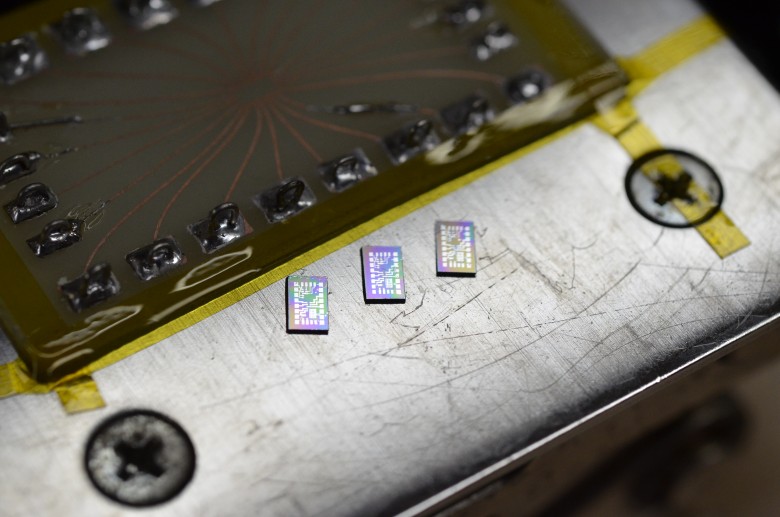

使用Epilog光纤激光器将50毫米(2英寸)的硅晶片破碎成5.08 x 3.175毫米的晶体(面积约16平方毫米)。选择晶体的大小以适合Kyocera 24针DIP封装。

N型板50毫米

N型板50毫米 N型板50毫米

N型板50毫米首先,通过快速浸入稀释的氟化氢中,然后用食人鱼蚀刻混合物(硫酸和过氧化氢的混合物),RCA 1的混合物(水,氨,过氧化氢),RCA 2的混合物(水,盐酸,过氧化氢)并反复浸入氟化氢中。

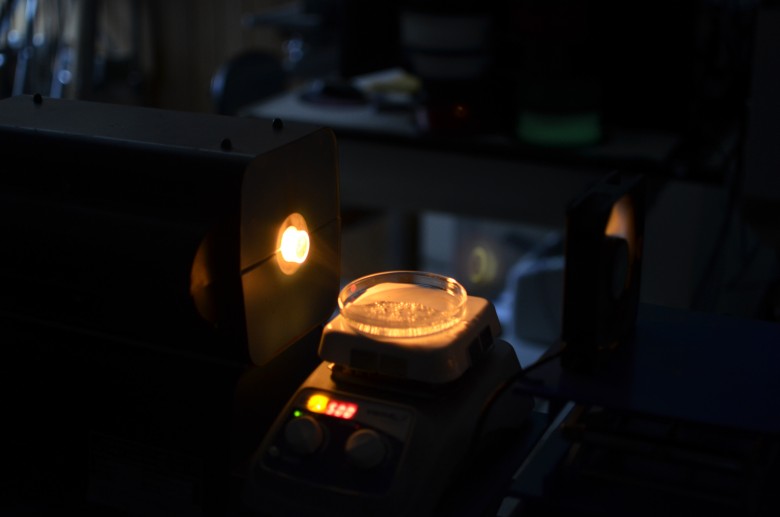

保护性氧化物在环境空气的水蒸气中

热生长 (湿氧化),厚度达到5000-8000Å。

湿热氧化

湿热氧化 湿热氧化

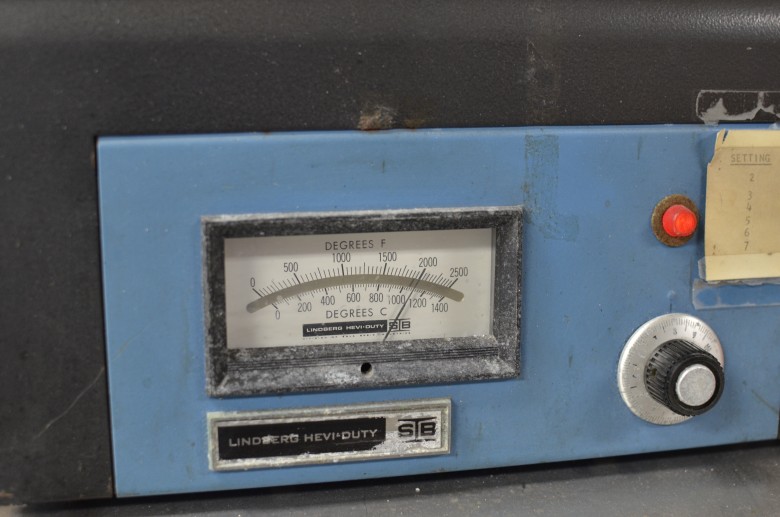

湿热氧化 管式炉

管式炉 氧化板

氧化板准备在有源/掺杂(P型)区域形成氧化板。 将

AZ4210光致抗蚀剂施加到以大约3000 rpm旋转的

乳房上,形成大约3.5微米厚的膜,然后在90°C的电炉上轻轻干燥。

光刻工艺详细核心掩模是由我的

光刻步进机Mark IV在紫外线下以365 nm的步长进行处理的,其结构是在氢氧化钾溶液中制成的。

抵抗结构

抵抗结构 抵抗结构

抵抗结构 30分钟干燥

30分钟干燥 核心蚀刻

核心蚀刻此后,固化抗蚀剂结构,并使用

其他一些技巧来确保在下一次用氟化氢蚀刻期间确保良好的附着力和耐化学性,从而将这种结构转移到栅氧化层,并向裸露的硅打开窗口以进行掺杂。 这些区域随后将成为晶体管的源极和漏极。

粒子关闭百叶窗

粒子关闭百叶窗 蚀刻栅极的合金晶体

蚀刻栅极的合金晶体此后,进行合金化,即从固体或液体源引入杂质。 作为固体源,使用氮化硼圆盘,该圆盘位于管式炉中,距板较近(小于2 mm)。 或者,您可以在水中或溶剂中制备磷酸或硼酸的液体源,然后根据

预涂/浸入氟化氢/扩散/去除釉中的标准过程进行掺杂。

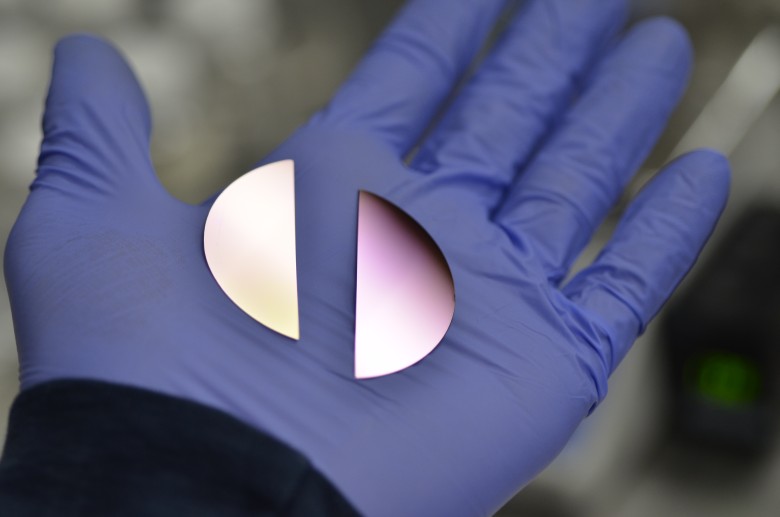

然后对栅极氧化物和接触层重复上述图案化步骤两次。 栅极氧化物应比保护性氧化物薄得多(小于750Å),因此要蚀刻漏极/源极之间的区域-并在那里生长更薄的氧化物。 然后,由于整个板在掺杂步骤被氧化,因此必须蚀刻接触窗以建立金属层与掺杂的源极/漏极区的接触。

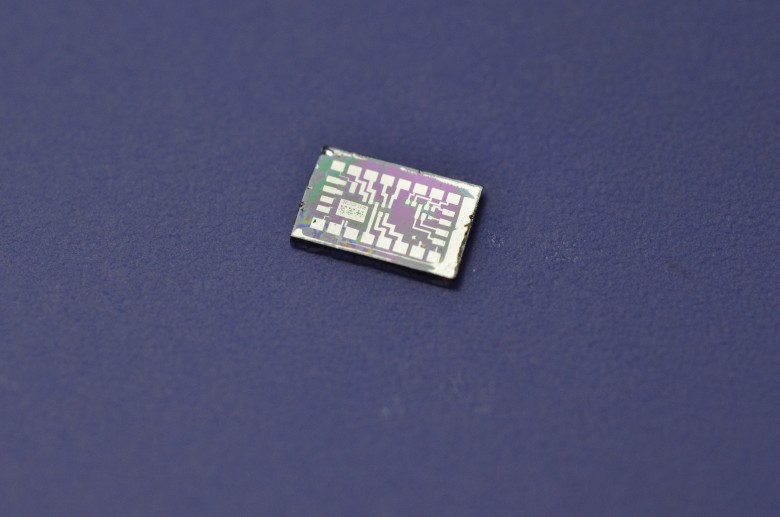

现在,所有晶体管均已形成,并可以通过访问输出帧进行互连。 将铝的保护层(400-500 nm)

喷涂或

热喷涂到板上。 另一种方法是剥离工艺,首先形成光刻胶,然后沉积金属。

喷涂金属

喷涂金属 喷涂金属

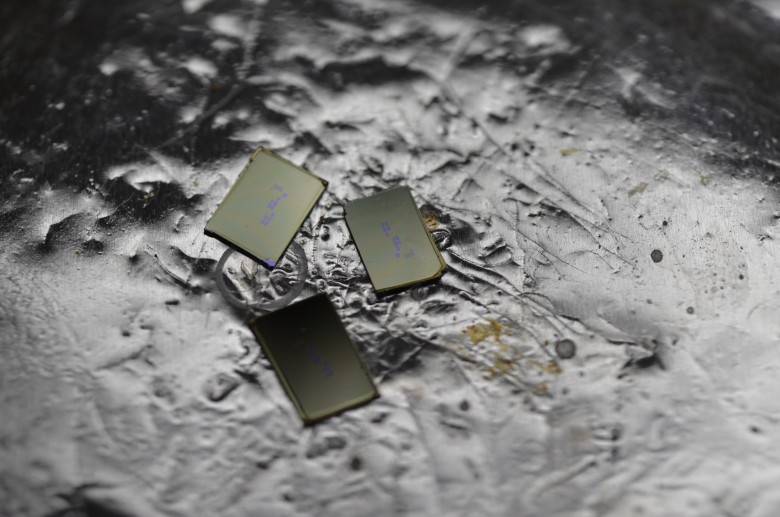

喷涂金属然后,在金属层上形成光刻图案,并在热磷酸中进行蚀刻,以完成集成电路的制造。 测试之前的最后步骤是目视检查和铝的高温退火以形成欧姆结。

该芯片现已准备好进行封装和测试。

我没有安装微焊接机(我接受捐赠!),所以现在的测试过程仅限于用锋利的镊子触碰平板,或者使用倒装芯片板(难以对准)并连接到字符表。 还在电路中对差分放大器进行了经验测试,以验证其可操作性。

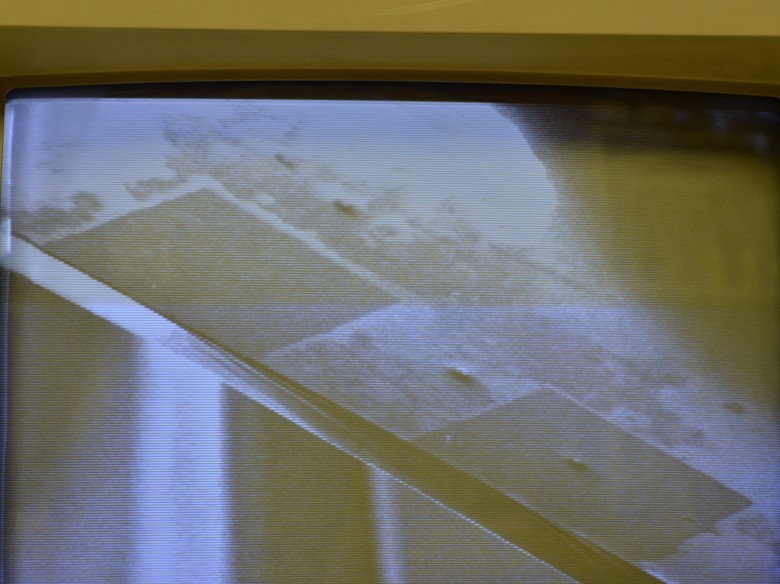

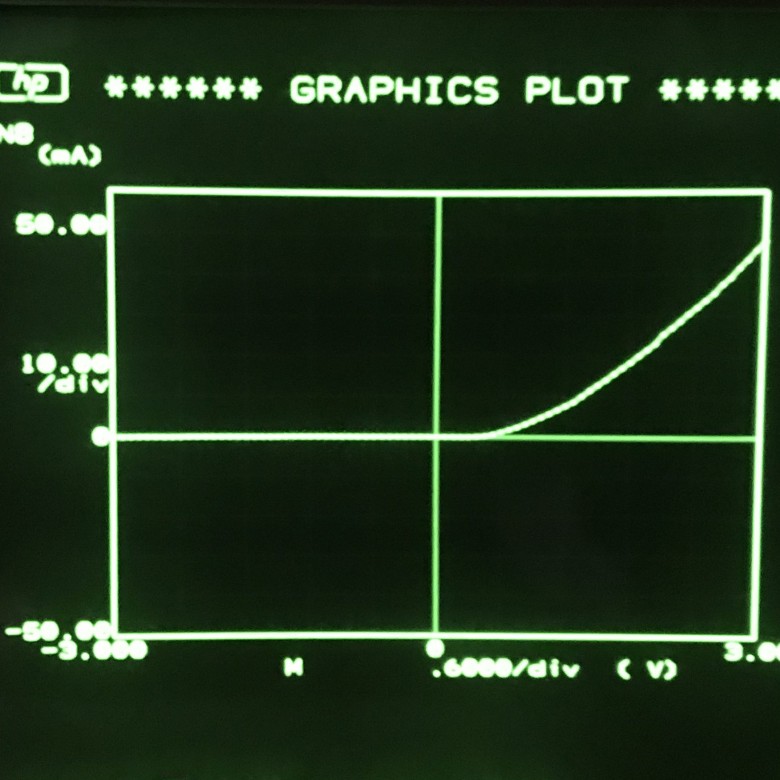

曲线IV

曲线IV 曲线IV先前NMOS器件的FET Ids / Vds曲线

曲线IV先前NMOS器件的FET Ids / Vds曲线当然,这些曲线远非理想的(包括由于过大的接触电阻和其他类似因素引起的),但是如果安装了微焊接,我希望性能得到改善。 这可能部分解释了晶体之间的某些差异。 很快我将在

此页面上添加新的IV曲线,晶体管和差分放大器特性。