在每一篇专门针对家用微处理器的有关哈布雷的文章中,都提出了许可的IP块的问题,以及它们的存在与否会降低开发的价值,实用性或安全性。 同时,许多评论员对讨论的主题不太了解,所以让我们尝试确切地弄清楚许可在微电子行业的工作原理,许可的好坏块是什么以及如果购买了大多数块,开发微电路的过程是什么?

任何现代微电路在一段时间前都被自豪地称为“片上系统”:即使是三足的线性稳压器和电压源也对用户隐藏了数字调节功能,对于包含数十个不同模块的微处理器和微控制器,我们能说什么呢?其中需要特定的技能和丰富的经验来规避书籍和文章中未提及的陷阱。 此外,任何项目通常都具有自己的杀手级功能,因此开发人员希望获得比竞争对手更多的优势,应该尽可能地做到这一杀手级功能,而所有其他功能块都不应比其他功能差。

注意,问题是:是否有必要维持一支昂贵的开发团队,该团队可以独立地独立完成所有必要的工作?

一个甚至更有趣的问题:如果您自己开发了微处理器指令系统,您是否需要一个程序员团队来

为其编写一个编译器 ,移植流行的操作系统的新内核,进行许多其他艰苦的工作,而且很可能不会将您的创作放在一个与流行的体系结构保持一致,哪些人在其中工作?

而且最重要的是:前两个问题的肯定答案会为您的产品带来竞争优势吗?

抒情离题6月5日,莫里斯·张(Morris Chang)退休,这是一个您从未听说过的人,但没有他,就不会有现代电子产品。 莫里斯·张(Morris Chang)出生于中国,在南北战争爆发之际,他离开了美国,从麻省理工学院毕业,然后在德州仪器(Texas Instruments)和通用仪器公司(General Instruments)工作了多年。 在那些年中,任何微电子公司的组成部分都是其自己的产品,其设备比现在便宜了几个数量级,但价格却非常昂贵。 这是张自己写的:

当我在TI和通用仪器公司工作时,我看到很多IC设计师想离开并建立自己的业务,但是,使他们离开这些公司的唯一或最大的原因是他们无法筹集到足够的资金。组建自己的公司。 因为当时认为每个公司都需要制造,需要晶圆制造,所以这是半导体公司和IC公司中资本投入最大的部分。 我看到了所有想离开的人,但是由于缺乏筹集大量资金来建立晶圆厂的能力而停下来。

1985年,张国荣(Morris Chang)即将退休,但接受台湾政府的提议在工业技术研究院工作,该研究院原本是旨在帮助台湾引发工业革命并缩小发达经济体与发达国家之间的鸿沟。 1987年,在与ITRI合作的同时,Chang创立了TSMC,该公司已成长为全球最大的集成电路制造商。 台积电(TSMC)业务模型最初基于这样一个事实,即该公司不开发任何东西,只开发其他人的开发产品,这是创建用于开发和生产微电路的现代生态系统的第一步,即无晶圆厂模型。

抒情离题的终结什么是无晶圆厂?

Fabless是微电路开发和生产的模型,其中开发商公司没有自己的产品,而使用第三方工厂的服务,该第三方工厂也与其他开发商合作(有时有自己的产品)。

由于无需购买和维护生产设备,第三方工厂的存在可以从根本上将进入微电子市场的门槛(由莫里斯·张曾梦想过)降低至数百美元至数百万美元。 由于为复杂功能块(它们也是Silicon IP)的供应商形成了市场,它还允许您进一步降低此阈值。 如果您在自己的工厂中生产芯片,那么您只能依靠自己的优势,并且必须包含可以创建所有必要模块的团队。 如果工厂不仅由您自己使用,而且还由其他公司使用,那么有人已经解决了您面前的大多数典型任务,那么您可以使用别人的工作成果-或将您自己的解决方案转售给其他人,并且事先已经同意了价格和条件,以便没有人留在失败者中。 当然,您不太可能将自己的知识出售给直接竞争对手,但是在很多情况下,您无需参与利益冲突就可以赚钱。 IP分组市场的出现是出于可能性和渴望重用解决典型问题的结果而产生的,截至2017年,IP分组市场的规模接近40亿美元,并继续快速增长。

如何盈利?

买方IP-主要是节省。 根据各种估计,购买IP块通常比自行开发便宜2至5倍。 此外,购买该产品通常可以大大减少开发时间,因为您不需要独立生产测试芯片和修复错误。

对于IP开发人员而言 ,这是在利基解决方案上建立可运作的业务并显着降低业务成本的机会。 微电路成本的很大一部分是营销,包装,测试,技术支持,应用软件的成本,最后是用于大规模生产的照片模板的成本等。 等 如果您不生产成品,而只出售块状产品,那么您将没有所有这些费用。

工厂 -吸引更多客户的机会。 大型工厂正在努力创建一个由其周围的IP块供应商组成的生态系统,因为它们的使用可以显着加快设计速度,并且最重要的是,使其尽可能地自动化。 丰富的现成组件组合对最终产品的设计有很大帮助,因为它使您仅凭自己的专业知识就能完成自己的工作,而不必花费宝贵的资源来开发总体上的所有事物,特别是在人们已经开发出现成的解决方案的情况下他们为开发投入了大量的时间和经验,超出了您的承受能力。 因此,在为您的项目生产选择特定工厂时,广泛选择的现成IP可能是一个重要因素。

如何运作?

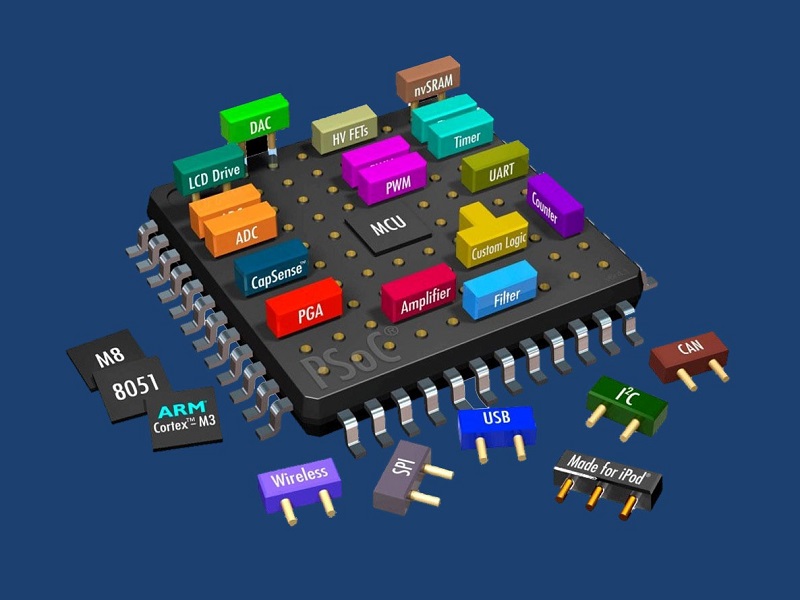

让我们以芯片上的球形定制系统为例,看一下内核的许可。 该系统将包含处理器内核,用于组合内核和外围设备的总线,一定数量的高速缓存存储器,用于与外界通信的接口(例如CAN和I2C),PLL,DAC和ADC。 为了实验的纯洁性,假设所有东西都将在没有独立开发的情况下购买。 你说:“愚蠢的假设,”你将不太正确。 当然,实际上,这种情况极为罕见,但是仍然有可能想象出,产品的杀手feature本身并不是某些功能块,而是现有功能块的特定组合。 例如,您是一个街区的第一个购买者(因此,竞争对手尚未拥有),或者您想出了一个现有街区,以供该街区使用,而该街区没有特色(因此,该细分市场中的竞争对手没有相似之处)。

所以,让我们从...开始

...不,不是来自处理器内核,而是来自模拟绑定。 例如,以模数转换器(ADC)为例-大多数微控制器和处理来自外界数据的任何其他系统的典型单位。

ADC是一个模拟模块,这意味着其参数不仅严重取决于其电路,而且还取决于该电路在芯片上的实现方式。 如果我们从一个技术过程中获取带有拓扑结构的最终文件,并在另一个工厂中以相同的设计标准进行生产,则可以得到完全不同的参数(更不用说转移到其他设计标准了)。 但是,从本世纪中叶开始就存在的“第二供应商”文化仍然存在。 例如,Towerjazz工厂提供了某些台积电制造工艺的副本。

ADC是与特定过程相关的硬IP模块的一个很好的例子。 为了购买这样的设备,您必须确切地知道最终产品将使用哪种技术制造,并且如上所述,必要的Hard IP的可用性对于工厂来说是一个重要的竞争优势。

硬IP如何交付? 这是一个有趣的问题,要回答这个问题,有必要讨论以何种形式开发这样的模块。 在大多数模拟模块的情况下,电路开发是在单个晶体管的级别上进行的,也就是说,输出文件将是电路文件和具有拓扑的文件。 此外,该方案和拓扑结构的功能都可能具有严重的商业价值,当然,我也不想将其抛在一边。 并且为了使客户端无法按拓扑对方案进行反向工程,通常也不会传输拓扑,因此,在通常情况下,传递的文件如下所示:

- 客户端收到的是高层行为模型,而不是电路,该模型没有公开实现功能。 这样的模型可以用Verilog-A编写。 一种替代方法是,某些CAD系统(例如Cadence Virtuoso)支持电路加密,也就是说,客户端将能够使用您的电路(或verilog-A文件),但无法打开和查看内容。

- 拓扑的尺寸布局,带有明显的外部结论,并描述了一个块占用了多少金属化层。

- 测试环境中主要参数的验证。

- 文献资料

当然,在这种情况下,第三方的参与是必要的,您可以向其转移拓扑而不必担心竞争和逆向工程。 该第三方是工厂,其在客户与承包商之间的中介作用是无晶圆厂芯片开发生态系统的重要组成部分。 当然,工厂应该有明确的声誉(这与书签有关),并且理想情况下,它自己不能产生任何类似的东西,因为在任何情况下,在竞争公司的工厂工作都是一种可疑的乐趣。 三星成功为自己和苹果同时生产处理器,但其他大型工厂通常要么专注于自己的生产(如英特尔),要么完全放弃自主开发(如台积电)。 顺便说一句,摆脱这种利益冲突的愿望是从AMD分配Globalfoundries(工厂市场第二大参与者)的动力之一。

抒情离题顺便说一句,在俄罗斯,俄罗斯没有纯粹的工厂。 而且,对于绝对所有市场参与者而言,生产自己的产品是当务之急,无晶圆厂开发商所生产的所有全国产芯片都是在其潜在竞争对手的设施或国外的纯工厂生产的。

抒情离题的终结此外,供应商与工厂之间的交互还有另一个重要的细节:工厂将您的IP块输入到其自己的数据库中,并进一步检查所有传入的项目是否存在您的拓扑(有人可能从您那里以及从非法那里获得该拓扑),以及请与您联系,询问请求制作的人是否具有许可证(因为许多廉价许可证意味着仅在一个项目中使用该设备)。 工厂检查的存在使Hard IP开发人员可以选择任何方便的许可选项-与项目数量,出售的芯片数量,将芯片投入生产的时间等相关。 等 但是在下一部分中将进一步介绍许可证的类型。

像芯片上典型系统中的硬IP一样,您将需要ADC,PLL,I / O接口的物理层。

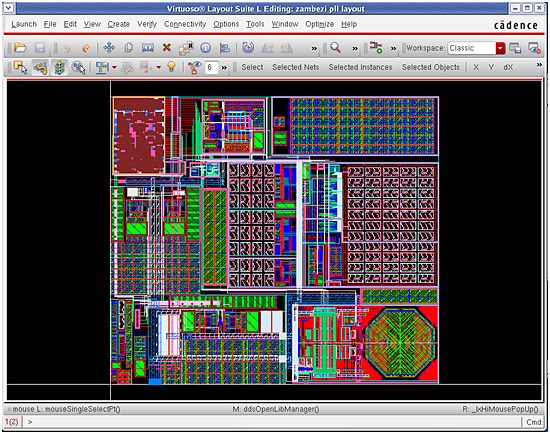

CAD窗口Cadence Virtuoso Layout Suite具有模拟Hard IP模块的拓扑(如果有兴趣,则为PLL)。 各个子单元(通常由不同的人制作)之间的边界,例如对于集成电路非常罕见的元素-右下角的电感器,清晰可见。 左上方是一个数字模块(可能是控制模块),其余部分是多位接口。

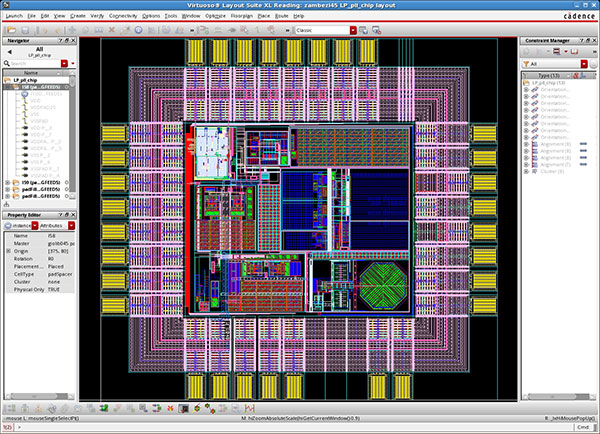

它是相同的,但是已经以成品芯片的形式(例如,用于测试)。 I / O焊盘以及从焊盘和电源连接它们的环清晰可见。

术语“硬IP”也用于FPGA的IP块。 在这种情况下,可以理解,已对块代码进行了优化,以用于特定的FPGA模型,并对其进行合成以放置在其中。

软IP

我们将考虑的下一个块是处理器核心。 实际上,几乎任何数字电路都可以代替它,例如带有Reed-Solomon码的信号编码单元,但是处理器内核被广泛使用,并且占整个市场的一半(包括由于复杂性和高成本)。

数字电路开发与模拟电路开发之间的主要区别在于,数字电路通常以特殊的高级语言(Verilog或VHDL)编写,然后由一个特殊的CAD系统根据此代码合成电路和拓扑。 因此,直到综合时,代码才不依赖于特定技术,并且同一块可以在不同的工厂中生产(或缝入FPGA)或以相同技术的不同版本生产(例如,针对高速或低功耗进行了优化)。 。 实际上,这是由开发公司(例如ARM)使用的。 这种与特定技术无关的数字模块称为软IP。

这是一个加法器位的方案:

这是一个八位加法器在芯片设计中的实际样子:

module adder(

input wire [7:0]a,

input wire [7:0]b,

output wire [7:0]out,

output wire carry

);

assign {carry, out} = a + b;

endmodule

, , , . , IP- .

Soft IP? :

• Clean, readable, synthesizable Verilog HDL, VHDL

• Cadence Encounter RTL Compiler synthesis scripts

• Documentation – integration and user guide, release notes

• Sample verification testbench

Encrypted source along with a complete certification data package (CDP) including all artifacts required for chip-level compliance.

, — , ( IP ). , . , - -, , .

, LEON3:

- , Cobham Gaisler, LEON3 GPL

- LEON3FT ( ): The LEON3FT core is distributed together with a special FT version of the GRLIP IP library, distributed as encrypted RTL.

- ( ) , LEON2FT, .

, , Verilog-, . Verilog- , , , , . digital watermarks, , IP.

, “Clean, readable, synthesizable” , , IP . , , , ( , hardware trojans) , , , .

, : soft IP , , ? , Soft IP, , .. .… :

ARM, , , , , ( ), IP , - , , . . (, , , ). Apple Imagination Technology in-house , Apple , Imagination ( ).

, — ( IP ) ( ).

soft IP FPGA, , . , Xilinx IP, ( ) , , ( , ).

, , .

— IP- . , -, . , IP, , IP , , IP ( , ); , - .

— . , ( IP).

— . , , , . — . , , .

— , , (, ARM Cortex). — , .

— . (, , ) , — ( , , ). ? , ( - , , ) . , , , , , — .

? : , , , . , Apple, ARM - , , (, ARM ) — .

: , , , , , , ( — ). , , . , , Apple, , , ! ARM, , Apple . , ARM . , , Apple — PowerPC, , PowerPC x86, Apple Intel.

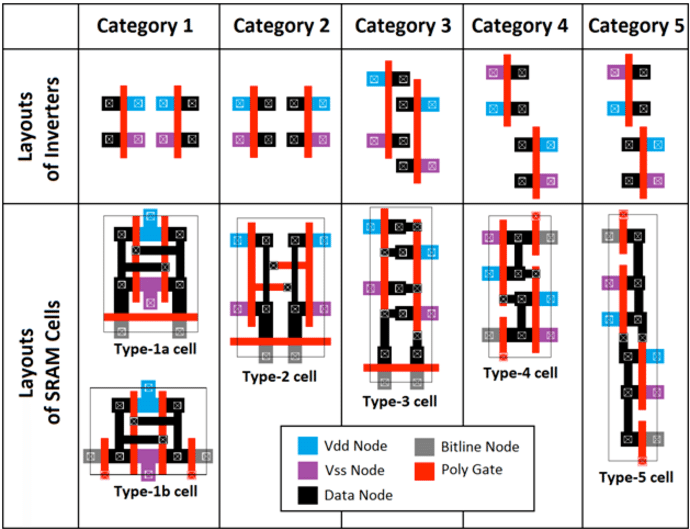

Soft IP , - , IP . :

- , “ — ”, .

- - IP ( ), IP, IP ( IP hardening) . ? , , , .

soft IP ( ), , , .. ..

Configurable IP

IP, hard soft — , . - , - . ? , IP-? ?

( , FPGA) , , , . , , IP- Hard IP, Soft IP ( , ).

— -.

Foundation IP

«-hard» IP- — foundation IP, . — , . , , , , , . , , ( ) , (, ) . «generic» , , , , , .

Foundation IP -, , , .

BarsMonster .

Verification IP

, , — , . , , , . , , . , - . “”. .

, — Verification IP. — , , ( ). Synopsys , , Synopsys — IP-. IP Design&Reuse Synopsys 828 Silicon IP ( ARC — ARM) 116 Verification IP .

verification IP CAN, ( APB AHB ARM) - . , , , .

?

, , , , ? .

:

- , ( verification IP ).

- — .

- ( , ).

- Soft IP , .

- , , .

- , , .

- , .

- , ( ).

, , ( ). , - , « - BGA 400-700 ». , Hard IP- 400-700 , , , 4-8 (, Soft IP). — ? , . , «-» .

— Synopsys IC Compiler , .

, — , , , , , , .

, , fabless- IP- , , , . , , ( “”) , , : , , , , , , - . , , — .

: Open Source?/ Open Source . , - ( ) , - . , , - . , , .

—

Opencores.org, — OpenRISC, ( FPGA), ASIC ( Samsung). Opencores, , - , ( ARM), FPGA. FPGA Proven, — ASIC Proven.

—

RISC-V. ( OpenPOWER OpenSPARC) , - , , ( ).

RISC-V — , MIPS, , , , ( , MIPS). RISC-V Foundation Google, Samsung, NXP, NVIDIA . , , , , OpenPOWER, , , ARM , ARM, , , ( Intel). - . RISC-V (

RISC-V), - , . , ,

RISC-V — Falcon NVIDIA.

: ?OpenCores, IP- ( ) . :

TSMC IP Alliance, IP .

Design&Reuse, IP-, ( ).

ChipEstimate, D&R, .

— ?, , , - .

— “” (), “” ( ), “” “” (211), “Neuromatrix” ( “”), RISC-V (Syntacore), ARM, MIPS, SPARC, MCS96, MCS51, C166, AVR, MSP430.

,

“ ” ( ):

IP-:

: ARM Cortex-M4F, ARM Cortex-M0, ARM946E-S c AMBA, ARM VFP9-S, SPARC v.8 c AMBA. 8- RISC .

IP- (PLL) TSMC, KeyASIC AnalogBits, Sidense Memory, - (eFuse) TSMC, IP- , ROM RAM ..

“ ” , IP- - (-, IP-).

IP? IP- (

“ ”,

“”,

211), . Design&Reuse ChipEstimate “ ” ( ) NTLab. , .