我从远处开始。 去年冬天,我碰巧制作了一个USB器件,其内核托管在FPGA中。 当然,我真的很想检查此总线的实际带宽。 毕竟,在控制器中-有太多事情要做。 您总是可以说有延迟,或者在那之上。 就FPGA而言,我看到了一个数据抽取块,因此他告诉我其中包含数据。 但是我设置为所有内容都已处理,并且可以接受新部分(同时,它已经在同一端点的第二个缓冲区中接收数据了)。 太好了,从一开始就准备好就绪状态,看看USB能够“锤击”而不停止的情况会怎样。

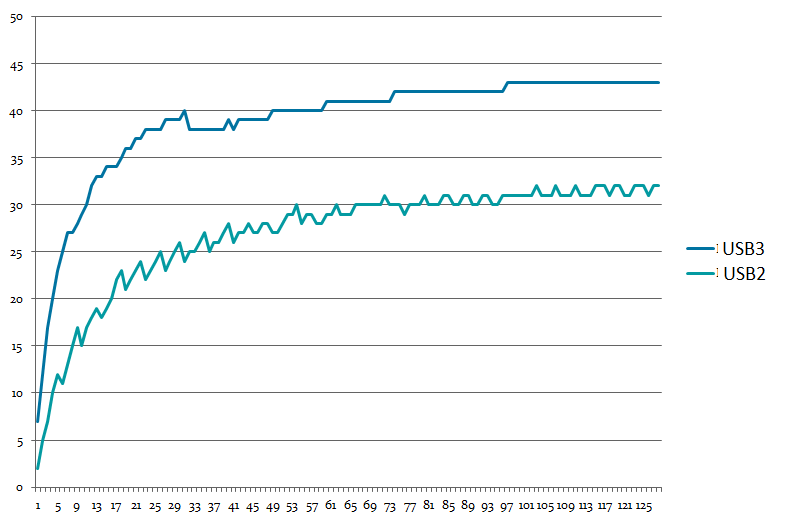

但这真是一件了不起的事情。 如果USB 2.0设备卡在“蓝色”连接器(即USB 3.0)中,则速度为1。 如果在“黑色”-另一个。 这是我的USB记录速度与数据长度的关系图。 USB3和USB2是连接器的类型;设备始终为USB 2.0 HS。

我在不同的机器上尝试过。 结果很接近。 没有人能向我解释这一现象。 后来,我找到了最可能的原因。 原因很简单。 这是USB 2.0控制器的属性:

控制“蓝色”连接器的控制器不支持。 相差仅约20%。

据此我们得出结论,带宽限制并不总是由总线的物理特性决定的。 有时还会叠加其他一些东西。 这些天,我们通过了这些知识。

初级实验

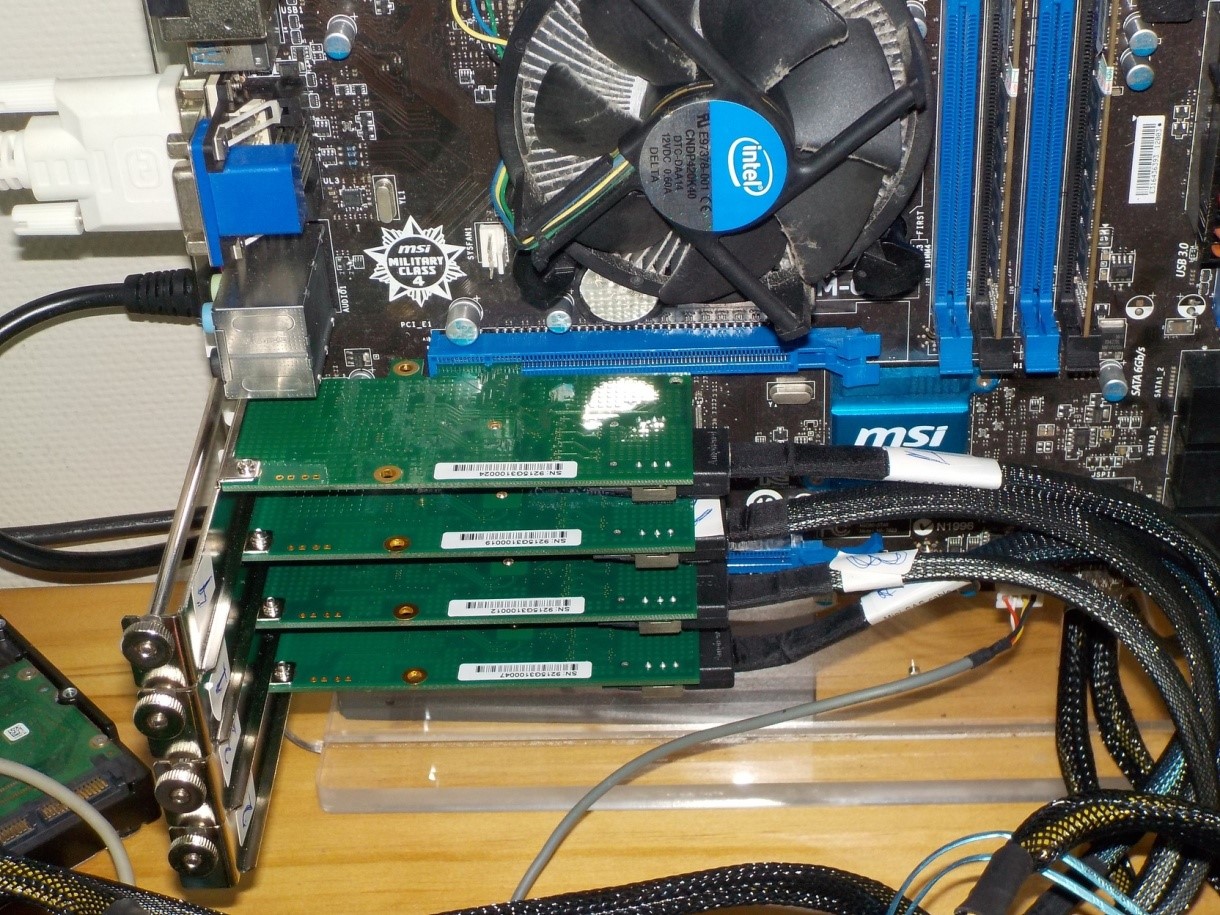

这样啊 一切开始变得平凡。 检查了一个程序。 同时检查了将数据同时写入几个磁盘的过程。 硬件很简单:有一个带有四个PCIe插槽的主板。 具有AHCI控制器的完全相同的卡插入所有插槽,每个插槽仅支持PCIe x1。

每个卡可提供4个驱动器。

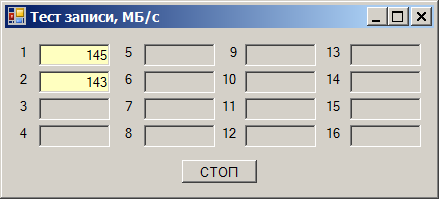

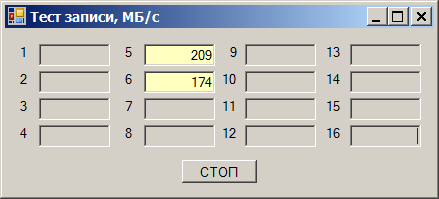

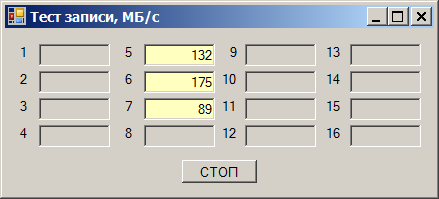

然后揭示了以下效果。 我们拿一个磁盘并开始向其中写入数据。 我们得到的速度为每秒180到220兆字节(以下,兆字节为1024 * 1024字节):

我们进行第二次开车。 写入速度从170到190 MB / s:

我们立即向两者写信-我们得到了速度上的下降:

总速度约为290 MB / s。 但是令人惊讶的是,我们在同一驱动器上但在其他通道上调试了该程序(结果证明)。 那里一切都很好。 我们迅速转移到这些渠道(它们将通过另一张卡),我们获得了出色的成绩:

我会在好地方买一个插槽

我必须马上说,将所有内容归咎于其他人的组件是不值得的。 此处的所有内容均由我们编写,从程序本身开始,以驱动程序结束。 这样就可以监控整个数据路径。 仅当请求发送到硬件时,未知消息才会出现。

经过初步分析,结果表明速度不受“长” PCIe插槽的限制,而受“短” PCIe插槽的限制。 长卡可以在其中插入x16卡(尽管其中一张可以在不高于x4的模式下工作),而短卡仅适用于x1卡。

一切都很好,但是原则上当前卡中的控制器不能以PCIex1以外的模式工作。 也就是说,无论插槽长度如何,所有控制器都必须处于完全相同的条件下! 但是没有 谁生活在“多头”中-工作快,谁生活在“短”中-慢。 好啊 又快-多快? 添加第三个驱动器,写入所有三个驱动器。

在“短”插槽中,限制仍然约为290 MB / s:

在“长”中-大约400 MB / s:

我搜索了整个互联网。 首先,一段时间后,我已经从文章中笑到说x1的PCIe第1代和第2代的吞吐量分别为250和500 MB / s。 这些是原始兆字节。 由于第2代的开销(我用这个非俄语单词表示与主数据沿同一行的服务交换),我们每秒获得的可用流恰好为400兆字节。 其次,我顽固地找不到关于290号魔幻数字的任何东西(展望未来-我仍然没有找到它)。

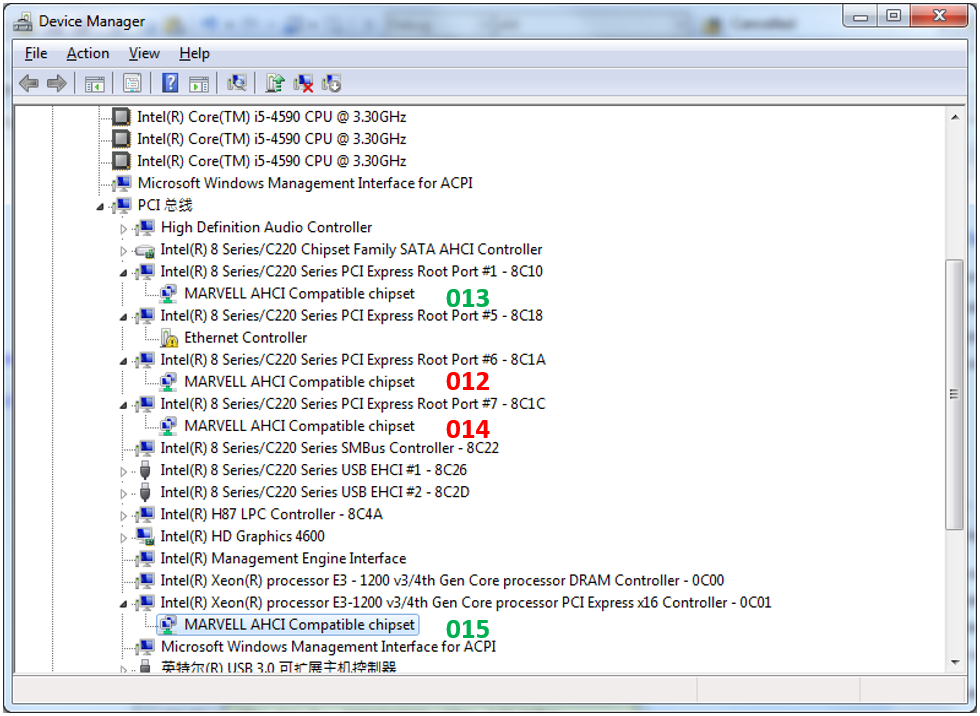

太好了 尝试查看包含控制器的拓扑。 在这里是(013-015-这些是设备名称后缀,我通过匹配它们来以某种方式进行区分)。 绿色快,红色慢。

我们甚至不考虑控制器“ 015”。 他住在一个专门为视频卡设计的插槽中。 但是013rd和014th的012nd连接到同一开关。 他有什么不同?

一些文章说,不同的卡在最大有效负载设置上可能有所不同。 我研究了所有卡的配置空间-该参数适用于每个人,且具有相同的最小值。 而且,该主板芯片组的文档说没有其他含义。

总的来说,我在配置空间中翻阅了所有内容-一切都配置相同。 和速度不同! 反复重读芯片组的文档-无带宽设置。 优先级-是的,已经写了一些有关它们的内容,但是在完全没有其他通道负载的情况下进行了测试! 也就是说,它不在其中。

以防万一,我什至关闭了中断程序。 处理器负载已增加到疯狂的数量,因为现在它不断地愚蠢地读取就绪位,但是速度读数没有改变。 因此,不可能将这个问题归咎于该子系统。

那其他板呢?

我们试图将主板更改为完全相同。 没有变化 他们试图更换处理器(有理由认为它很垃圾)。 同样,速度没有变化(但是旧处理器确实很垃圾)。 我们安装了新一代主板-一切都在所有插槽上运行。 此外,即使在“长”插槽,甚至在“短”插槽中,最大速度也不再是400,而是每秒418 MB:

但是这里-没有奇迹。 使用通常的手部移动(这些天已经使用了),我们读取了配置空间,并看到Max Payload参数未设置为128,而是设置为256字节。

更大的数据包大小-更少的数据包。 发送它们的开销更少-更多有用的数据设法在同一时间运行。 没错

那么谁该怪?

对于文档中的标题,我不会给出确切的答案。 但是我的想法是遵循以下路径:假设流量限制是在芯片组内部设置的。 它不能编程,设置紧密,但是可以。 例如,每个差异等于每秒290兆字节。 一对 更多-它已经在其内部机制的芯片组内的某个地方被切掉了。 因此,在“长”插槽(您可以将卡最多粘贴到x4的插槽)中,芯片组内的卡不会被割破,因此,我们会受到x1总线的物理限制。 在“短”连接器中,我们遇到了此限制。

实际上,检查这并不容易,但是非常简单。 我们将第013个插槽固定在AHCI上,而不是AHCI上,而是放在SAS控制器上,该控制器一次可服务8个驱动器,并且可以在x4的PCIe模式下工作。 我们将4个智能SSD驱动器连接到它。 我们着眼于记录速度-就像灵魂欢欣一样:

现在,我们添加出现在第一个测试中的那四个磁盘。 SSD性能可观地下降了:

我们计算通过SAS控制器的总速度,得出每秒1175兆字节。 除以4(到“长”插槽的行数很多),我们得到...鼓卷...每秒293 MB。 我已经在某个地方看到了这个号码!

因此,在该项目的框架内,事实证明问题不在于我们的程序或驱动程序,而在于芯片组的奇怪限制,这些限制可能紧密地“连接”在一起。 开发了可以在项目中使用的主板选择方法。 但总的来说,我们得出以下结论。

结论

- 在现实生活中,设备通常比理论上的性能要差。 如USB所示,驱动程序甚至可以施加限制。 有时可能会拿起没有此类限制的设备(或其驱动程序)。

- 限制甚至可能没有记载,但表达清楚。

- 很多文章说一对差分PCIe产生。 1和gen 2每秒提供大约250和500兆字节,这是错误的。 它们彼此复制相同的错误-每秒兆字节的原始数据。 开销累积在接口的多个级别。 凭借128字节的最大有效负载,PCIe gen2实际上每秒获得约400兆字节。 在新一代的PCIe中,一切都应该稍微好一点,因为物理编码不是8b / 10b,而是更经济,但是到目前为止,还没有找到可以在实践中验证其性能的驱动器控制器。