尽管现代微电路中的晶体管已经讨论了摩尔定律的逝世数年,并且微型化的物理极限已经接近(更确切地说,它已经在某些地方成功规避了),但现代微型电路中的晶体管尺寸却无可避免地减小了。 但是,这种下降并不是徒劳的,而且用户的胃口增长快于芯片开发商的能力。 因此,除了晶体管的小型化以外,还使用了其他的,通常不少于先进的技术来制造现代微电子产品。

在我的最后一句话中,我特意使用了“微电子产品”一词,而不是“微电路”一词,因为本文将重点关注这样一个事实,即在CPU或GPU外壳内部可能不仅有一个晶体,而且有多个芯片的整个系统,因此称为:包装中的系统或包装中的系统。

术语“一个案例中的系统”远不如相关术语“片上系统”广为人知,开发人员喜欢胜任任何事情。 而且,现在几乎所有芯片(最简单的芯片除外)都是芯片上的系统,微处理器集甚至南北桥的单个芯片的时代已经成为过去。 片上系统的优势非常明显:电路板上的外壳更少,面积更小(因此更便宜),杂散电感和容量更少(这意味着产品将更好,更快地工作),用户更容易(实现起来更方便,出错空间更小),生产便宜(代替几种专用的微电路,可以生产一种通用的微电路)。

但是片上系统也有其缺陷。

首先,当您尝试将所有物体一次都推到一个晶体上时,就有冒这样一个风险的风险,即要获得这样一个大小(且有很多支脚)的芯片,以至于无法适合任何情况。 此外(正如专业技术人员在评论中所建议的那样),很大的芯片有可能无法进入光刻扫描仪领域的规模。 您可以绕开此限制,但是从技术上讲这非常困难,因此非常昂贵。

其次,芯片的尺寸越大,成品率的百分比就越低,尤其是在生产中,您需要在光掩模上缝合几个窗口。 当然,这也会影响成本。

第三,如果您的系统由异构组件组成,那么将它们全部组合在一个芯片上可能对系统质量来说太困难,太昂贵或太坏。 例如,DRAM需要特殊的电容器,将它们添加到“正常”制造过程中对于工厂而言可能会变得不合理地昂贵(因为这将被迫提高客户价格)。 硅上的射频或功率组件的参数可能比A3B5材料(砷化镓及其类似物)的参数差得多,并且同一晶体上数字和模拟部分的连接会产生噪声问题。

上面提到的所有因素的结合导致了一个事实,即“将所有东西全部放置在一个晶体上”的趋势已被更加平衡的方法所取代,并且包装盒中晶体的技术迅速发展。

性能和产量

我想到的第一个示例当然是AMD微处理器(请参阅KDPV)。 用于多核产品的系统被认为是公司近期崛起的重要原因之一,这是在英特尔因大型芯片产量低而推出新技术工艺问题的背景下发生的。

该图显示了28核Intel Xeon芯片。 这些处理器的尺寸达到了惊人的456平方毫米,而对于八核芯片,AMD芯片的最大尺寸约为200平方毫米,并且具有更多核的产品是由几个相同的晶体组装在处理器盒中的两层印刷电路板上的。

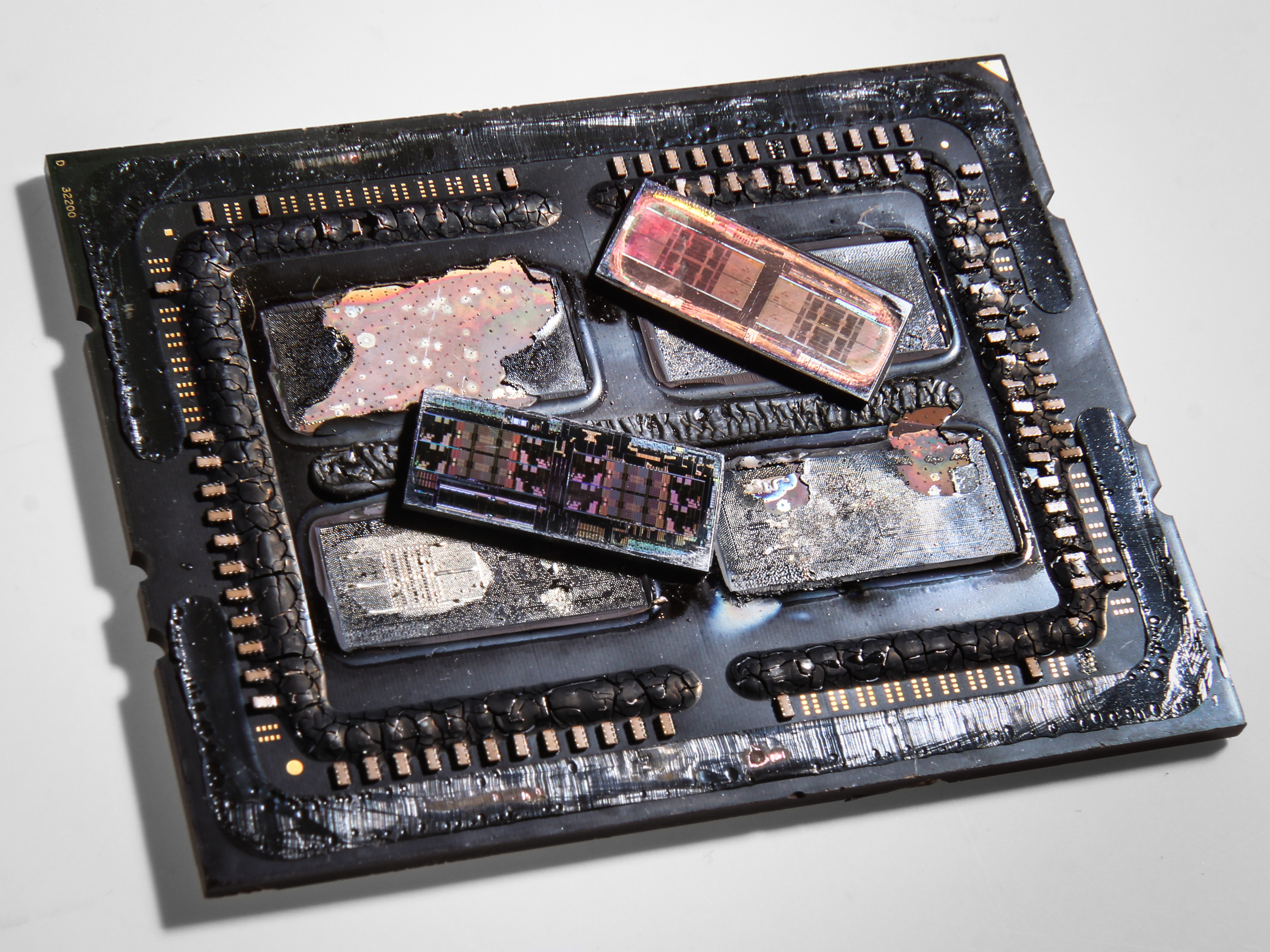

在此图中,您可以看到EPYC和Threadripper处理器(又名KDPV)外壳内部的电路板设计。 四个八核晶体位于两层板上。 如果是Threadripper,则禁用一半的内核。 为什么如此不合理地使用晶体?

首先,生产一种类型的晶体可能比几种不同的晶体便宜。

其次,其余的线束也是如此-与开发和生产几种不同的模型相比,不必要的禁用会更便宜,技术更多。

第三,最适合200毫米芯片的成品率百分比也不理想,并且最终产品的这种设计允许使用并非所有芯都起作用的晶体。 英特尔也做同样的事情,但是由于晶体更大,它们的输出问题要严重得多。

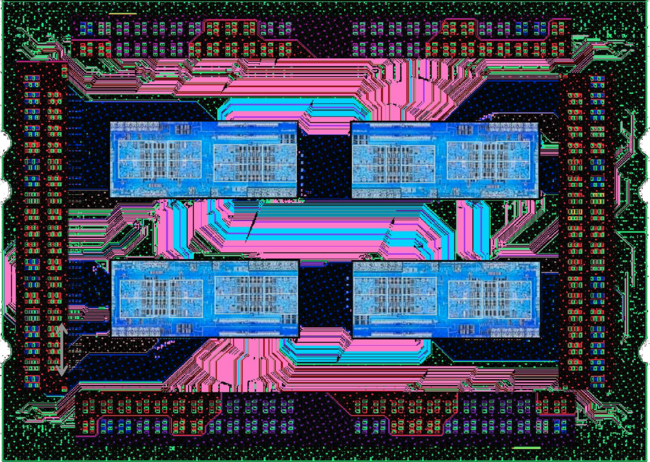

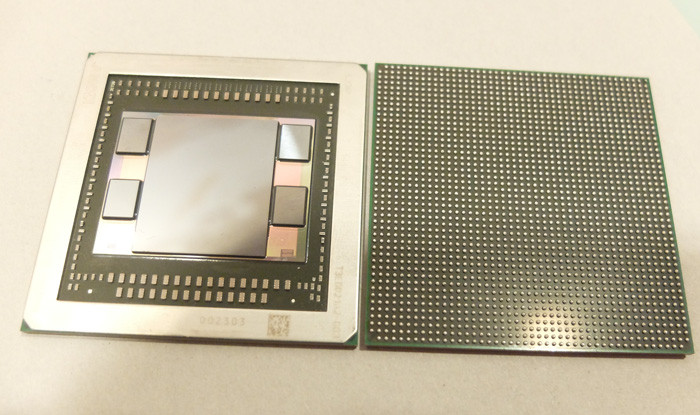

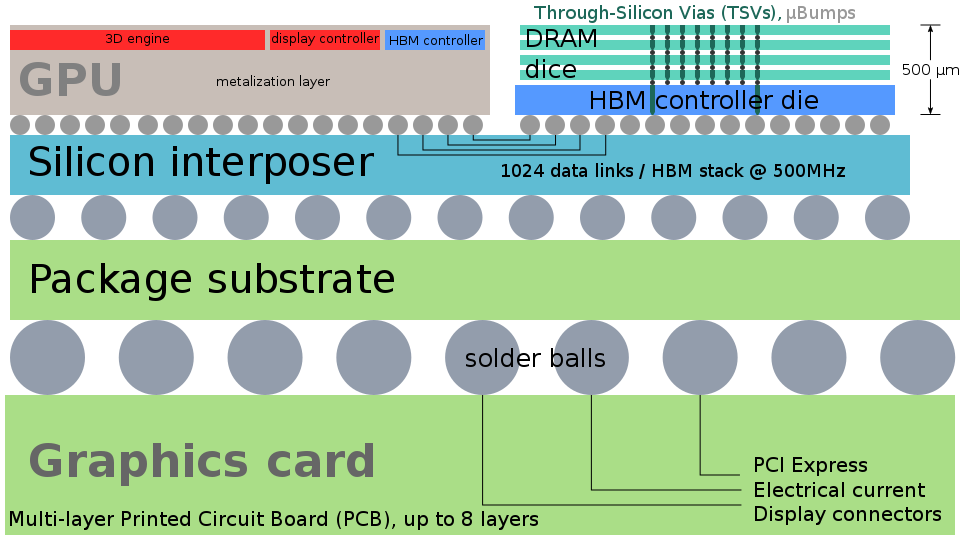

这是一个更有趣的例子,同样来自AMD。 AMD Fiji是位于机箱中并带有内置高速内存的GPU。 为什么这很重要? 因为从处理器到内存的短得多的线路使得可以实现高速,从而获得更高的性能。 与前面的示例不同,表壳内部的晶体不同。 而且,乍一看似乎没有五个,但有二十五个。 这是结构的一部分:

最顶层是GPU芯片本身,是使用TSV(硅通孔)连接的几个(在本例中为四个)存储芯片的“架子”,这些导电柱贯穿晶体达到整个厚度。

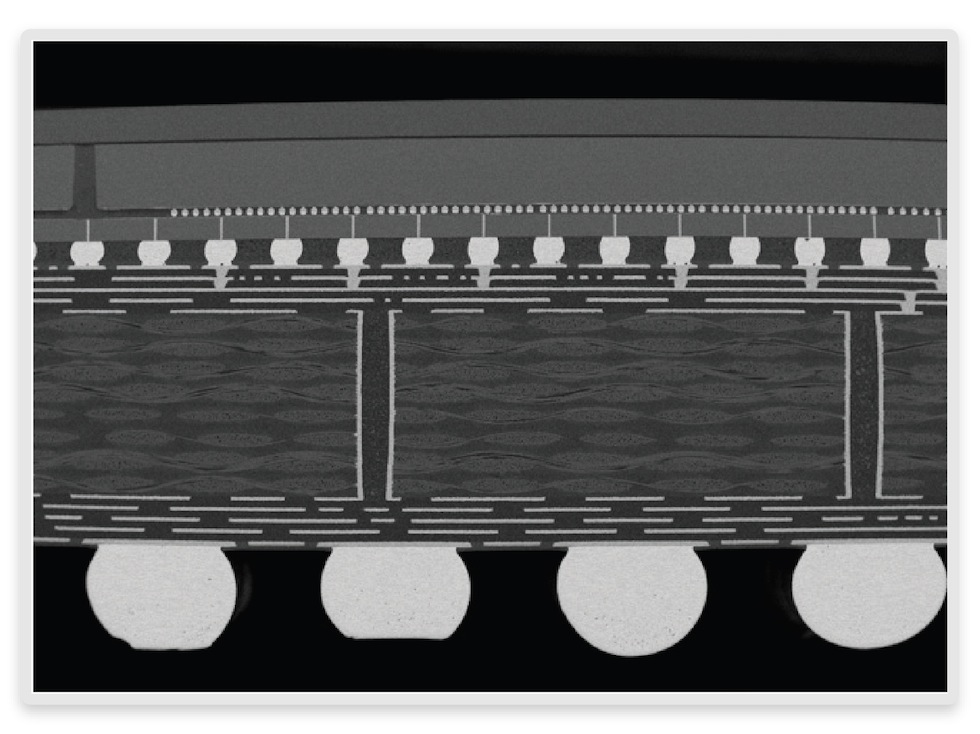

TSV看起来像这样,真实而真实。

TSV技术最初仅用于内存阵列(毕竟,永远不会有太多的内存,对吗?),现在正变得越来越普及,这要归功于位于GPU和内存下方的下一个芯片。

Silicon Interposer替代了由硅晶体制成的多层印刷电路板,该多层印刷电路板包含多层金属化层和TSV,用于连接顶部和外壳的芯片。 硅的使用允许获得比印刷电路板小得多的元件尺寸(微米单位),但是同时设计标准可以足够粗糙,因此该连接芯片具有高产量和可承受的价格。 元件的尺寸较小意味着对连接的寄生参数的影响较小,并且已经提到的TSV比印刷电路板上的通孔紧凑得多,并允许数百个甚至数千个触点通过中介层拉到外壳。 对于直径为100-150毫米的晶圆的过时工厂而言,此类互连芯片与MEMS一起是重要的新市场。

Xilinx是3D集成的另一个先驱。 从技术上讲,它的FPGA接近AMD产品(尤其是集成内存的产品),动机也相似:FPGA是一种市场利基,在早期向新制造工艺过渡可以提供比竞争对手更大的优势。 根据各种估计,在技术生命的早期阶段,将晶体尺寸减小三到四倍可以使产量提高两到三倍,从百分之几十到一半以上。 而且,FPGA是一种常规结构,在该结构上可以方便地跟踪技术缺陷。 因此,FPGA制造商是新制造工艺的典型“第一客户”,由于Xilinx的产品包含多个小晶体而不是一个完整尺寸的晶体,因此其推出新模型的速度比竞争对手快了几个月。

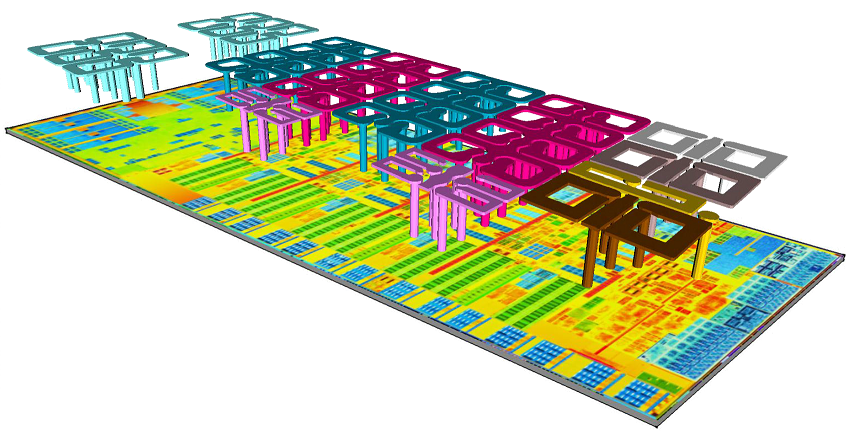

这是Xilinx FPGA内部的横截面。 上层芯片实际上是FPGA的一部分,与插入器的触点非常小(40-45微米),将多个芯片连接在一起,底部是外壳的底部,外壳有十几层自己的金属互连。

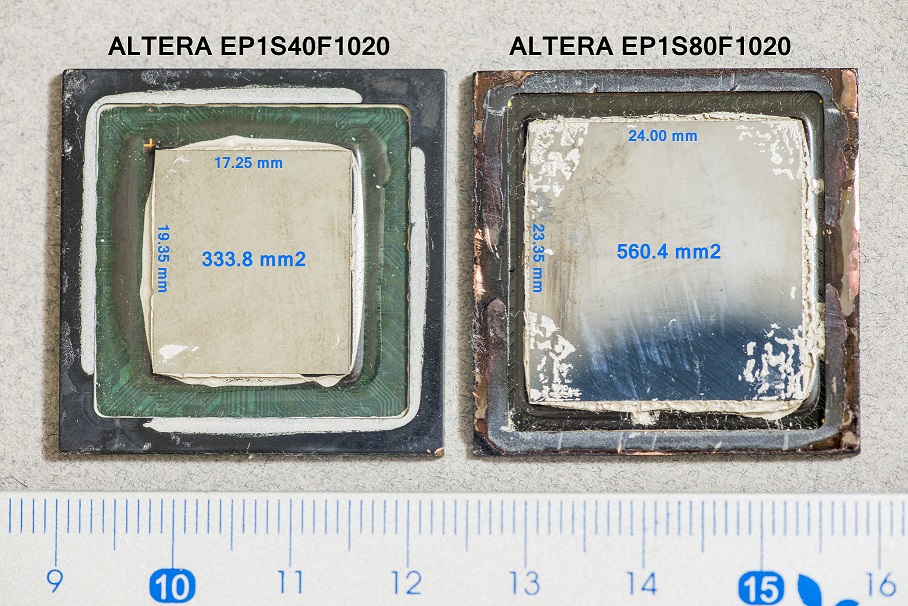

作为比较-在一个巨大的晶体上使用FPGA Altera。 560平方毫米,卡尔! 如果突然,微电子生产技术人员阅读了这篇文章,请确保他们没有心脏病发作。

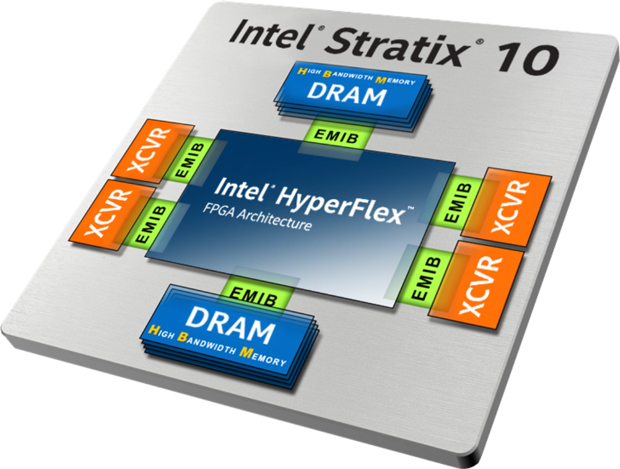

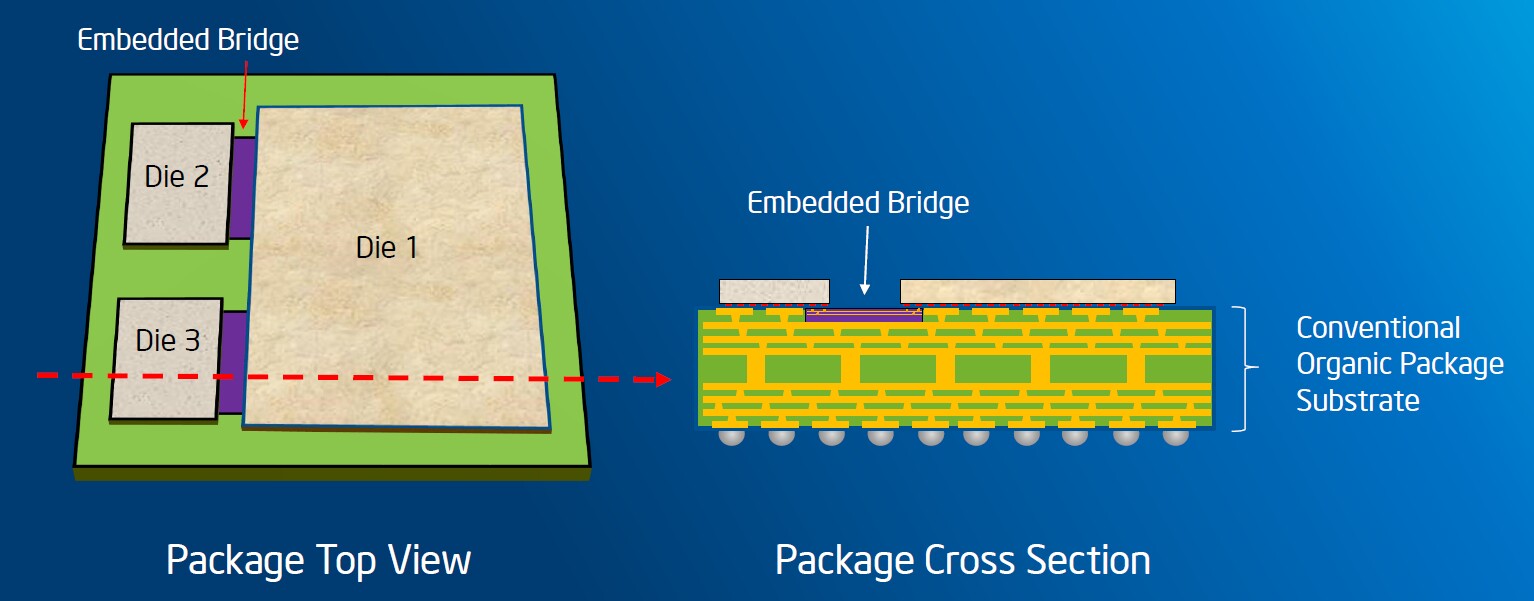

但是,英特尔/ Altera当然不会坐以待,,看着竞争对手的成功。 他们在封闭系统中的最新发展是嵌入式多芯片互连桥(EMIB)。 使用Intel Stratix 10 FPGA可以很方便地查看它。

如您所见,EMIB互连(一个!)FPGA芯片,存储器(这里是多层结构)和外围晶体。 那么这是什么EMIB? 我写的关于硅中介层的文章稍高一些,因为它采用了更严格的技术工艺,因此其价格比使用薄技术制造的类似尺寸的芯片要低得多。 然而,插入器是巨大的。 是否可以缩小尺寸?

英特尔的答案是肯定的。 EMIB的想法是使用多个小插件而不是一个大中介插件,然后将它们直接集成到主体基板中。

这是使用硅中介层创建的产品的一小部分。 请注意微电子标准对它们的巨大尺寸,以及如上所述的Xilinx战斗芯片被分成几小块这一事实。

不仅仅是性能。

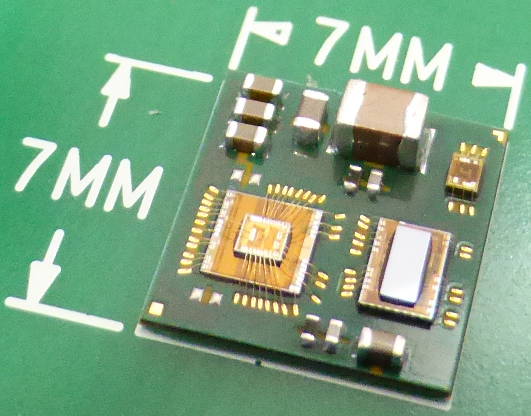

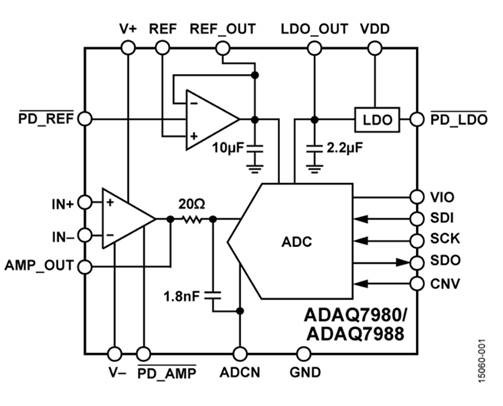

下图显示了Analog Devices ADC外壳的内部和电路图。 看起来就像是用于ADC的完全普通的印刷电路板,只是更小,对吧? 没错,就是这样,仅由于使用了开放式框架组件,才减少了与虚假元素相关的错误,并且该电路板是由Analog Devices开发的事实,它们可以节省大量客户时间,同时请确保用户不会因选择错误的组件而搞砸了。组件或接线不良。

但是,上图中有一个小技巧:看到放在两层楼上的水晶了吗? 上层晶体是一个芯片,具有ADC本身的有源组件和(显然)一个双运算放大器,下层晶体是无源组件(电容器和电阻器)。 在单独的晶体上执行可使您使它们的尺寸更大(从而减少误差),而又不增加主晶体(也因此增加了成本)。

所有这些都可以在一个芯片上完成(实际上,这并不罕见,尤其是对于内置在微控制器中的ADC而言),但是这样的芯片将更大(如我们所知,存在降低可用百分比的风险),并且他的技术将必须支持所有必要的附加选项。 另外,同一晶体上不同块的组合将导致需要确保它们彼此不影响(例如,以某种方式消除晶体基板上的噪声)。

其他外壳功能

我们已经发现,将不同的元件(包括无源SMD组件)包装在一个外壳中,可以使您显着减小最终产品的尺寸,甚至提高其速度。 但是,如果我们将外壳本身用作设备的功能元件怎么办?

2013年,英特尔处理器(Haswell微体系结构)实现了集成稳压器(FIVR-完全集成稳压器),其中稳压器的有源部分实现在处理器芯片上,而无源部分(电容器和电感器)集成到机箱中。

积分电感使所有芯片开发人员都头痛不已,因为获得芯片上的线圈不仅具有最佳参数,而且具有巨大的参数(这意味着它们非常昂贵,尤其是采用薄技术时)。 这是关于无芯的信号线圈,根本没有任何动力传输的说法。 英特尔通过将数十个工作频率为160 MHz的并行小线圈集成到微处理器外壳中,成功地解决了这个问题。 因此,他们能够显着简化微处理器的电源要求。

但是,此开发出现了问题,下一代Haswell处理器中不再有Intel FIVR处理器。 从那以后,一直有谣言说他们将重返FIVR,但到目前为止,他们仍然是谣言。

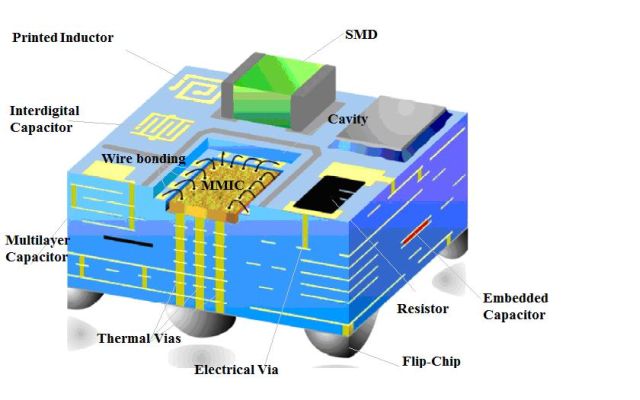

但是,即使没有英特尔,例如在LTCC(低温陶瓷)类型的外壳中,无源组件集成的方向也在积极发展。 当然,这里存在局限性和陷阱(例如,与评级的准确性相关),但是这项技术是有需求的,并且正在积极开发中。 分层的LTCC外壳看起来像这样:

该图显示了由多层陶瓷制成的所有类型的无源元件,甚至是金属散热器(对于强大的微波电路来说就是这种情况)。 实际上,它是外壳与陶瓷印刷电路板的混合物。 这样的零件在RF模块中非常受欢迎,并且在小规模生产中也相对便宜。

还有什么

在这种情况下,系统有很多潜在的应用程序,几乎不可能一一列举。 此外,不断出现新的事物,包括由于这些技术比10-7-5-3纳米晶体管便宜得多的事实。

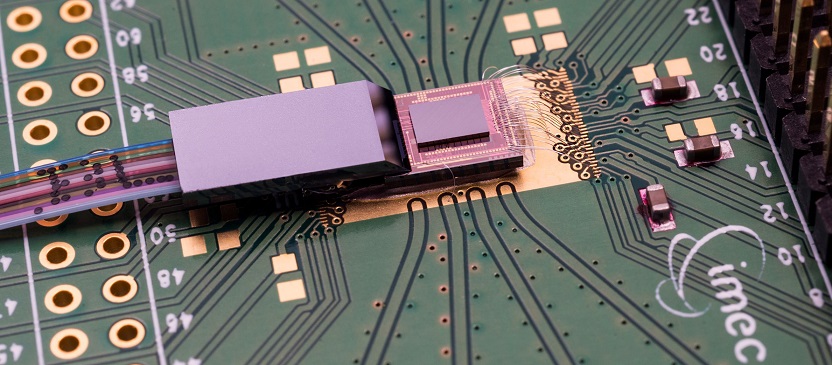

一个新的应用和特性的好例子就是在一个封装中实现了异构芯片的集成,这是各种光学系统,其中SiP允许您组装接收器或发射器(通常不在硅上制造)以及它们的电源和控制电路。 在下图中-比利时研究机构IMEC组装了一个400 Gb / s的原型光链路(承诺在太比特之前)。

此外,在这种情况下,该系统的有希望的应用还考虑了诸如内置液体冷却装置的内置插补器(不仅是游戏处理器,还有电源键和激光器),壳体中集成的MEMS单元等。不在摩尔定律的狭窄框架之内。 此外,在以下情况下,无处不在的物联网被认为是系统的重要市场,在这种情况下,小尺寸,不存在虚假元素的损耗(主要是能量,而不是时间)以及将无源组件(例如无线电路径的一部分)集成到微电路中的能力很重要。