1.简介

众所周知,鸡蛋和鸡蛋的问题是:雇主不想雇用没有工作经验的毕业生,但是毕业生可以在哪里获得工作经验? 在微电子学中,鉴于需要大量的特定经验,这个问题尤为严重。 自苏联时代以来,我们的大学以最广泛的理论培训而闻名,这可以帮助毕业生在生活中的任何困难处境中。 但是,现代工业需要实践经验。 我们在这里补充说缺乏动力,这导致大约15%的毕业生从事该专业的事实,并且我们在该行业中遇到了最严重的人员短缺,这对人员素质提出了很高的要求。 但是,如果每个学生都可以用自己的水晶“闪烁灯泡”,情况可能会以完全不同的方式发展。

图1. KDPV

是什么阻止了像MEPhI和MIET这样的培训国内微电子学的巨人采取与外国同事(例如MIT或UZH)类似的行动,即不允许研究生发行自己的晶体? 当然,可以假设自己的晶体的生产是非常长,复杂和昂贵的任务,因此对于机构而言是昂贵的,对于学生而言是不可能的。 但是,事实并非如此。 让我们看一下国内微电子市场上可用的技术之一,熟悉该技术将使该学生在未来的就业方面变得更具吸引力,而针对该学生的提议将使该大学在申请人和雇主的眼中大大提高其评级。

2.什么是BMK?

BMK是基本的基质晶体。 变得更清晰了吗? 然后走到一边,看看大大简化的定制芯片制造(ASIC)生产周期:

- 模式描述开发

- 拓扑创建

- 将技术文件传输到工厂并等待晶体准备就绪

- 测量获得的晶体

- 机壳

- 待售

这里有两个非常“长”的要点-方案的制定和对工厂结果的期望。 各种各样的方法被用来减少开发时间,在学生环境中,最好的解决方案是团队合作,但是我们对第二点感兴趣-工厂的工作时间。 由于微电子工厂是一种非常惰性的产品,因此一切都应按计划进行。 赶不上生产开始日期吗? 下一次尝试是通过季度。 根据产品的复杂性,生产本身可持续长达六个月。 此外,这六个月是在高度自动化的机器上批准的生产周期,而不是人员的草率。 如何减少这些用语? 通过在所有产生的方案中引入一定的共同基础,以便引入差异的阶段很快。

这个共同的基础是BMK-带有预先排列的晶体管的晶体,其功能目的由金属化层决定,金属化层允许晶体管互连。 这些互连形成了晶体的独特功能。

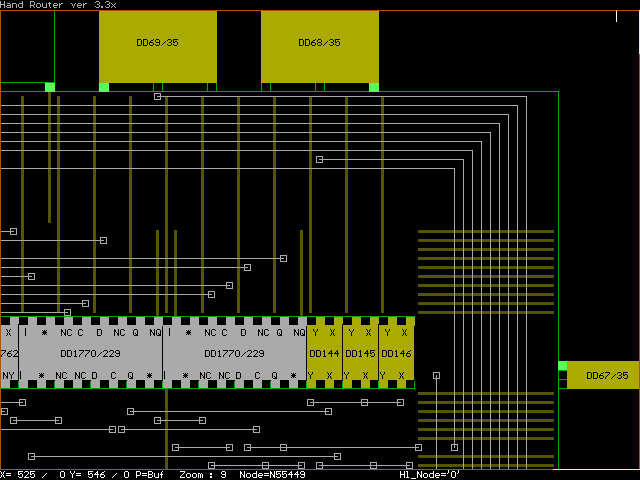

图2.手动路由器v3.3,最初来自NICEVT的肠道,创建于1980年代至1990年代。

在一个BMK上,使用不同的金属化方案,可以为各种组织生产数百个不同的微电路。 在这种情况下,BMK本身成为该工厂的批量生产产品,并且可以根据客户要求快速更改精加工阶段(金属化层)。 因此,我们更频繁地将新产品投入生产并降低价格。 对于学生的发展,这两个方面都是极为相关的。

3.为什么选择BMK?

让我们比较使用不同的培训方法的好处,并以最低的成本查看获得最大效果的方法。

表1.使用各种方法进行学习的教育效果比较

标头编码 否则,它不适合布局的宽度。

A-面向FPGA的开发

B-BMK,不使用FPGA,但实际发布

C-使用FPGA且实际发布的BMK

D-ASIC,无FPGA,无实际发布

带有FPGA且没有实际发布的E-ASIC

F-具有FPGA的ASIC和实际发行版

G-kaf的MEPhI当前的培训计划。 27

| 路线组成 | 一 | 乙 | ç | d | Ë | ˚F | g ^ |

|---|

| 问题陈述 | ■ | ■ | ■ | ■ | ■ | ■ | ■ |

| RTL编程 | ■ | ■ | ■ | ■ | ■ | ■ | ■ |

| 基于ASIC的RTL编程 | □ | ■ | ■ | ■ | ■ | ■ | □ |

| 使用现代CAD | ○ | ■ | ■ | ■ | ■ | ■ | ○ |

| 了解特定于FPGA的代码 | ■ | □ | ■ | □ | ■ | ■ | ○ |

| 了解合成器 | □ | ■ | ■ | ■ | ■ | ■ | ○ |

| 了解约束要求 | ○ | ■ | ■ | □ | □ | ■ | □ |

| 了解放置和跟踪的重要性 | ○ | ■ | ■ | □ | □ | ■ | □ |

| 测试中 | ■ | ■ | ■ | ■ | ■ | ■ | □ |

| 创建验证环境 | ■ | ■ | ■ | □ | ■ | ■ | □ |

| 多角模拟 | ■ | ■ | ■ | ■ | ■ | ■ | □ |

| 提取建模 | □ | ■ | ■ | ■ | ■ | ■ | □ |

| 机壳 | □ | ■ | ■ | □ | □ | ■ | □ |

| 模拟电路 | □ | ■ | ■ | ■ | ■ | ■ | ○ |

| 与测量装置一起使用 | □ | ■ | ■ | □ | □ | ■ | ○ |

| 在实验室工作 | ■ | ■ | ■ | □ | □ | ■ | ○ |

| 费用 | 1个 | 2 | 3 | 0 | 1个 | 4 | 0 |

■-存在于程序中;

□-程序中不存在;

○-可以选择。

这张表完全是根据我对真空中球形毕业项目中特定阶段的存在如何影响学生的勤奋的看法而完成的。 实际上,有人可以在没有教学帮助的情况下掌握整个路线,而有人则无法在Verilog上编写多路复用器。 “成本”行反映了顶部的位置,但绝不是乘数。 同样,由于多种不同的原因,“成本”没有考虑到CAD的实际成本。

现在很明显,以较低的额外成本,使用FPGA并以实际发布为目标发布BMK的路线完全涵盖了发布ASIC所需的相同技能。 其余路线虽然名义上涵盖了广泛的技能,但实际上,由于缺乏动力进行大量努力而没有任何明显的结果,因此学生并未认真地进行。

4.市场观察

迄今为止,入门级微电路的设计已成为一项相当简单的任务:每个人都听说过FPGA(可编程逻辑集成电路),代码合成器,用于布置组件的程序以及随后的微电路跟踪。 同时,许多新手开发人员很难想象BMK是什么,如何使用BMK以及它提供的优势。 不幸的是,对于BMK制造商而言,这种情况导致以下结果:

“ 2009年的分析表明,由于在签发许可证的基础上扩大了进口FPGA的应用范围,部分消费者流失了。” (C)Anstrem OJSC的2009年年度报告。

现代微电子市场上有许多BMK制造商:国内外。 特别是,在俄罗斯和白俄罗斯联邦州,至少有六家芯片制造商提供其BMC进行开发:Angstrem OJSC,IEC NN,Progress NIIMA JSC,技术中心科学与生产中心,物理NPO OJSC和Integral Minsk ”。

通常,使用诸如Cadence,Synopsis或Mentor Graphics之类的著名公司的专用CAD系统来开发微电路,但是对于BMC,一切都有些复杂。 该软件不提供对BMK的官方支持,它是一种单独的微电路,但是可以通过各种技巧使其在正确的模式下工作。 在这种情况下,BMK开发人员必须开发自己的独特设计路线,有时会使用OpenSource软件(例如Yosis)以及独立开发的软件。

- 对于Angstrom OJSC,很难找到确切的信息和所用的CAD。 但是,有先决条件可以相信不再使用其CAD“ Nevod”,并且已经完成了向Cadence产品使用的过渡。

- IEC NN,OJSC NPO Fizika,JSC NIIMA Progress和Integral均未提供所用CAD的信息,但是Integral在Cadence下具有PDK,因此我们可以得出结论,其余路线也在那里。

- NPK“技术中心”使用其CAD“ Ark”,该CAD几乎实现了整个设计路线。 无论如何,这是在其网站上批准的。

5.多少个阀门足以满足每个人的需求?

不愿意与BMK合作的一个普遍原因是不确定所开发的方案是否适合该BMK以及所有这些以什么速度运行。 当然,当BMK系列具有单个设计库时,这是很好的,并且如有必要,您可以跳到容量更大或更快速的晶体,但这并不总是可能的。 例如,在这里,关于台积电的一切都非常清楚:有许多公司公开声明其电路在其中一个或另一个电路上的速度。 过程。 那我们的BMK呢? 在哪里可以获得基于BMK创建的产品列表,并查看其性能?

一些例子:

- 数模BMK。 大约300个门+ 8个功率晶体管。 实施了具有两级保护的2分钟计时器方案。 在电流镜,功率晶体管上监控负载,以控制负载。 降低功耗,使用32.768 kHz石英,电源电压范围为1.8V至9V。

- 数字高兴。 持久性BMK。 100,000个阀。 逻辑特价。 目的地+ NCO(数控振荡器)。 电池相位40位,正弦-12位。 两个寄存器控制正弦频率,并行和串行控制。 输出是并行的。

- 数模BMK。 大约400个门+十个类别的DAC。 具有电流输出的7位正弦发生器。

- 数字BMK。 1500至3000个阀门。 多路复用通道GOST 26765.52-87的各个端子。

- 数字BMK。 大约500个登机口。 一个八通道发电机,用于控制变压器的初级绕组。

- 数字BMK。 大约3000个登机口。 8位总线的多数电路。

不幸的是,市场的具体情况导致了BMK的绝大多数发展对公众仍然未知的事实。 公开数据不能清楚地说明速度,小册子中提到的数字也模棱两可。 但是,对于了解技术的任务来说,并不需要很多,并且已经有了一些经验,对特定方案的复杂性进行近似估计要容易得多。

6.开发过程

让我们继续进行最有趣的事情。 我们拥有:BMK,用于约3k个具有通道架构的阀(1个阀= 2个CMOS晶体管),在一个金属层和一个多晶硅子层中进行布线; 热情 批准企业管理以进行员工自我培训。

未来晶体的想法源于无所事事,也就是说,通过阅读一个论坛,尤其是在讨论用于计算正弦代码的电路紧凑解决方案的讨论中。 这个话题对我来说似乎很有趣,因此我决定看看在这个方向上可以做什么。

现在让我们看看做了什么,没有做什么,有什么错误和有什么结论。

6.1设计

表面研究表明,存在一种用于计算正弦值的算法,该算法从数学运算中仅需要求和,减法和向右移位。 事实证明,这不仅是一种算法,而且是一个称为CORDIC(坐标旋转数字计算机)的整个家族。 那些对算法的操作细节感兴趣的人可以参考本文结尾处的引用列表,但是我只会澄清一下,使用这种算法不仅可以计算正弦值,还可以计算余弦,反正切,乘和除参数以及计算一些双曲函数。

在研究了许多关于该算法的出版物并将这些知识系统化之后,我发现您可以尝试在容量约为3k的BMK上实现该算法。

那么,我们最终在电路架构中会得到什么呢?

- 用于计算正弦的扩展流水线CORDIC算法。

- 内部数据总线中的4个额外位可补偿舍入误差。

- 11位相位值累加器。

- 相位增量由并行总线设置。

- 输出数据格式:7位+符号,并行总线。

一切似乎都很好,但是如果您不补偿舍入误差会怎样? 这是什么(比较内部总线11位和8位):

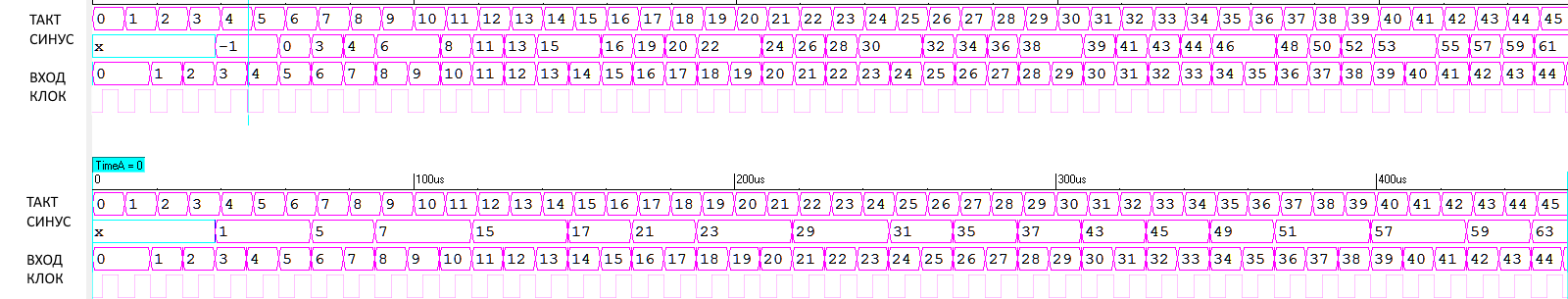

图3.分别使用11位和8位内部总线时,CORDIC算法的输出比较。

如果您注意数据的第二行,则会发现舍入误差会有效降低计算质量。

如果将来我们将此芯片连接到7位DAC,我们将获得一个完全合适的正弦发生器(我们认为DDS-直接数字合成)。 在这种情况下,我们将有机会对正弦波进行频率调制,但不会进行相位调制。

通常,使用小型BMC的路线与当前设计路线有些不同。 如果您考虑一下,差异将变得显而易见:在如此小的阀门体积下,有必要非常高效地使用每个阀门,而现代设计的主要范式根本就不是。 她说,该产品在每个阶段都应在体系结构上与自动化测试,验证,测量的现代系统兼容。 在这种情况下,作为必要的开销,阀效率问题仍然不在括号内。 确实,在动态发展的生产技术时代中,关于效率的思考是多余的。 因此,当(并且如果)我们仍然达到物理极限并停止增加晶体上晶体管的密度时,使用面积效率的问题将完全解决。 好吧,对于小型BMK,它们已经处于全高状态,因此得出以下结论:在小型坦克的BMK中,您可以并且应该使用复杂的设计,并使用各种棘手的块生成方案,各种闩锁,反馈和其他方式,以便在现代路线中使用一个高级工程师会伤了他的手。

使用这些东西的主要问题是使用它们,工程师必须清楚地知道他在做什么以及为什么。 但是,如果有理解,那么收获将是巨大的。 如果没有理解……那么,您可以用一百万种不同的有效方法射击腿部。

在我的情况下,设计路线是什么样的:

- 手动绘制为图书馆项目图

- 估计电路体积

- 处理电路,直到电路体积超过BMK容量的80%

- 这也包括新库元素的创建,它们的测试以及与设计路线的集成方面的工作。

- 制定电路测试

- 手动电路追踪

这里经验丰富的设计师可能会立即反对错过了几个重要步骤,但我真的忘了提及任何事情。

手动设计很好地显示了质量组件库的重要性。 电路的第一个变体不能简单地通过逻辑量来适应晶体,但是在通道BMC的情况下-布线穿过位于晶体管“行”之间的通道-互连约占电路体积的30%。 因此,我必须根据在此特定项目中获得的拓扑结构,对该库进行一些扩展。 这种方法可以节省大量的登机口,甚至可以或多或少地自由铺设所有路线。

最终的晶体填充率为72%,另外三分之一的晶体进入布线。 然后将文件转移到工厂,然后我返回到当前的工作项目。

使用“手动”设计方法时,必须记住以下几点:

- 您不能基于库元素的功能而盲目使用它们。 有必要在晶体管级别研究该元素是数字还是模拟组成的。 无论是纯粹的CMOS逻辑,还是TG或其他功能,他在输入和输出方面的承受能力是什么?

- 有必要考虑和协调元素的力量及其负载。

- 如果您有同步触发器,则需要用相等功率的信号对其进行时钟控制。

- 如果您使用某种信号而没有中间放大,并且负载在许多用户上,则该信号可能会非常失败。 在正常情况下,这可能微不足道,但在测试WWF(外部因素)时至关重要。

没有任何建模系统可以取代您自己的大脑。 通常,如果您自己不了解电路的工作原理,则无法运行仿真。

6.2测量

测量晶体的一个极其重要的阶段是其测量。 可以区分三种类型的测量:技术,功能,电气。 第一个证明工厂没有停工,并且晶体在技术上正确制造。 后者验证了理论(即建模)与实践(真实晶体)的融合。 , : , , . , , . , - . , . — , — . , … , , . .

, . , Fairchild 80- USB, . FORMULA "", . HP - Unix' . National Instruments , , , (). Agilent, . , ?) .

, -, , . , , , , Fairchild, , NI. , . - , , .

, , :

- , .

- . , .

- "" .

- , , , .

- .

- :

- /, , . /.

- , .

- , – . .

- , «» , .

- , .

, , .

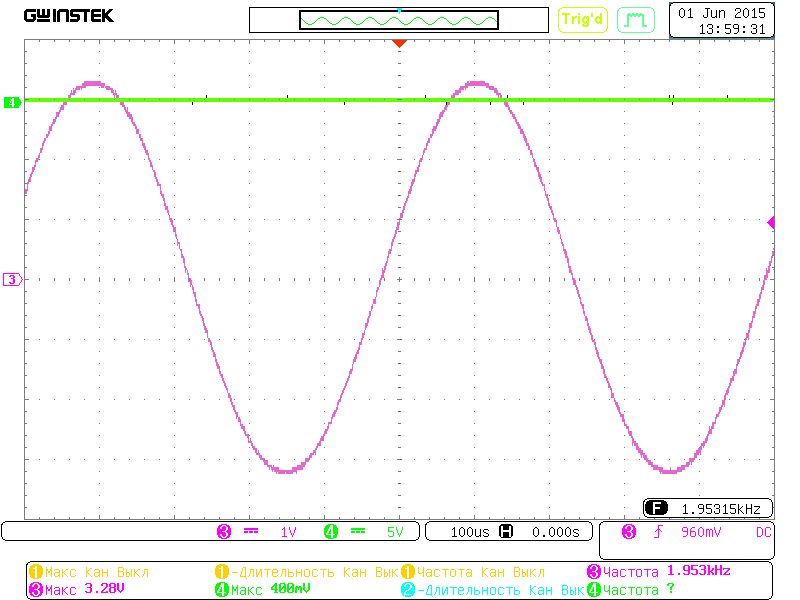

. 4 (!) . , , . , ?) " ".

4. .

, . , , . 80 , , , , 8- .

, . :

5.

6.

, , .

, — . , . 8- . .

6.3

?

- ;

- NCO(numerically controlles oscillator);

- , , NCO ROM(cROM);

- ;

- :

- , ;

- ;

7. , HRT.

:

- — 83%.

- 14

- 11

- (sin & cos, 12 )

- 16

, , ? , . , - .

, . , . , — . .

7. ?

.

.

30 000 100 2. , " " . , , Setup&Hold, , Verilog' , , , — , , . , — , , , … . — , .

. .

-

MIT Massachusetts Institute of Technology

UZH Universität Zürich

ASIC Application specific integrated circuit

-- []

CORDIC Coordinate Rotation Digital Computer

-

NCO Numerically controlled oscillator

ROM Read-only memory

cROM Compressed ROM

文学作品

- CORDIC IP Block Design, Vitaliy Kuhar, Stockholm, Sweden 2008

- CORDIC. , . . , . .

- Comparison of parallel and pipelined CORDIC algorithm using RCA and CSA, Guerrero, Meloni

- CORDIC for dummies.pdf

- Sine/Cosine using CORDIC Algorithm, Prof. Kris Gaj

- Lecture_cordic.pdf