你好

本文回顾了虚拟内存系统体系结构ARMv7。

扰流板方向此处不考虑缓存,DMA,LPAE等的细微差别。 有关更详细的描述,请参阅文章末尾的文献。

引言

虚拟内存系统执行多项任务。 首先,它允许您将用户进程放置在彼此隔离的独立内存空间中。 这使您可以提高系统的可靠性,一个进程的错误不会影响其他进程的操作。 其次,操作系统可以为进程提供比系统更多的内存。 未使用的内存页面被推入永久存储,然后从那里加载必要的页面,从而形成了比实际更多的内存幻觉。 第三,连续的虚拟空间使编写定制软件更加容易。 所有进程都在同一空间中执行,OS向它们隐藏系统中的实际内存配置。

定义

本文中使用以下定义:

虚拟地址-处理器内核使用的地址。 堆栈指针,指令计数器,返回寄存器使用虚拟地址。

物理地址-处理器总线上的输出地址。

页面是寻址虚拟内存的单位。

部分-页面的类似内容,具有较大的尺寸。

帧是物理内存寻址单元。

页表-用于翻译地址的记录数组。

ASID是地址空间标识符。

TLB-地址快速转换的缓冲区。

MMU是内存管理单元。

TLB

TLB是一个非常快速的硬件缓冲区,其中包含最新地址转换的结果。 转换页面地址和当前ASID的内核请求到达TLB。 如果那里有一个有效的条目,则检查访问此内存的权限,并将访问方法和相应的帧地址返回给MMU。 如果内存访问被拒绝,则将引发硬件异常。 如果发生了TLB未命中(未找到记录),则TTBCR进一步的行为区分大小写。 可以在页表中进行搜索,或者引发异常。

重要的是要注意,在处理页表时,必须正确重置TLB,因为 不相关的信息可以存储在此处。

在TLB中更新条目对循环编程器是透明的。

也可以在TLB中上载并保护某些条目,以防止其拥挤。

图1. TLB

图1. TLB页表

ARMv7是32位体系结构,因此我们有4GB的可寻址虚拟内存。

页表分为两个级别-L1和L2。

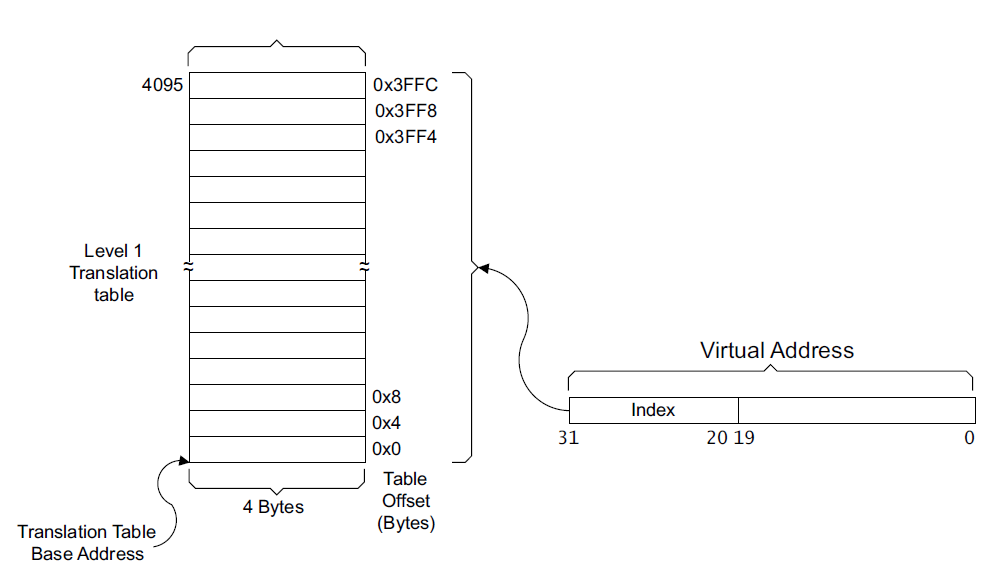

表L1描述了所有4GB的地址空间。 它由4096个32位记录组成,每个记录描述1 Mb。 该表中的条目由虚拟地址的高12位选择。

图 2搜索表L1中的条目

图 2搜索表L1中的条目表L1位于物理内存中,并与16KB边界对齐。 这些条目有4个选项:用于描述页面,部分和超级部分。 好吧,一条空记录,用于尚未映射的内存。

图 L1中的3种条目类型

图 L1中的3种条目类型位0和1表示记录类型00b-Fault,01b是页描述符,10b是节描述符(和超节)。

如果对物理内存进行了分页,则表L1将存储表L2的地址(物理,对齐为1Kb)。 位9由制造商(实现定义)确定,位[8:5]-用于域机制(在ARMv7中已弃用),SBZ-零。

如果我们决定将内存分为几部分,则必须在L1中写入相应的物理地址。 本节直接涉及对齐的1MB物理内存区域。 不需要表L2。 Supersection是分区的一种特殊情况,L1表中的条目应重复16次,物理和虚拟内存分配块的对齐方式也为16 MB。

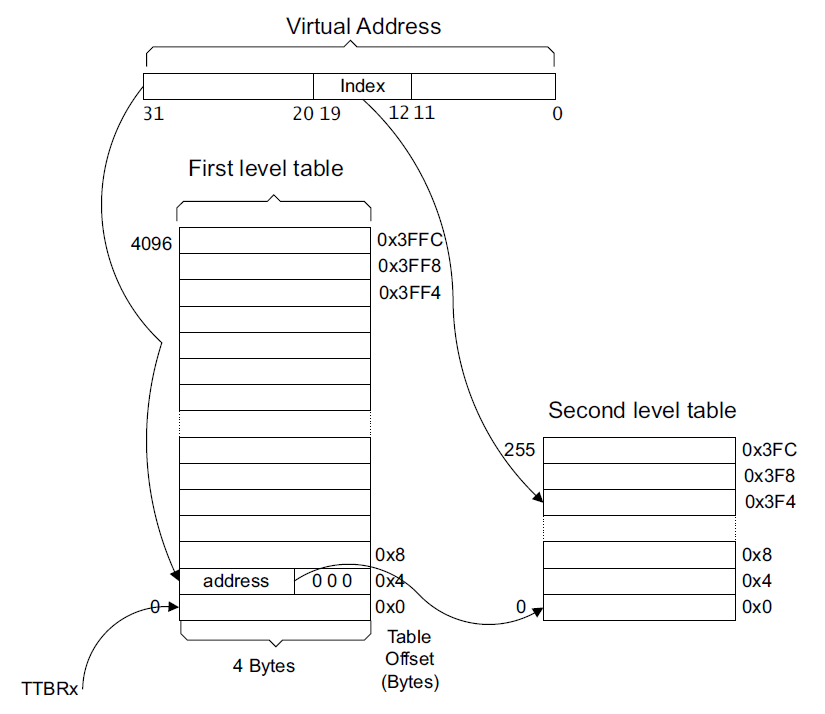

表L2由256个32位条目组成。 它应对准1Kb。

图 4在表L2中搜索条目

图 4在表L2中搜索条目表L2中的索引由虚拟地址的平均8位[19:12]形成。 每个表条目都包含框架的地址。

图 L2中的5种条目类型

图 L2中的5种条目类型页面可以有两种大小:64Kb(大页面)和4Kb(小页面)。

AP和APX位设置了特权/非特权模式(内核/用户)的读/写许可权。 TEX,C,B,S位负责存储器的类型,其缓存和读写缓冲。 nG-nonGlobal位允许访问所有进程或仅一个特定ASID的页面。

使用大页面会减少TLB中的条目数。 而不是16个条目(4Kb * 16 = 64Kb),那里将仅存储一个。 但是,必须在表L2中输入16个相同的条目。

寻址不同大小的块的能力,一方面允许以所需的粒度分配内存,另一方面,可以减少相对较慢的内存中对页表的调用次数。

寄存器

为了控制ARM体系结构中的系统(包括MMU),设计了特殊的CP15协处理器。 内存管理是其中的六个寄存器。 我们对其中的几个感兴趣-控件,TTBR0 / 1,TTBCR和ContextID。

在控制寄存器中,最低有效位负责打开/关闭MMU,一切都很简单。

一对寄存器TTBR0 / 1包含第一级表的物理地址。 在这些地址,MMU开始搜索所需的页面。

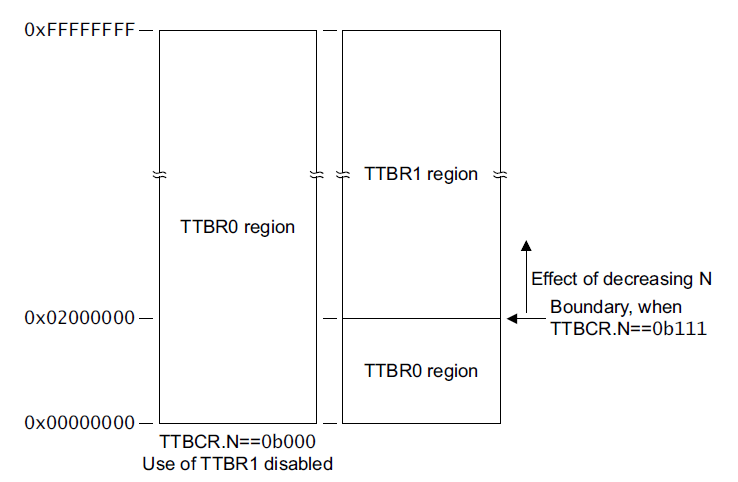

TTBCR寄存器允许您将整个地址空间分为TTBR0和TTBR1之间的两部分。 他们每个人都将广播其地址的一部分。 [2:0]位用于设置大小。 记录的数字(从0到7十进制)掩盖了虚拟地址的较早部分。 如果其值为“ 0”,则通过TTBR0广播所有地址。 如果为“ 1”,则将屏蔽31位地址,较低的2GB虚拟空间通过TTBR0,较高的虚拟空间通过TTBR1。 “ 2”-屏蔽了31位和30位,分别获得了1GB和3GB的划分。 因此,地址的下部可以用于用户应用程序,从而使TTBR0寄存器过载以进行新的处理,而上部可以留给系统使用。

图 6分割地址空间

图 6分割地址空间[5:4]位负责TLB丢失行为-在页表中搜索或发生异常。

ContextID寄存器包含当前进程的ASID字段。 更改上下文时,必须与寄存器TTBR0的内容一起更改。

地址翻译

将虚拟地址转换为物理地址的算法如下:

- 在TLB缓冲区中搜索请求的虚拟地址和ASID

- 如果TLB没有所需的地址,则在页表中执行硬件搜索

如果内核先前请求了虚拟页面,则它将存储在TLB中。 在这种情况下,MMU会将其从缓存中移出,无需执行任何操作。 如果是第一次请求该页面(或者它是从那里被迫退出的-TLB不是很大),那么将执行表L1-L2中的搜索。 因此,虚拟地址和物理地址的映射如下:

- 在寄存器TTBR0 \ TTBR1中,搜索表L1的地址。

- 虚拟地址的前10位构成表中的索引。

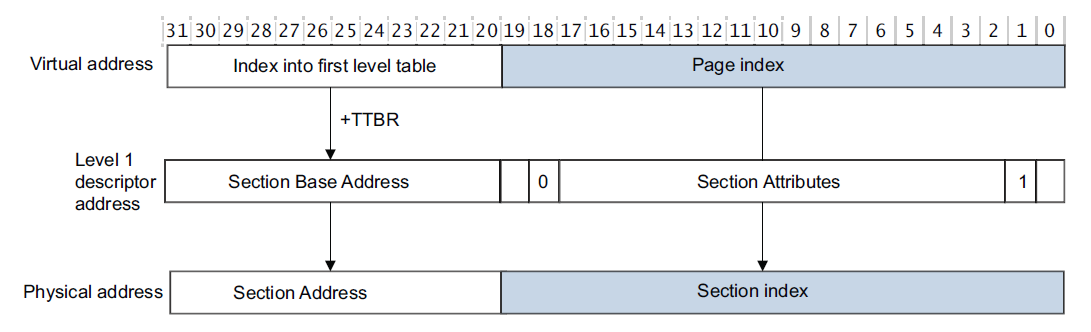

- a)如果记录对应于该部分(超级部分),则检查该部分的属性,如果一切正常,则结果物理地址由该部分(超级部分)的基地址和虚拟地址的低20(24)位组成。

扰流板方向 图 7上位地址翻译

图 7上位地址翻译

b)如果记录是表L2,则在其中继续搜索。 页面虚拟地址的中间部分构成表的索引。

扰流板方向 图 表L2中的8地址转换

图 表L2中的8地址转换

- 正在进行TLB更新

总的来说,虚拟内存子系统由以下部分组成:

- 多个CP15控制寄存器

- 包含地址转换规则的页表

- TLB-成功广播的缓存

- MMU是地址转换单元。

文学作品

《 ARM体系结构参考手册》 ARMv7-A和ARMv7-R版

ARM Cortex-A系列程序员指南