8月底,半导体集成电路制造商GlobalFoundries(与AMD合作)

停止开发7纳米制造工艺。 几个月前,英特尔

宣布再次推迟其10纳米芯片的发布。

我们将进一步解释做出这些决定的原因以及行业状况。

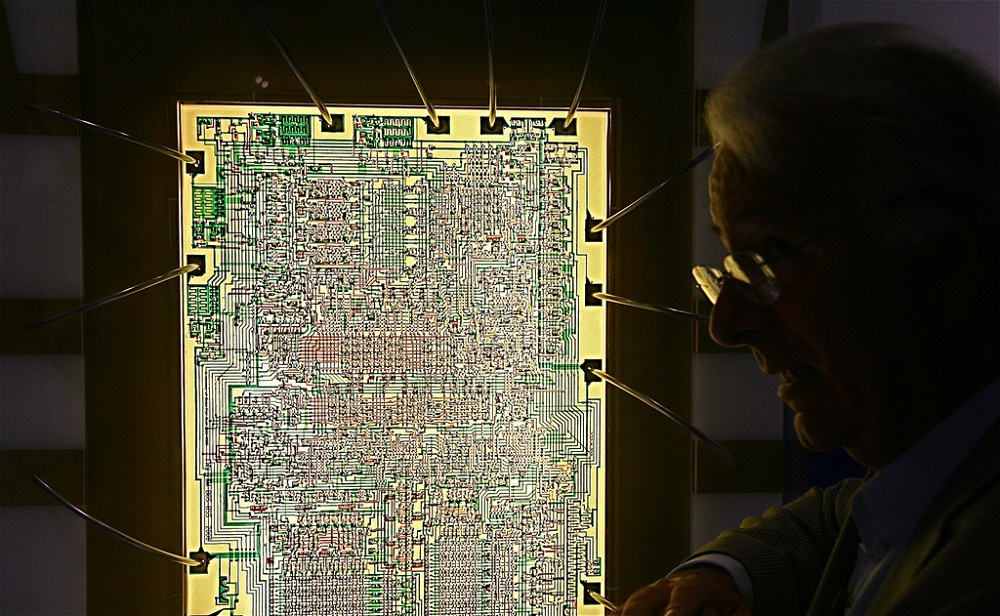

/图片Intel Free Press CC

/图片Intel Free Press CC关于工艺流程的几句话

芯片上的独立晶体管

通过光刻法形成。 在这种情况下,将称为光致抗蚀剂的光敏聚合物薄膜施加到硅基板上。 然后通过具有必要图案的光掩模对该光层进行光处理(产生所谓的曝光)。 在显影液中冲洗掉曝光的区域,然后蚀刻晶体。

公司正在减少工艺流程,以增加一个工件的产品数量并减少最终芯片的能耗。 制造商有机会提高芯片的速度,而尺寸保持不变。

长期以来,这种趋势(减少工艺流程)一直很合理。 但是现在,IT公司已经开始延迟甚至停止开发新的技术流程。 部分原因是设备价格上涨和高婚姻率。

有关情况的更多详细信息将在下面讨论。

为什么GlobalFoundries取消了7nm工艺

GlobalFoundries在全球八家工厂生产硅晶片。 该公司原定于2018年第二季度推出7纳米芯片。 但是,在预期发布的几周前,GlobalFoundries决定取消所有内容。

相反,该组织

将专注于针对

14LPP (低功耗增强版)和12LP(领先性能)的专门生产标准的开发,以及各种内置

存储设备的创建。

14LPP平台是基于3D

FinFET晶体管的14nm工艺的改进版本。 它使设备的性能提高了55%,功耗降低了60%(与28 nm相比)。

12LP是半导体的制造工艺,可满足AI系统,智能手机和汽车电子产品的需求。

根据CTO GlobalFoundries加里·帕顿(Gary Patton)的说法

,战略转向的原因不是技术问题,而是财务问题。 该公司已投资数十亿美元开发7纳米芯片。 使用浸没式光刻技术的第一代产品即将完成。 但是第二个和第三个(它们需要更深的UV范围以增加晶体管的密度)没有足够的资金。

随着7纳米的取消,GlobalFoundries停止了5纳米和3纳米制造工艺的开发。 由于做法的变化,GlobalFoundries将裁减其5%的员工,并审查与AMD和IBM的协议。 特别是,该公司将与IBM合作直至年底,然后停止研究新的技术流程。

还有谁推迟发展

另一个推迟采用新工艺发布芯片的组织是英特尔。 两年来,这家IT巨头一直

在大规模发布10nm电路。 这次,首批10纳米产品的销售开始已

移至 2019年底。

根据公司

代表的说法,延迟的原因是处理器的低产量。 据

信 ,该问题与多图案化技术和钴的使用有关。

产量增长速度低于计划。 从技术上讲,英特尔已经小批量供应10nm芯片。 例如,第一个Core i3-8121U(Cannon Lake系列的10纳米处理器)已经

可以在Lenovo笔记本电脑中使用。 但是,无需谈论芯片的批量生产。

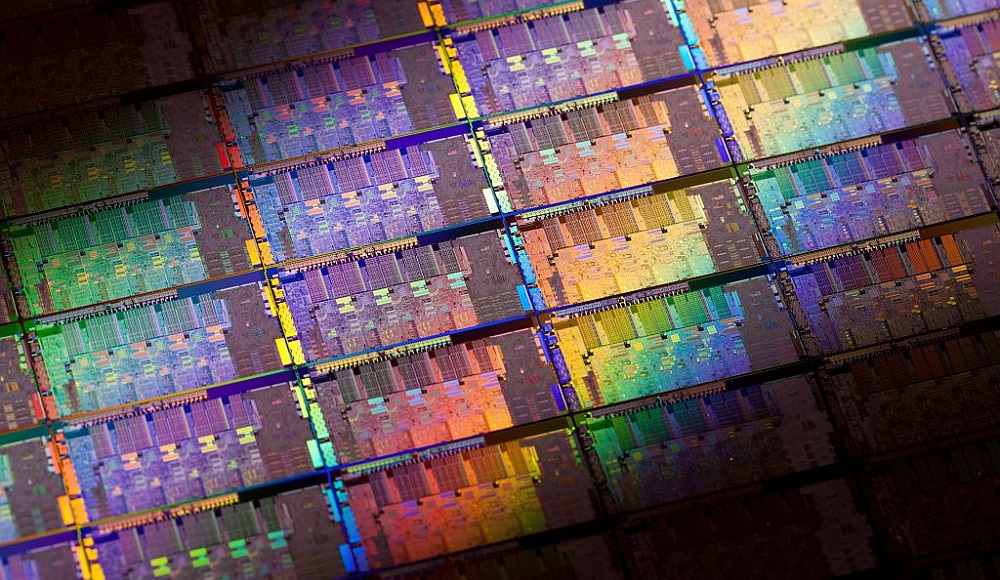

/图片Intel Free Press CC

/图片Intel Free Press CC其他市场参与者也不急于将新技术流程的开发投入生产。 迄今为止,联电已

决定采用14纳米制程技术,而三星则

承诺采用 7纳米制程,但也不得早于2019年。

主要原因

正如我们已经说过的那样,高昂的过渡成本是GlobalFoundries缩减其项目的原因之一。 根据Gartner的说法,她是主要角色。 据分析师称,开发7纳米技术的成本约为2.7亿美元。

用于

EUV光刻的设备,纳米片,诸如钌的奇异材料-所有这些东西都不便宜,但其中一些已经很难做到。 为了收回生产投资,每年

必须生产 1.5亿个芯片。 因此,在商业上不利于实施7、5、3和2纳米工艺。

而且,即使它们产生了微电路,性能的“疲惫”也并不总是很明显。 例如,高通公司

认为 5纳米制程在性能上不会大大超过7纳米,在其开发上将需要投资数十亿美元。

第二个原因是错误的可能性及其价格很高。 例如,10纳米英特尔制程技术供应的延误,给市值200亿美元的IT巨头之一“

吹了不少钱 ”。

高净值居民还

强调了半导体行业增长放缓的其他原因。 例如,一位用户认为减小晶体的尺寸对其冷却有不利影响。 因此,公司正在尝试投资开发更节能的技术,而不是减小晶体的尺寸(这是GlobalFoundries选择的途径)。

为什么仍需要更新

行业代表

认为 ,工艺流程仍必须减少。 这将确保AI,MO,5G网络和IoT的有效运行。 根据台积电开发人员的

初步计算 ,7纳米制程技术将使生产率提高30%,并且一半减少处理器的功耗(与10纳米相比)。

但是,半导体公司Lam Research的高级副总裁David Hemker

强调指出 ,该行业将需要新的解决方案来应对制造工艺日益复杂的问题。

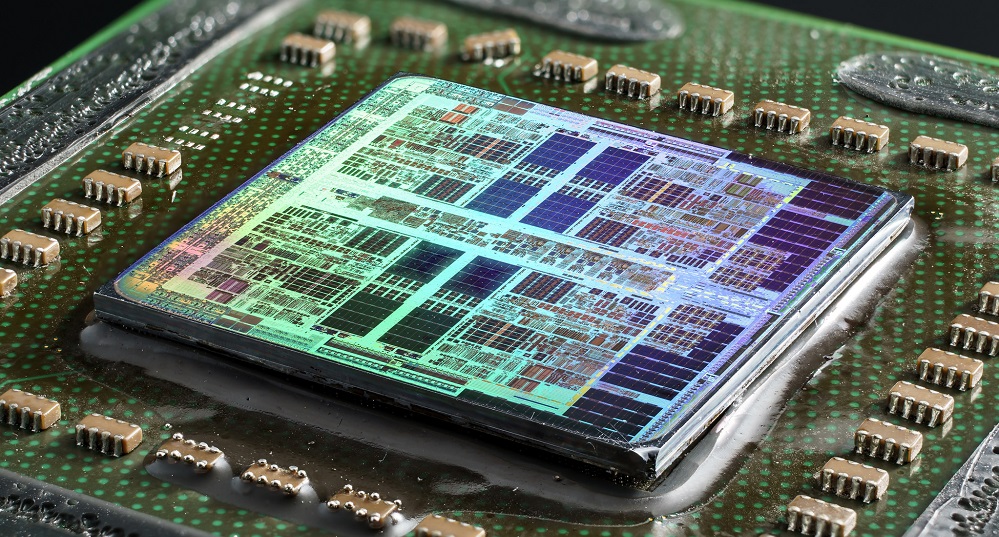

/图片Fritzchens Fritz PD

/图片Fritzchens Fritz PD到目前为止,EUV光刻

在芯片制造中会产生

太多缺陷 。 但是,如果我们继续改进技术,它

应该减少开发新技术过程

的时间和成本。

尽管生产困难重重,但一些行业代表已经对小于5 nm的工艺进行了预测,并讨论了此类芯片的发布时间。 因此,例如,也从事半导体生产的台积电(TSMC)已经

在计划开发3纳米和2纳米制程技术。 Imec研究中心与Cadence Design Systems一起甚至使用3纳米技术

开发了微处理器的测试样本。

因此,将来我们一定会看到这些技术的应用,只有这一刻比原先设想的要晚一点。

PS第一个公司IaaS博客的其他资源:

PPS来自我们Habré博客上的相关文章:

我们在IT-GRAD中的工作:• IaaS • PCI DSS托管 • Cloud-152