现代微电子技术-例如“十个小印第安人”。 开发和设备的成本是如此之高,以至于每迈出新一步,都会有人落败。 关于GlobalFoundries拒绝开发7 nm的消息之后,剩下了三个:TSMC,Intel和Samsung。 那么“设计标准”到底是什么?那么珍贵的7 nm尺寸在哪里呢? 而且他在那里吗?

图1.晶体管Fairchild FI-100,1964年。最早的串行MOS晶体管于1964年进入市场,正如老练的读者从图纸中可以看到的那样,它们

几乎与现代的现代晶体管没有什么不同-除了尺寸(请看导线上的比例尺)。

为什么要减小晶体管的尺寸? 这个问题最明显的答案是摩尔定律,该定律指出每两年芯片上晶体管的数量应增加一倍,这意味着晶体管的线性尺寸应减少两倍。 “必须”-根据Gordon Moore(和其他一些工程师)在七十年代的观察。 根据摩尔定律,还有许多其他因素构成了ITRS微电子技术路线图。 实施摩尔定律(也称为Dennard的小型化定律)的方法最简单,最粗糙的方法是,芯片上晶体管数量的增加不应导致功耗密度的增加,也就是说,随着晶体管尺寸的减小,电源电压和工作电流应成比例地降低。

流过MOS晶体管的电流与宽度和长度的比例成正比,这意味着我们可以保持相同的电流,并按比例减小这两个参数。 而且,减小晶体管的尺寸,我们还减小了栅极电容(与沟道长度和宽度的乘积成比例),从而使电路更快。 通常,在数字电路中,实际上没有理由使晶体管大于最小尺寸。 接下来,细微差别开始了,为了补偿电荷载流子迁移率的差异,逻辑p沟道晶体管通常比n沟道晶体管稍宽,相反,在存储器中,n沟道晶体管更宽,因此可以通过非互补键正常写入存储器,但实际上细微差别以及总体上-晶体管的尺寸越小-数字电路越好。

这就是为什么通道长度始终是微电路拓扑中最小的尺寸,也是最合逻辑的名称。

在此应注意,上述关于尺寸的推理对模拟电路无效。 例如,现在在我的计算机的第二台显示器上,有一对使用150 nm技术的匹配晶体管,每个晶体管的尺寸为8/1微米,共32个。 这样做是为了确保这两个晶体管的身份,尽管参数存在技术差异。 该区域是次要的。技术人员和拓扑学家具有典型拓扑大小的所谓的lambda系统。 这对于学习设计(如果没有记错的话,是伯克利大学发明的)和将设计从一个工厂转移到另一个工厂非常方便。 实际上,这是对典型尺寸和技术限制的概括,但是有些粗糙,因此可以在任何工厂中正常使用。 在她的示例中,查看芯片中元件的典型尺寸非常方便。 lambda系统的核心原理非常简单:

- 如果在两个不同的光刻掩模上的元素偏移具有灾难性的后果(例如,短路),则防止出现不一致的尺寸裕度应至少为两个λ。

- 如果元素的移动有不良后果,但不是灾难性后果,则大小边距必须至少为一个λ;

- 光罩窗口的最小允许尺寸为两个lambda。

从第三段开始,尤其是旧技术中的lambda是设计规范的一半(更准确地说,晶体管沟道长度和设计规范是两个lambda)。

图2.由lambda系统执行的拓扑示例。lambda系统在旧的设计标准上运行完美,使您可以方便地在工厂之间转移生产,组织第二芯片供应商并做更多有用的事情。 但是随着竞争的加剧和芯片上晶体管的数量的增加,工厂开始努力使拓扑结构更加紧凑,因此现在您无法满足与“干净” lambda系统相对应的设计规则,除非在开发人员独立进行粗化的情况下(考虑到生产可能性)芯片在不同的工厂。 但是,多年来,业界已经开发出一种直接连接的“设计标准=晶体管沟道长度”,这种连接成功存在直到晶体管达到数十纳米。

图3.晶体管的原理图部分。该图显示了传统平面(平坦)晶体管的非常简化的截面,显示了拓扑沟道长度(Ldraw)和有效沟道长度(Leff)之间的差异。 差异来自何处?

说到微电子技术,几乎总是提到光刻技术,而其他同样重要的技术操作则很少见:蚀刻,离子注入,扩散等。 等 在我们与您的对话中,提醒您扩散和离子注入是如何工作的并不是多余的。

图4.扩散和离子注入的比较。通过扩散,一切变得简单。 您需要事先(借助光刻)在其上施加图纸的硅片,用氧化硅覆盖不需要杂质的地方,并打开需要杂质的地方。 接下来,您需要将气态杂质与晶体置于同一腔室内,并加热至杂质开始渗透到硅的温度。 通过调节过程的温度和持续时间,可以实现所需数量和深度的杂质。

明显的扩散减法是,杂质以相同的方式(从一侧向下)渗透到所有方向的硅中,从而减小了有效沟道长度。 我们现在正在谈论的是数百纳米! 尽管设计标准的尺寸是几十微米,但一切都很好,但是,这种情况不会持续太久,扩散被离子注入所取代。

在离子注入期间,杂质离子束加速并被引导到硅晶片上。 在这种情况下,所有离子都沿一个方向移动,实际上消除了它们向侧面的扩散。 从理论上讲,当然。 在实践中,尽管距离比扩散时要短得多,但离子仍会散开一点。

然而,如果我们返回晶体管图形,我们将看到,由于这种小蠕变,拓扑和有效沟道长度之间的差异恰好开始了。 从原则上讲,她可以被忽略,但她并不是造成这种差异的唯一原因。 仍然存在短通道效应。 它们有五个,如果沟道长度接近各种物理限制,它们会以各种方式更改晶体管的参数。 我不会全部描述它们,我将介绍与我们最相关的-DIBL(漏极引起的势垒降低,漏极引起的势垒降低)。

为了进入阱,电子(或空穴)必须克服阱pn结的势垒。 栅极电压减小了该势垒,从而控制了流经晶体管的电流,我们希望栅极电压成为唯一的控制电压。 不幸的是,如果晶体管通道太短,漏极pn结就会开始影响晶体管,这首先会降低孔电压(请参见下图),其次,晶体管两端的电压不仅会影响栅极电压漏极pn结的厚度与漏极处的电压成比例地增加,因此缩短了沟道。

图5.漏极引起的势垒降低(DIBL)效果。

资料来源-维基百科。此外,沟道长度的减小导致电荷载流子开始自由地从源极流到漏极,绕过沟道并产生泄漏电流(下图中的不良电流),这也是静态功耗,缺少它是CMOS早期成功的重要原因之一技术,与当时的双极竞争者相比具有抑制作用。 实际上,现代技术中的每个晶体管都有一个与其并联的电阻,其值越小,沟道长度越小。

图6.短通道技术泄漏导致的静态功耗增加。

来源-Synopsys。图7.不同设计标准下微处理器的静态功耗比例。

资料来源-B. Dieny等。 等,“自旋传递效应及其在自旋电子元件中的应用”,国际纳米技术杂志,2010年现在,如您在上图中所看到的,静态功耗大大超过了动态功耗,并且是创建低功耗电路(例如,可穿戴电子设备和物联网)的重要障碍。 实际上,大约在这成为一个重要问题时,就开始采用设计标准进行市场营销,因为光刻技术的发展开始超过物理技术的发展。

为了解决800-32纳米设计标准下短通道的不良影响,发明了许多不同的技术解决方案,我将不对其进行全部描述,否则本文将发展为非常不雅的尺寸,但是在新的步骤中,我不得不引入新的解决方案-其他对靠近pn结的区域进行掺杂,进行深度掺杂以防止泄漏,将晶体管中的硅局部转变为硅锗...在减小晶体管尺寸方面没有一步之遥。 哦

图8. 90 nm和32 nm技术中的有效通道长度。 晶体管以相同的比例拍摄。 图中的半圆是漏极(LDD,轻掺杂漏极)的附加弱匹配的一种形式,旨在减小pn结的宽度。

来源-Synopsys。在从90 nm过渡到约28 nm的过程中,典型的金属化尺寸和元素之间的距离与设计规范的降低成比例地减小,也就是说,下一代的典型尺寸是上一代产品的0.7(因此,根据摩尔定律,面积减小了两倍)。 同时,通道长度与上一代相比最大减少为0.9,有效通道长度几乎完全没有变化。 从上图可以清楚地看出,晶体管的线性尺寸从90 nm改变为32 nm并没有发生三倍的变化,所有技术人员的工作都是围绕减少快门重叠和掺杂区域,以及围绕控制静电泄漏进行的,这是不允许的。通道更短。

结果,两件事变得清晰了:

- 在没有技术突破的情况下低于25-20 nm不起作用;

- 市场营销人员越来越难以根据摩尔定律来描绘技术进步的景象。

摩尔定律通常是一个有争议的话题,因为它不是自然定律,而是对某家公司历史上某些事实的经验观察,可以推断整个行业的未来发展。 实际上,摩尔定律的普及与英特尔市场营销者有着千丝万缕的联系,后者成为了他们的旗帜,并且实际上推动了该行业的发展多年,迫使其遵守摩尔定律,也许值得一等。营销人员发现情况的方式是什么? 非常优雅

晶体管通道的长度很好,但是如何从该通道中估算出增益,从而过渡到新的设计标准? 早在很久以前,该行业就使用了六晶体管存储单元,这是最流行的微处理器构件。 正是这些单元通常由一个高速缓存存储器和一个寄存器文件组成,它们占据了半个晶体,这就是为什么总是小心翼翼地将六晶体管单元的方案和拓扑舔到极限的原因(通常是这样做的特殊人员),因此这是一个非常好的措施堆积密度。

图9.六晶体管静态存储单元的示意图。图10.六晶体管静态存储单元的不同拓扑选项。 资料来源 -G. Apostolidis等。 等,“ 32nm技术中的6T SRAM单元架构的设计和仿真”,《工程科学与技术评论》,2016年因此,长期以来,在技术描述中,设计标准的数量伴随着第二个数字-存储单元的面积,从理论上讲,这应该从通道长度得出。 然后有一个有趣的概念替代。 根据摩尔定律,当直接缩放停止工作并且通道长度每两年停止减少时,市场人士猜测,有可能不是从设计规范中得出存储单元面积,而是从存储单元面积中得出设计规范的数量!

也就是说,自然地,“我们曾经拥有65 nm的沟道长度和X的存储单元区域,现在沟道长度为54 nm,但是我们挤压了金属化层,现在单元区域变为X / 5,这大致对应于从65 nm到28 nm的过渡。 那么,让我们告诉大家我们有28 nm的设计标准,而我们不会告诉任何人有关54 nm的通道长度吗?” 公平地说,``金属化带刺''也是一项重要的成就,并且在晶体管本身的小型化,最小金属化宽度,与晶体管的接触尺寸或拓扑结构上的某些其他图形出现问题之后的一段时间内,这些都与规定的设计标准相对应。 但随后的发展始于FinFET晶体管,其关键尺寸与光刻分辨率无关,晶体管的小型化速率最终与其他所有因素均发生分歧,存储单元面积仍然是唯一正常的数字,据此我们得知“ 10”,“ 7”和“ 5”纳米。

图11.英特尔14纳米和10纳米技术的比较。

资料来源-英特尔。这是这种“新规模”的一个很好的例子。 我们显示了存储单元中的特征大小如何变化。 参数很多,但晶体管通道的长度和宽度一无所知!

他们如何解决不可能减少通道长度和控制技术泄漏的问题?

他们发现了两种方法。 首先是在额头上:如果泄漏的原因是植入的深度较大,让我们减少它,最好是从根本上减少它。 绝缘体上的硅(SIC)技术早已为人所知(这些年来一直活跃使用,例如,在130-32 nm AMD处理器,90 nm Sony Playstation 3机顶盒处理器以及射频,电源或太空电子设备中使用)随着设计标准的降低,她又迎来了第二风。

图12.使用常规体积和FDSOI(完全耗尽的SOI)技术制造的晶体管的比较。

来源-ST微电子 。如您所见,这个想法不仅仅是优雅的-氧化物位于非常薄的活性层下面,消除了藤蔓上有害的泄漏电流! 同时,由于pn结电容的减少(漏极立方体的五个侧面中的四个被去除了),速度提高了,功耗降低了。 这就是为什么现在积极宣传FDSOI 28-22-20 nm技术作为物联网微芯片的平台的原因-消耗量实际上减少了数倍,甚至减少了一个数量级。 但是,这种方法将来允许将常规的平面晶体管缩放到14-16 nm的水平,而体积技术将不再允许这种尺寸。

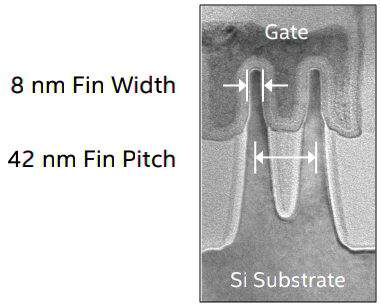

尽管如此,FDSOI并没有特别降低到14 nm以下,并且该技术还存在其他问题(例如,SOI衬底的高昂成本),因此业界寻求了另一种解决方案-FinFET晶体管。 FinFET晶体管的想法也很优雅。 我们是否希望通过栅极控制漏极和源极之间的大部分空间? 因此,让我们在四周用百叶窗包围这个空间! 好吧,不是全部,三个就足够了。

图13. FinFET结构。

资料来源-A. Tahrim等人,“用于16纳米制程下阈值区域的1位FinFET全加法器单元的设计和性能分析”,纳米材料杂志,2015年图14.平面晶体管和FinFET上不同加法器选项的功耗比较。

资料来源-A. Tahrim等人,“用于16纳米制程下阈值区域的1位FinFET全加法器单元的设计和性能分析”,纳米材料杂志,2015年在FinFET中,通道不是平坦的,而是位于基板表面的正下方,但形成垂直鳍(鳍为鳍),并在表面上方突出,并在三个侧面被百叶窗围绕。 因此,通过闸门控制漏极和源极之间的整个空间,并且大大减少了静态泄漏。 第一批量产的FinFET是英特尔,其设计标准为22纳米,其余的则由其他顶级制造商提拔,其中包括诸如Global Foundries(前AMD)之类的KNI辩护律师。

FinFET, , , FinFET c , , , « », .

15. (5T-9T) FinFET. — M. Ansari et. al., «A near-threshold 7T SRAM cell with high write and read margins and low write time for sub-20 nm FinFET technologies», the VLSI Journal on Integration, Volume 50, June 2015.FinFET. , ? , , , - . ?

16. 14-16 .

— the ConFab 2016 conference proceedings., 16 FinFET , 20-25 , . , . , : , , — , . : Intel 16 nm ( !) .

17. 14 Intel.

17. 14 Intel.

— wikichip.org, , , , , . , , - , , , , , , , , -. , , TSMC 7 , Intel 10 , , 7 TSMC 10 Intel — , .

? , . , « ?» , , , . 450 , EUV- ( ), , , . , , , . , TSMC

, 3D-. «» 3D-,

, , , .