四倍数据速率(QDR-IV)是用于网络应用程序的高性能内存标准,是下一代网络设备,通信设备和计算系统的理想选择。

QDR-IV SRAM具有内置的错误检测和纠正(ECC)单元,以确保数据完整性。 该单元能够处理所有单位内存错误,包括由宇宙射线和alpha粒子引起的错误。 结果,内存模块的程序错误率(SER)不会超过0.01个故障/ MB。 QDR-IV配备了可编程的地址奇偶校验功能,可确保地址总线上的数据完整性。

QDR SRAM存储器的独特功能:

- 集成的纠错模块可确保数据完整性并消除软件错误

- 这些模块有两个版本:QDR-IV HP(数据速率1334 Mtrans / s)和QDR-IV XP(数据速率2132 Mtrans / s)

- 两个独立的双向DDR1内存数据端口

- 总线反转功能可在连接输入和输出线时降低噪声

- 集成协商方案(ODT)降低了电路板的复杂性

- 偏斜训练可改善信号捕获的时机

- I / O信号强度:1.2V至1.25V(高速收发器逻辑(HSTL)/端接逻辑(SSTL)),1.1V至1.2V(POD2)

- 361引脚FCBGA3封装

- 总线宽度:x18,x36位

引言

DDRx向导是HyperLynx中易于使用的工具,可让您批量控制时间波形并分析标准DDR JEDEC协议的信号完整性。 DDRx向导既可以在根据“假设”场景进行的拓扑前分析阶段,也可以在完全跟踪的板上启动。 此外,该工具还允许您导入由主要芯片供应商创建的大多数模型格式。

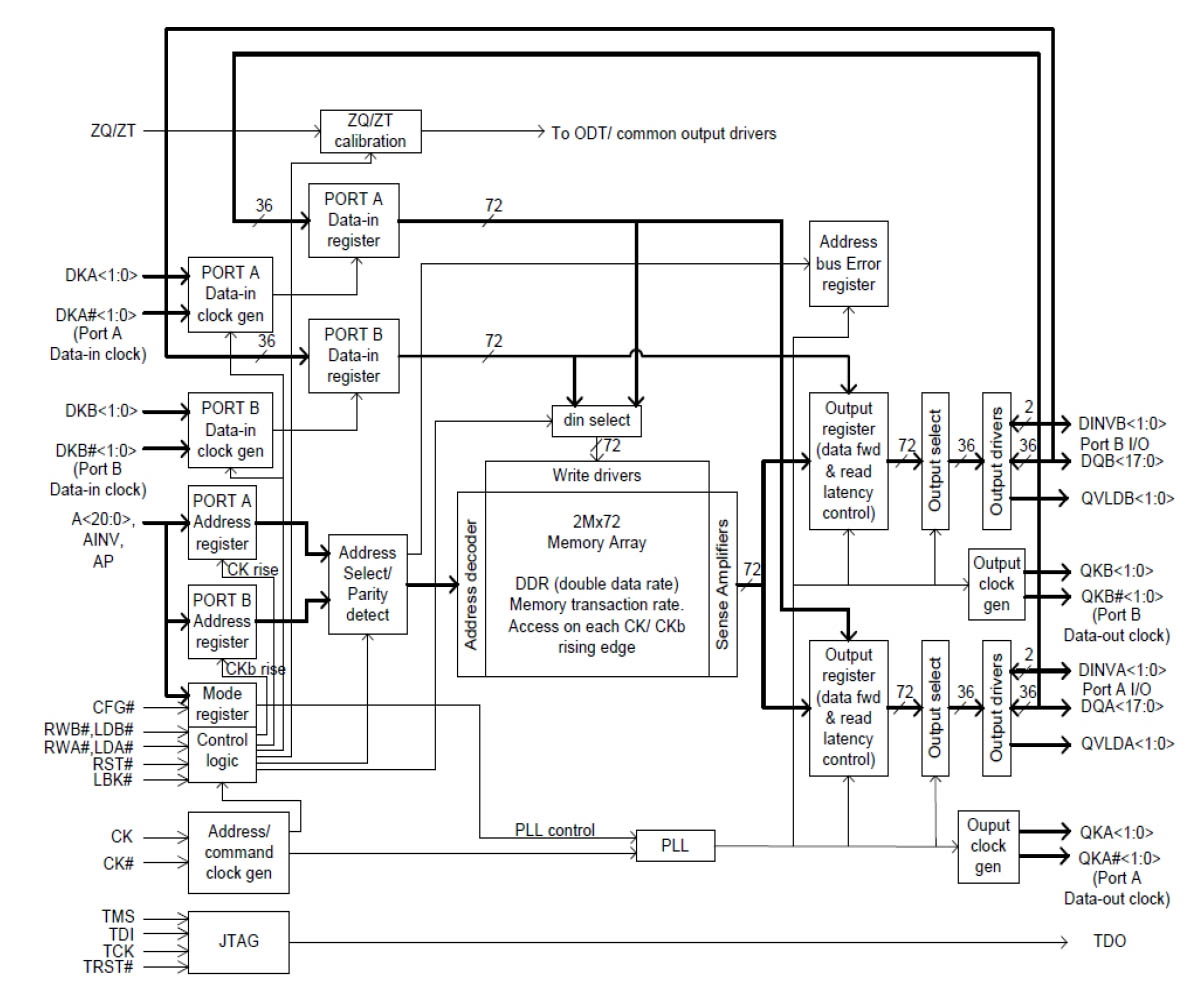

DDRx向导使您可以检查内存总线的所有位是否符合信号完整性,以及是否符合信号之间的同步要求。 本文将详细介绍使用交互式助手来分析实现QDR4协议的项目(图1)。

图 1.在模块CY7C4142KV13的示例上,QDR的内部体系结构(可单击)

图 1.在模块CY7C4142KV13的示例上,QDR的内部体系结构(可单击)首先看一下HyperLynx DDRx向导中的QDR-IV

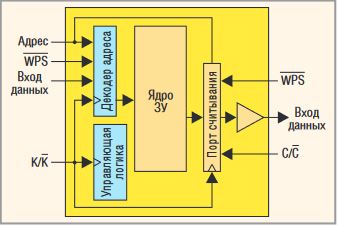

QDR-IV协议定义了两个单向的数据选通信号对:一个用于读取数据,另一对用于写入,它们支持彼此独立的操作以及同时的读写操作,并且端口可以在不同的频率下工作(图2)。 因此,完全消除了故障的风险。

图 2. QDR SRAM体系结构中单独的读写端口的可用性

图 2. QDR SRAM体系结构中单独的读写端口的可用性对于此协议,DDRx向导将使用单独的门来读取和写入数据。 QDR IV通常使用x36或x18位总线来实现(见图3a和3b)。

DDRx向导通过三个步骤启用QDR-IV仿真:

由于可以独立于数据读/写检查执行地址/控制总线检查,因此通过将此步骤与任何数据测试步骤结合使用,可以节省您的时间。 下面介绍了这些测试的所有三种方案。

技术特点

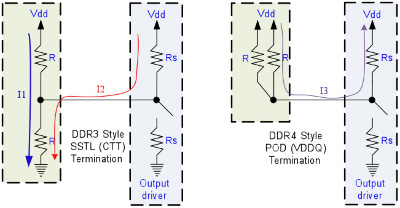

QDR-IV支持伪开漏(POD)技术和Stub系列终端逻辑(SSTL)终端逻辑(图4)。

图 4. POD和SSTL之间的区别

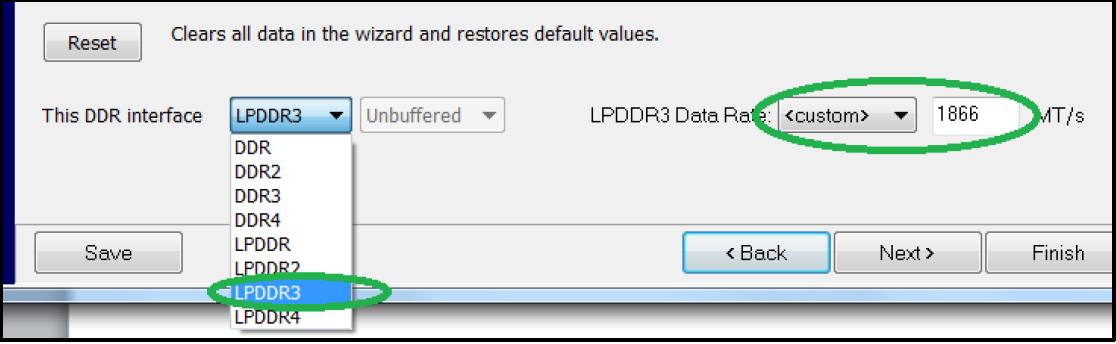

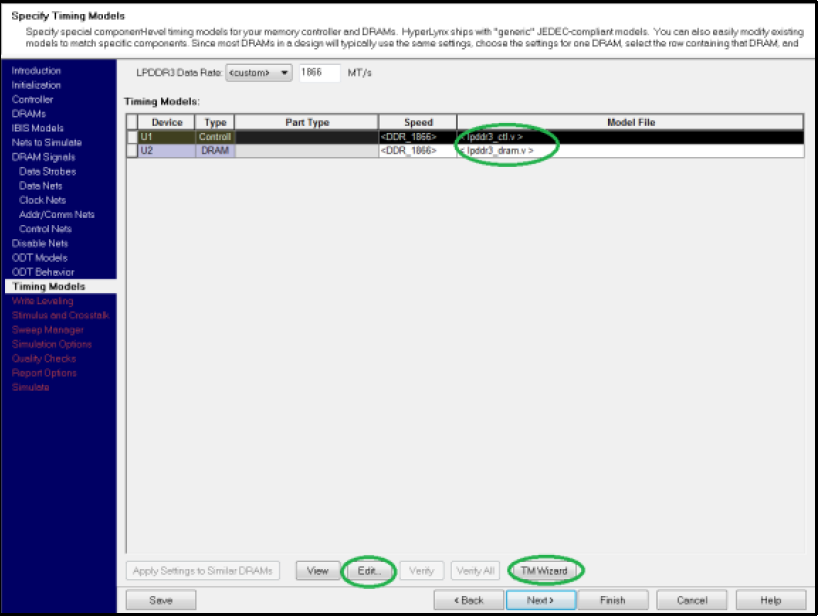

图 4. POD和SSTL之间的区别不管使用哪种逻辑标准,请选择

LPDDR3作为技术(图5),因为不支持

Vref训练 ,这与DDR4的POD模块一样。 而是使用Vref和Vinh / Vinl固定值,类似于DDR3和LPDDR3。 由于QDR-IV对地址信号(例如LPDDR3)使用双重数据速率,因此建议您选择此选项。 接下来,输入用户数据传输速率,例如1866 MT / s或2133 MT / s,其中MT / s是每秒的兆传输数(每秒的兆传输)。

图 5.标准逻辑的选择

图 5.标准逻辑的选择数据信号:读取操作

对于数据信号读取操作,DRAM将与差分选通QK信号一起控制DQ信号。 因此,设置着重于数据读取操作,并将必要的电路(信号)分配给相应的QK门。

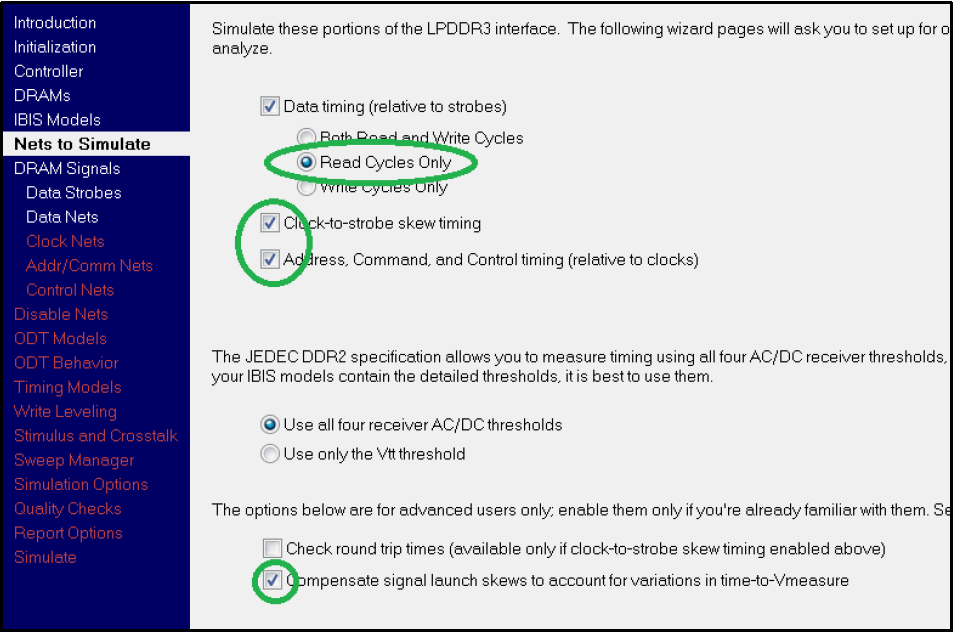

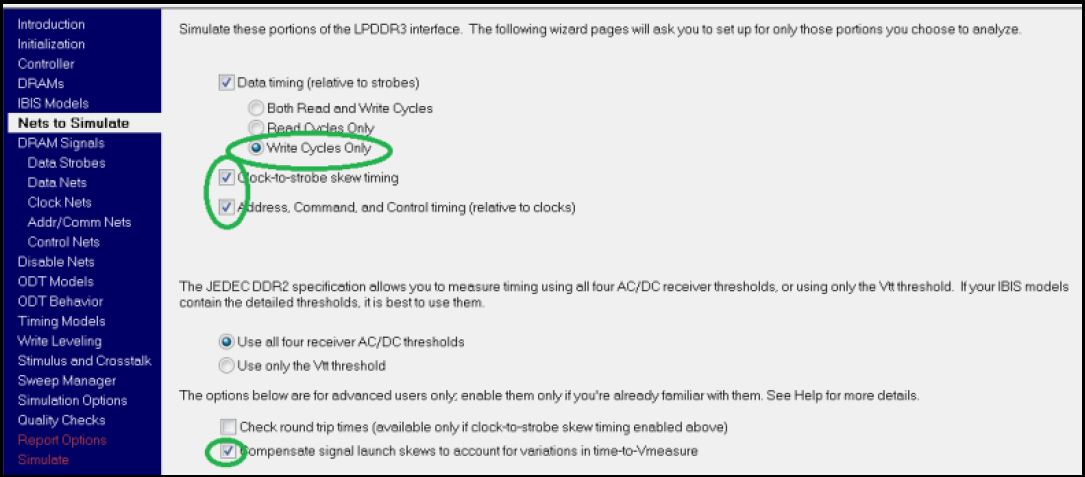

在“

要模拟的

网络”部分(图6)中,选中“

仅读取周期 ”框。 “

选通时钟”和“地址”复选框是可选的。

另外,请检查“

补偿信号启动偏斜”的安装,

以解决“测量时间”复选框的变化 。

图 6.读取数据

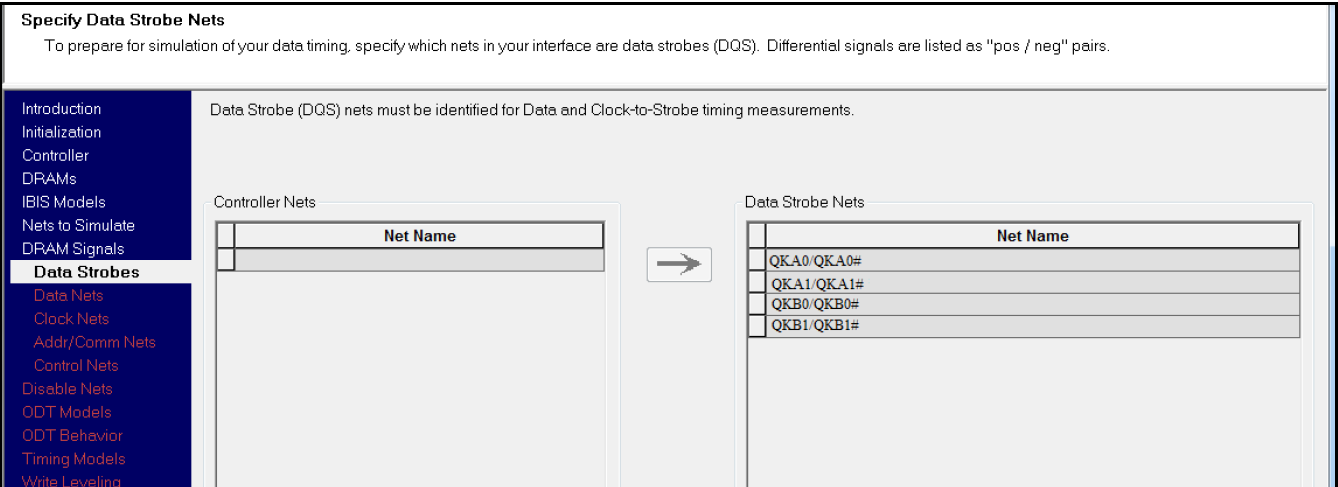

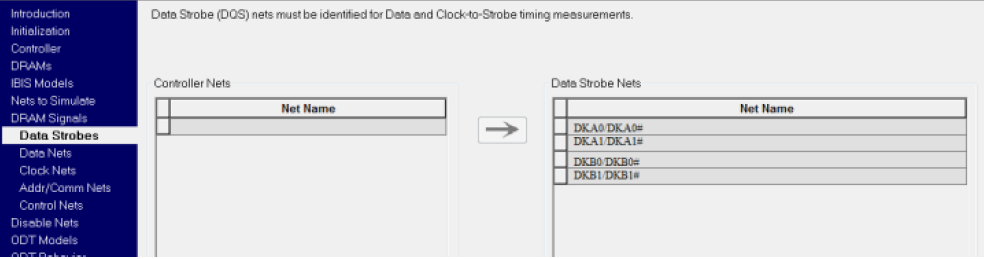

图 6.读取数据确保选择了所有必需的数据选通脉冲(图7)。

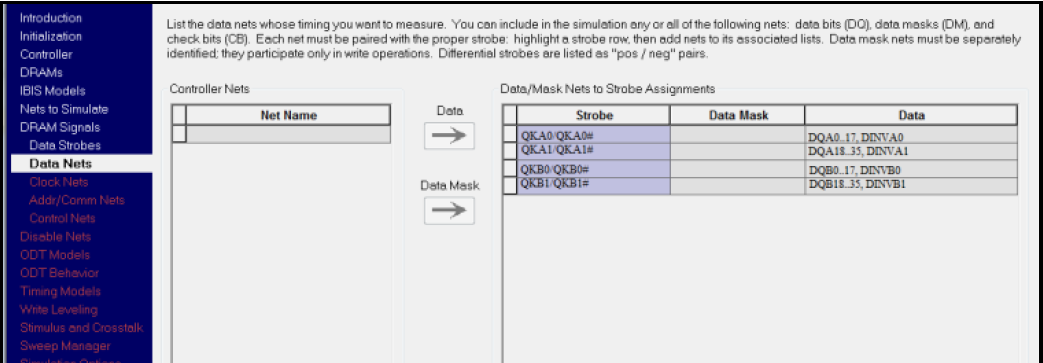

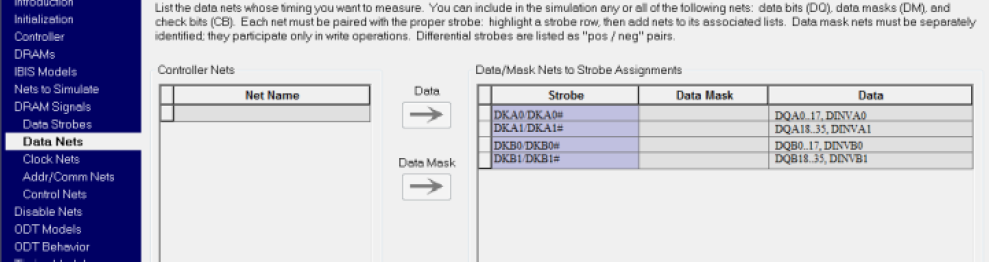

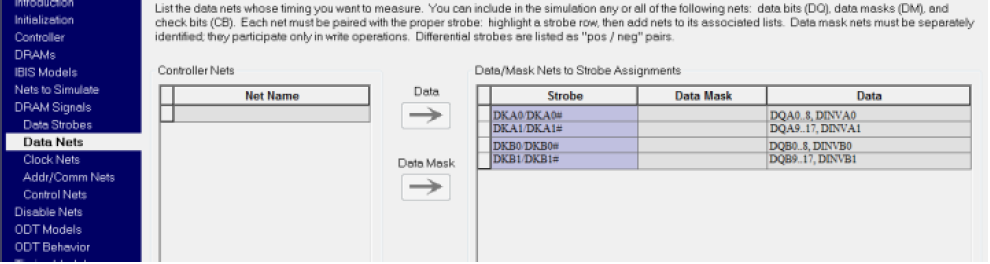

在“

数据网络”部分中,验证每个信号是否正确匹配每个门。 请注意,对于x18和x36位总线,信号是不同的,因此请确保针脚正确用于您的特定情况(图8a和8b)。

图 7.读取数据选通

图 7.读取数据选通 图 8a。 36位总线的信号组

图 8a。 36位总线的信号组 图 8b。 18位总线的信号组

图 8b。 18位总线的信号组并行总线测试通常是通过设置/保持选通与信号之间的时间来完成的。 DDRx向导需要所有这些要求以及其他临时值来验证结果。 这些值可能因微芯片而异;因此,建议您输入适用于特定存储设备的值。 此外,LPDDR3的默认时序信息与QDR-IV不兼容。 因此,应输入QDR-IV的所有时序信息,并与芯片的文档相匹配。

可以使用“

时序向导” (图9)来完成此操作,该

向导提示用户填写若干表格以用于随后的临时值的生成,或者您可以编辑与控制器和DRAM相对应的.V同步文件。

图 9.设置定时值请注意

图 9.设置定时值请注意 :由于仿真是在

LPDDR3模式下执行的,因此必须对结果进行相应的解释。

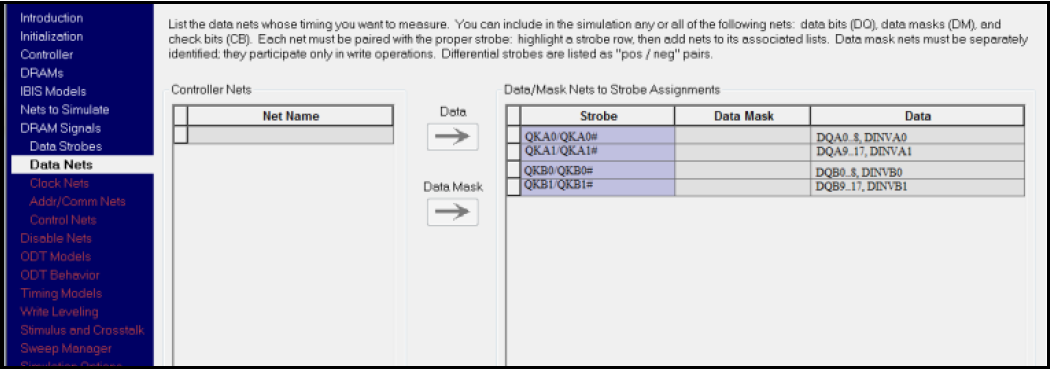

数据信号:写操作

数据写入操作及其分析类似于上述读取操作的分析。 但是,我们现在要考虑两个关键差异。 除了这两个细微差别,可以重复进行数据读取操作所采用的步骤以模拟数据写入。

在

要模拟的

网部分(图10)中,确保选择了

Only Write Cycles Only 。

还可以模拟

地址信号写入操作 。 并且不要忘记确保

选中了“

补偿偏斜启动以解决V-Time测量时间”复选框 。

图 10.数据记录

图 10.数据记录确保在“

数据选通”部分中选择了正确的门(图11)。 读事务和写事务之间的关键区别是用于同步数据的选通脉冲;此选通脉冲不同于用于数据读取操作的选通脉冲(图12和13)。

图 11.记录数据之门

图 11.记录数据之门 图 12.信号选通信号组(36位总线)

图 12.信号选通信号组(36位总线) 图 13.信号选通信号组(18位总线)

图 13.信号选通信号组(18位总线)总线地址,命令和控制

QDR-IV使用CK / CK#差分锁选择控制信号,地址和命令信号。 CK信号的上升沿用于输入有关端口A的信息,下降沿用于选择有关端口B的信息。

考虑到信号的完整性,地址线的波形必须满足安装要求以及时钟信号的上升沿和下降沿的延迟。 这与LPDDR3的行为非常相似。

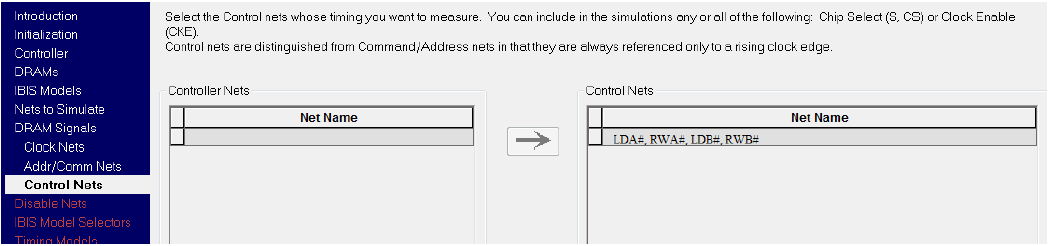

信号

LDA#,LDB#,RWA#和RWB#以相同的数据速率(单数据速率)同步。 这意味着这些信号仅在时钟脉冲的两个前沿之一上同步。 信号LDA#和RWA#在时钟的上升沿同步,而信号LDB#和RWB#在下降沿同步。

这些块在很大程度上是对称的-前差速器前轮与后轮没有太大差异。 这意味着,为了确保信号完整性,在时钟的上升沿或

下降沿采样时,

LDB#和RWB#的时序值应该几乎相同,即使不相同。 LPDDR3控制信号也仅在上升沿同步。

以下步骤专门针对使用QDR-IV的地址总线,命令和控制总线仿真。

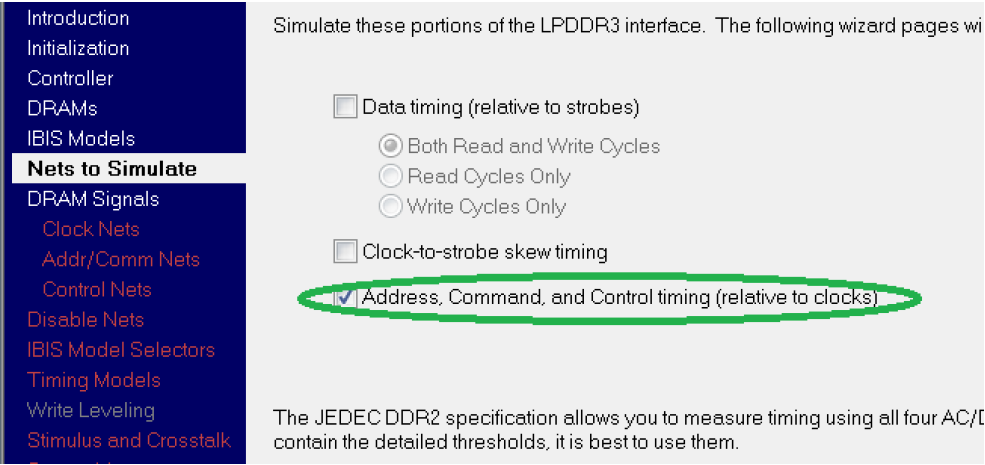

确保在“

要模拟的

网络”部分中选中“

地址,命令和控制时序(相对于时钟)”复选框(图14)。

图 14.选中地址,命令和控制时序框

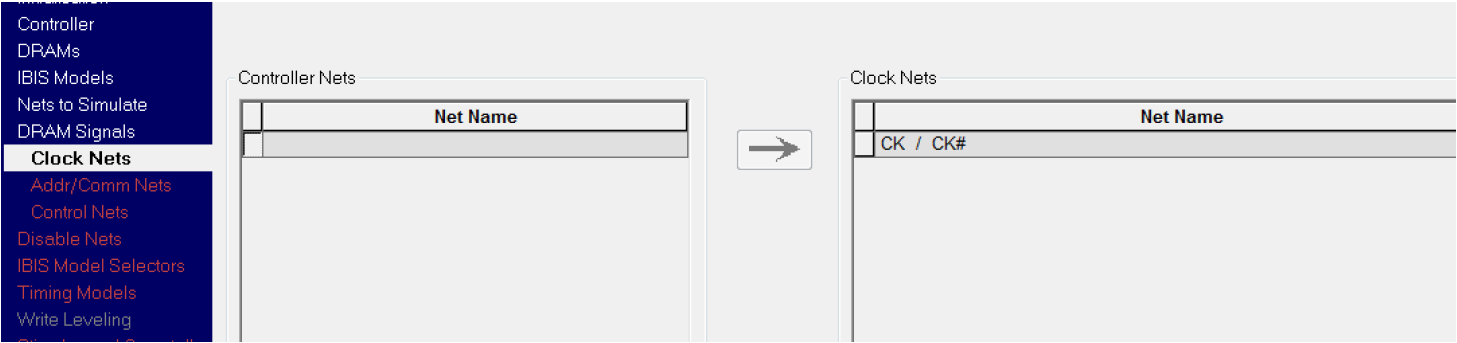

图 14.选中地址,命令和控制时序框在

Clock Nets部分中,确保选择了差分时钟信号对CK / CK#(图15)。

图 15.差分时钟的选择

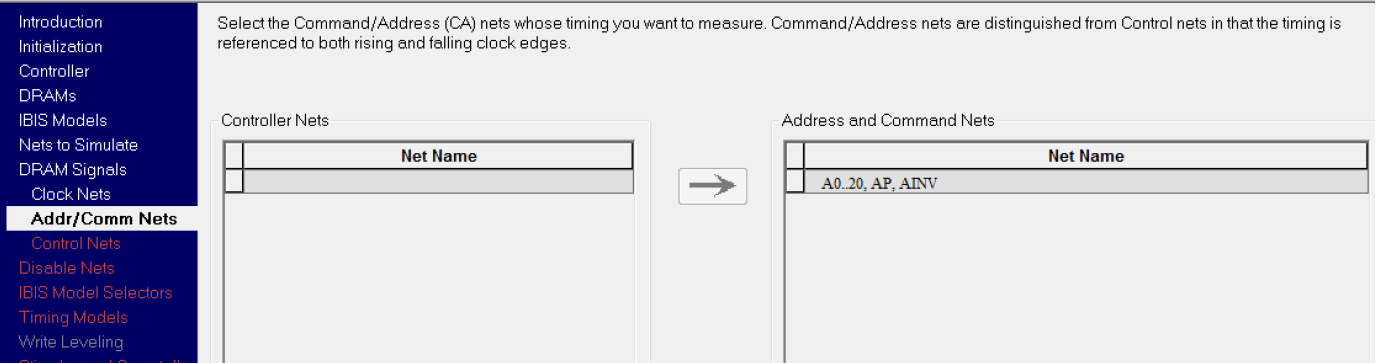

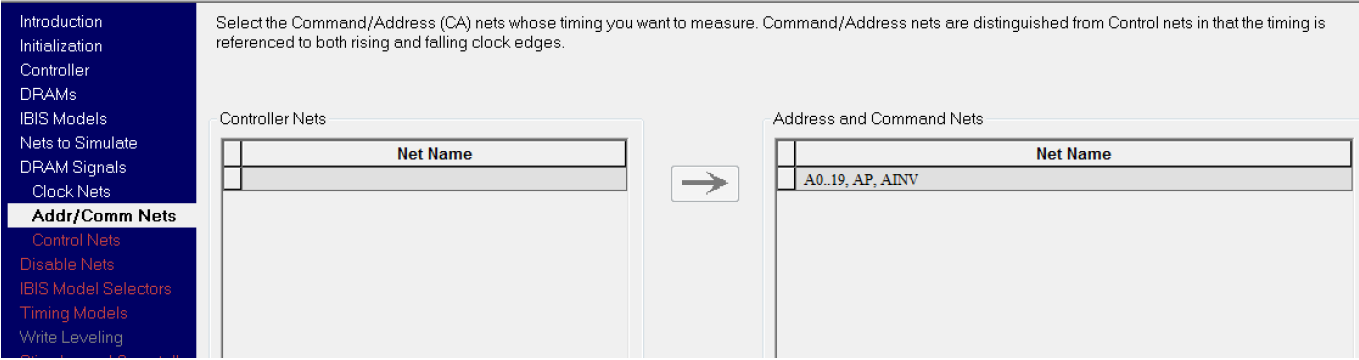

图 15.差分时钟的选择在“

Addr / Comm Nets”部分中,确保为x36位的设备选择位

A [20:0] ,为x18位的设备选择位

A [19:0] 。 另外,设置

AP和AINV信号 (图16和17)。

图 16. x36位总线的设置

图 16. x36位总线的设置 图 17. x18位总线的设置

图 17. x18位总线的设置在“

控制网”部分中,选择LDA#,LDB#,RWA#和RWB#信号(图18)。

图 18.控制信号

图 18.控制信号与对数据信号建模一样,请确保您使用的是带有时序参数的正确文件。 其余的建模和结果评估与LPDDR3相似。

“解释HyperLynx DDRx报告结果”结论

通过遵循本文中的简单说明,您可以受益于并使用DDRx向导帮助程序包来模拟和测试QDR-IV总线。

我希望本手册对某人有用。

真诚的,Filipov Bogdan(

pbo )。

借此机会,我想邀请REU的开发人员参加由Nanosoft和Mentor Graphics组织的研讨会:

“ Mentor Graphics的新一代电子设备设计解决方案”