问候,哈勃! 我的名字叫Daniil Smirnov,我在ITMO大学研究生院学习,我们的团队致力于在编程和建模实验室中与光纤传感器相关的项目的可编程电子学。 FPGA作为传感器的硬件基础,使用了现场可编程门阵列。 几年前,我们了解到FPGA制造商正在开发学生之间进行竞争。 从那时起,我们每年都会组成一个团队参加此活动,并且由于今年事实很特别,我们决定分享内部的一切。

参赛作品

那是2017年10月,我每周进行一次例行检查:对正在进行的有关本部门正在实施的主题的会议进行的分析。 有一次,我收到了Terasic的时事通讯:

在全球范围内,

使用FPGA上的调试板开发项目的

新竞争正在开始。 去年同一场比赛的经历在我的脑海中闪过,让我回想起:推迟到一个月的最后两周,长时间调试和调整算法,将所有频道发布给显示器,并保证不推迟到最后一天。

这是一次很酷的体验,在此期间,我们了解了有关SoC FPGA等平台的很多知识-大量逻辑元件和Cortex-A9处理器的互连以及它们之间以及与调试板上的外围设备的交互作用。

新竞争-新规则,新要求,新水平。 现在比赛分几个阶段进行:首先是地区阶段,然后是圣何塞决赛。 该板将发送给所有参与者

DE10-Nano ,并且现在您不仅可以选择基本的三个模块,还可以选择ADI公司的大型版! 但是,与往年的比赛不同,这次有必要签署该项目的保证书,并且如果未能兑现,则参赛者必须退还费用。 考虑到过去几年的统计数据,这很公平:

<...>来自20个欧洲国家的71个团队注册了比赛<...>法国的工业(ALTERA)和学术界(CNFM)的25名法官审查了32个项目[1]。

科学顾问就像想要参与这项工作的学生一样,已经在各种项目上承受了沉重的负担,但是比赛中的兴奋和学习很多新事物的动机成为重新参加比赛的重要理由。 剩下的就是要提出一个可以申请的项目。

一个项目的想法

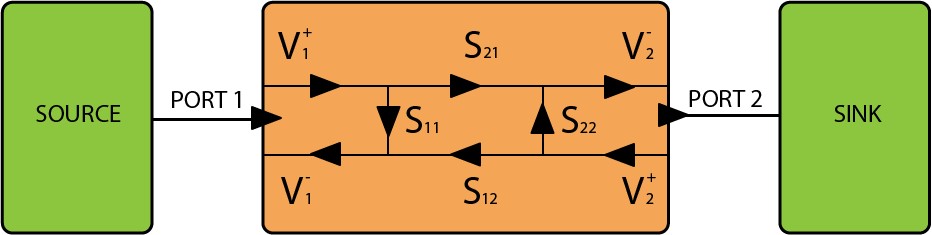

为了使该项目不会被搁置,因此决定实施一种对部门有用的设备,以后可以轻松地对其进行开发和改进。 根据该部门的活动领域,有多种选择:光学反射仪,频闪示波器等。快速查看现有应用程序和可用的其他板后,发现反射仪已经宣布,但是频闪示波器不能安装在此类元件上。 唯一活着的想法就是矢量网络分析仪。 几天前,将几个线圈带入实验室,但没有任何文件记录。 任务是确定这些线圈的至少近似特性。 众所周知,振荡电路是组装在其中的,因此主要任务是找出谐振频率。 在此类任务中,矢量网络分析仪(VAC或VNA-矢量网络分析仪)可以找到应用程序。 VNA允许您定义色散矩阵,也称为S参数矩阵。 在这种方法中,所研究的元素被视为黑匣子,其中分析了该设备端口的入射和反射信号。 因此,对于两端口系统,矩阵如下:

V1 + V2 +是到达端口的电磁波;

V1- V2--电磁波离开端口;

Sij是多径散射矩阵的元素。 [2]

多极S参数的测量方案

多极S参数的测量方案我们未能使用X射线(至少是地铁的X射线)检查组件和电路,因此以下电路被组装在膝盖上:使用发电机通过步进器交替地设置频率,步进通过循环器到线圈输入,循环器的第二个端口连接到线圈输入,第三个输入在其软件中具有幅度-频率分析模式的示波器。 这样的电路使得有可能测量参数S11,即测量参数S11。 反射。 最后,经过许多苦恼和校准,我设法消除了这一特性-但是要花多少钱? 该部门长期以来一直期望购买矢量网络分析仪来完成此类任务(以测量电子设备的AFC),但是这种购买总是会有所延迟。

在对线圈大惊小怪之后,决定组装您自己的具有可视化和舒适调整功能的电路分析仪。 从该系的学生和研究生那里发现兴奋和渴望为自己学习新事物的愿望并不难,因此,该团队迅速由一名电子工程师,一名芯片上系统的程序员,系统开发人员,我和两名导师组成。

快说不做! 在对项目的频带,处理算法和其他参数进行了大量讨论之后,该应用程序包含以下内容:

- 该项目是在DE10-Nano板上基于SoC FPGA的矢量电路分析仪;

- 要求的其他板:带可编程频率发生器的板,高频混频器和带ADC的板;

- 工作频率范围:根据附加板提供的参数;

- 快速增加连接端口数量的可能性;

- 振幅和相位分量的输出到屏幕;

- 矢量网络分析仪的其他基本输入/输出功能。

为了进入下一个阶段,有必要使项目页面获得在站点上注册的用户的足够“赞”。 起初,一切都进行得很好,但是与其他项目相比,一些可疑项目开始获得不切实际和对比的喜欢和观点价值。 原来,竞赛网站太容易作弊了。

一段时间后,组织者告知评审团仍会选择决赛选手,因此用户的赞誉实际上已经失去了分量。 1月31日,我们的团队出现在进入下一阶段的人员的列表中,我们开始对项目进行更详细的考虑,以期进行调试。

严酷的现实

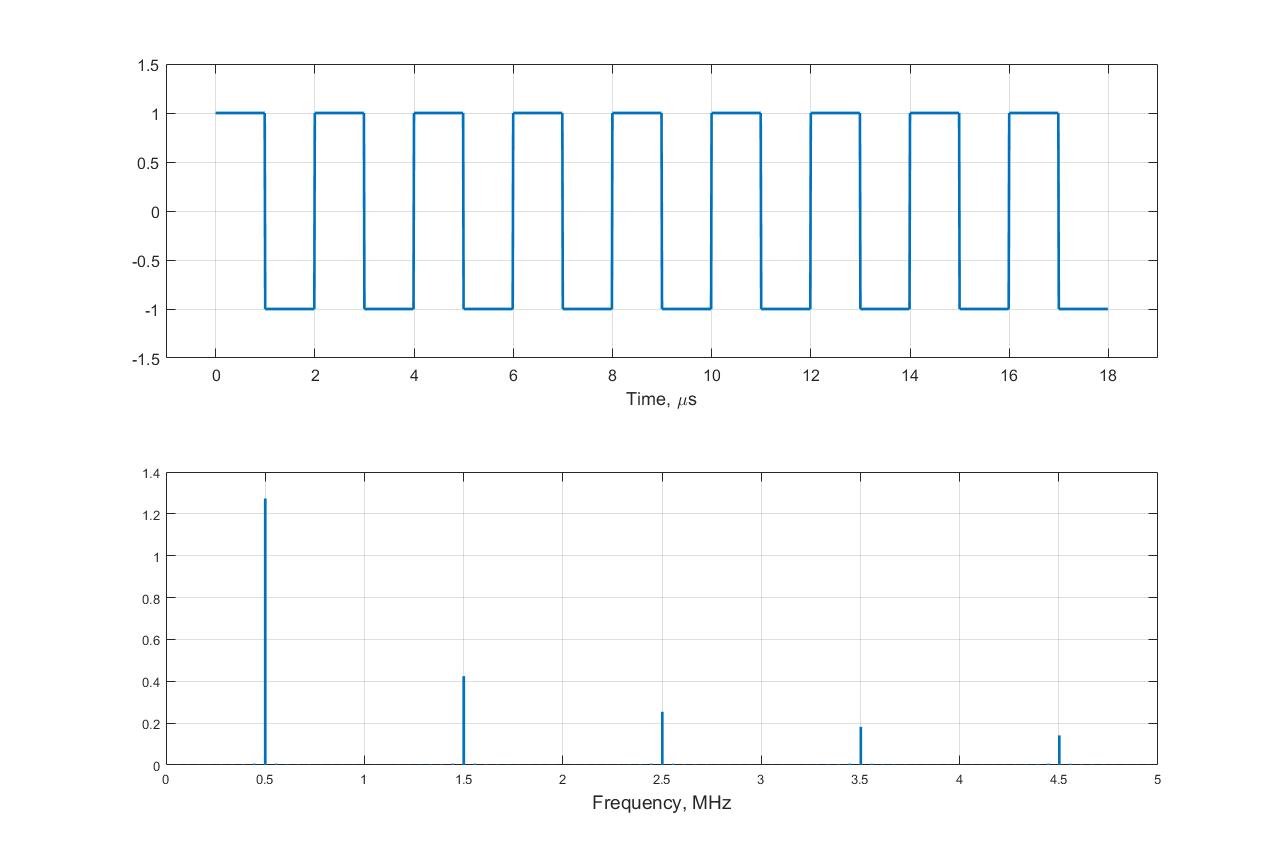

首先是DE10-Nano板。 令人愉快,但有点奇怪:他们希望董事会能够团结在一起。 几天后,海关打来电话:费用已经到位,它们都超过了价格门槛,因此您需要为通关支付大约等于这些费用成本的费用。 这种情况使我们感到沮丧,但不适合我们:我们拒绝了董事会。 在没有搅拌机和发电机的情况下,有必要寻找新的解决方案。 怎么办 首先想到的不是最准确的解决方案,而是不寻常的解决方案:使用常规的GPIO引脚并从中产生弯曲。 模拟低通滤波器安装在该脚的输出端,其截止频带略大于最大曲折频率。 对于初学者,建议从1 MHz开始分析(例如):然后在滤波器之后,我们将获得或多或少的纯正弦(最高谐波将被滤波器截断),依此类推,直到频率下降到滤波器后信号的频率为止。会有两个谐波。 曲折是奇次谐波的总和,每个谐波的比例贡献是事先已知的[3]。

时域和频域中的曲折示例:500 kHz,1.5 MHz等谐波信号的分量在频谱上可见。

时域和频域中的曲折示例:500 kHz,1.5 MHz等谐波信号的分量在频谱上可见。使用截止频率为1 MHz的滤波器,您可以降低到33。(3)kHz。 在这个频率之后,我们应该在滤波器后面得到两个正弦之和。 它们幅度的比例比例是已知的(正弦函数),被测设备对1 MHz频率(一次奇次谐波)的响应也是如此,因此我们需要组成一个未知数的方程式,并计算对33(3)kHz频率的响应特性! 最初,这种解决方案似乎太简单了,因此对于初学者来说,它被告知所有人,希望有人会发现错误。 没有发现错误,但是随着讨论的进行,发现了许多限制:

- GPIO脚并不是弯曲的最佳来源,尤其是随着频率的增加;

- 在可用组件上焊接紧凑型滤波器将是一项艰巨的任务。

- 即使可以克服这些限制,相位检测也会出现同步问题。

假设我们已经解决了模拟方面的所有问题; 以编程方式,另外两个出现:

- 随着频率的降低,先前每次检测和计算的误差将有助于后续的测量。

- 随着频率的降低,计算特性的时间将大大增加。

最后,最后但并非最不重要的一点。 如果可以通过线性传递函数描述被测元件,则可以使用所描述的电路。 但是,如果我们测量具有非线性特征的黑匣子,那么这个想法有很多弊大于利。 剩下的时间不多了(第一个结果应该在开发板到达两个月后显示),因此,经过深思熟虑,我们决定使用现有的调试板仔细检查库存-并找到一个

125 Msps的

14位DAC ! 不是最优雅的解决方案,但别无选择,我们将其用作输出信号发生器。

第一个概念

选定的DAC作为发生器,在并行总线的输入端接收数据,并使用来自FPGA的时钟信号将其锁存。 这样的电路是我们电路中同步的理想选择。 但是,检测仍然存在问题。

是的,在同一块板上有一个65 Msps的14位ADC。 但是只有发生器的能力可能更高,根据科特尔尼科夫定理,该ADC将不再以最大频率工作。

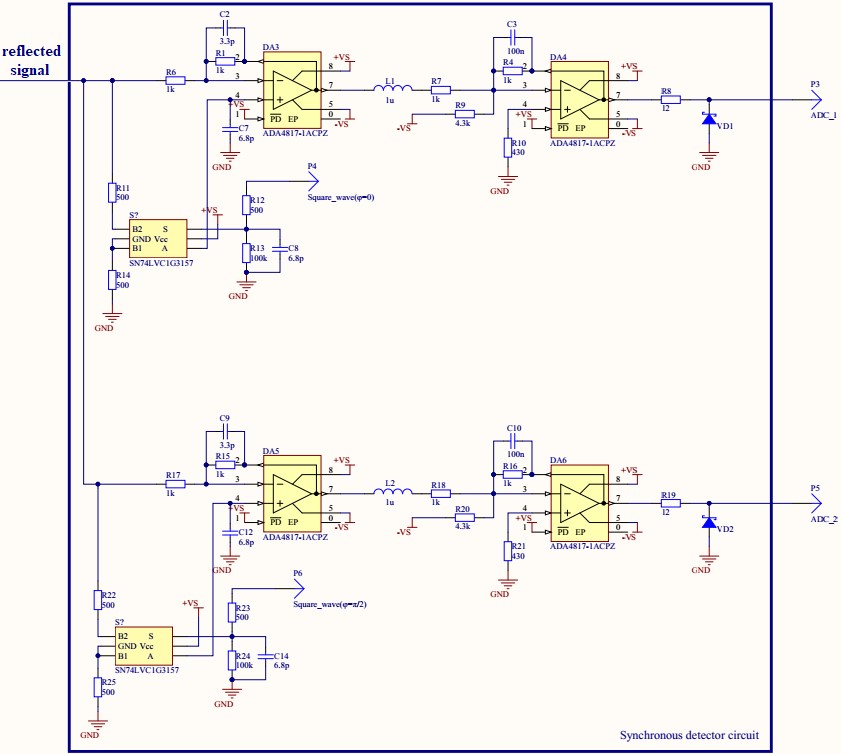

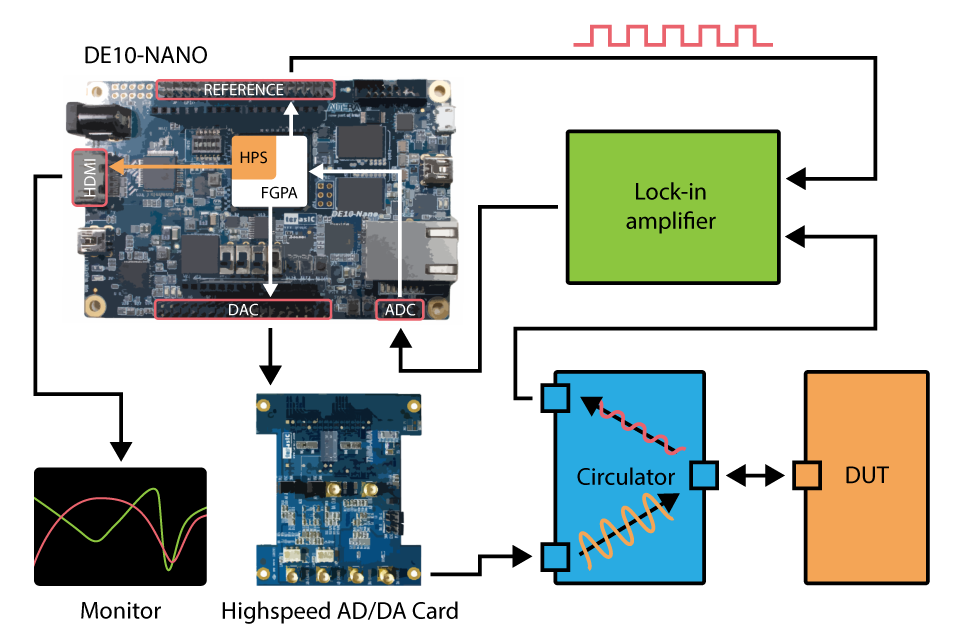

在与经验丰富的电子工程师讨论此问题时找到了解决方案。 事实证明,对于我们的任务,我们可以使用锁定放大器电路:这种检测器的输出是两个恒定值,即相位和正交分量,您可以从中获取信号的幅度和相位,并且由于它们是恒定的,因此可以对其进行检测。即使在DE10-Nano上安装了慢速ADC! 考虑到检测器输入是来自循环器的信号,并且输出连接到DE10-Nano板上的ADC,因此决定首先在LTSpice中对电路建模,然后才选择组件并组装电路。

关于同步检波器和循环器同步检测器还用于数字信号处理中,以针对噪声背景检测各种信号。 苏黎世仪器(Zurich Instruments)有一个很好的描述[4],在我们的情况下,检测如下:使用高频开关和运算放大器,将已知频率的反射信号乘以曲折:

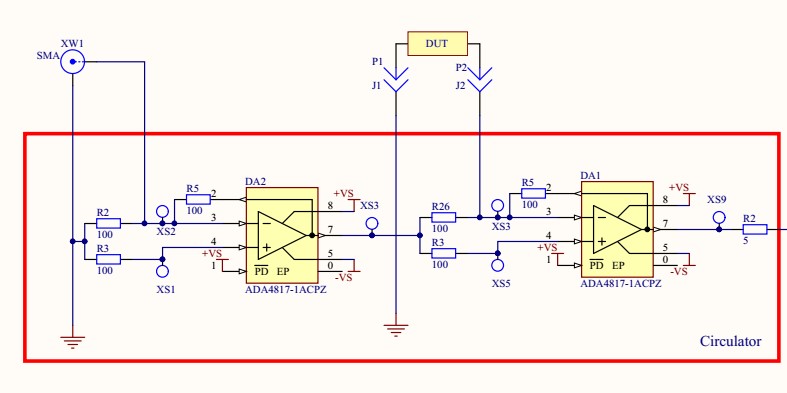

反射检测电路

反射检测电路实际上,乘法是通过切换运算放大器的工作模式来实现的,并且切换由来自DE10-Nano板的两个曲折控制:一个曲折与原始信号(在设备的输入端接收)同相,另一个曲折的相位延迟为90度。

乘法的结果是将有用信号传输到DC分量,并且上面的所有频率都不再有意义,因此可以将其滤除:

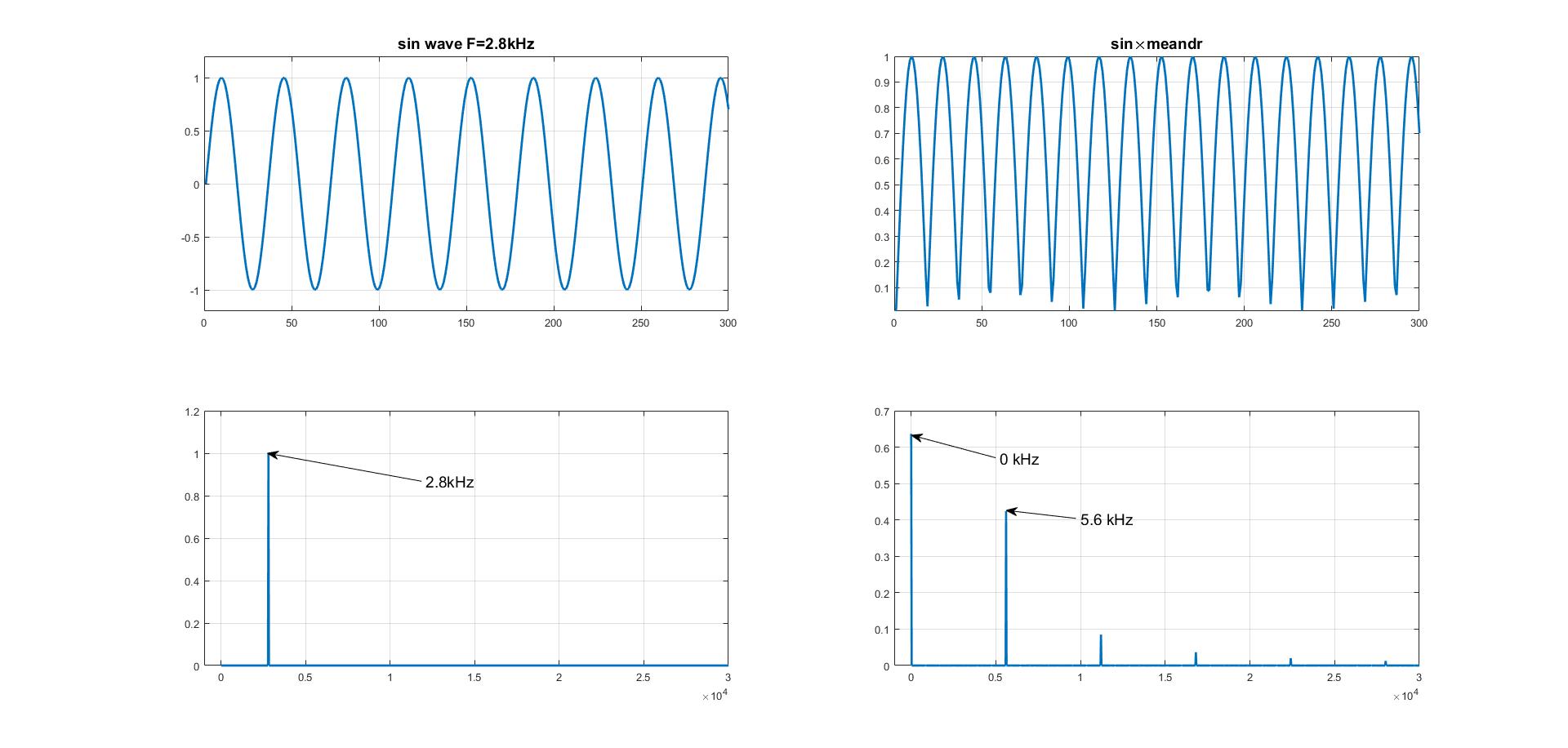

乘法前后的信号频谱:在运算放大器的输出端,您可以组装一个简单的低通滤波器以仅隔离直流分量

乘法前后的信号频谱:在运算放大器的输出端,您可以组装一个简单的低通滤波器以仅隔离直流分量运算放大器(运算放大器)上的循环器是闭合成环的运算放大器的串联电路。 OA循环器有许多用途,特别是用于调谐天线,放大器,发生器,千兆位以太网等。 在高达数百兆赫的频率范围内。 创建VAC时,使用了基于两个运算放大器创建的循环器电路[5]。

连接被测设备的电路图

连接被测设备的电路图  更新的项目概念

更新的项目概念频率设置为1 Hz至1 MHz(步长设置为几Hz)的正弦信号被馈送到循环器的第一端口。 所研究的设备连接到第二个端口,具体取决于其频率响应,信号的反射系数会发生变化。 反射信号被馈送到端口3,在该端口上组装了同步检测器电路,以确定频率和相位特性。 为了正确操作,将环行器的端口匹配到100欧姆的阻抗,这与DAC的输出电阻和所研究器件的选择有关。

在项目完成之前还剩下不到一个月的时间,在截止日期之前,有必要准备报告材料:竞赛页面上对该项目的详细描述,在GitHub上公共领域发布的项目以及所做工作的视频报告。

由于我们现在知道什么数据会输入和输出,因此我们开始进行SoC FPGA项目。 我们看到了该项目的实施过程:用户设置计划测量的频率范围,FPGA使用DAC在指定的时间间隔内依次产生谐波,ADC在输入端接收正交分量和相位分量,将其转换为当前频率下的幅度和相位值,获得的值将实时显示在连接到调试板上的监视器上。 在监视器上显示信息方面已经取得了许多成就,因此主要部分是实时正确呈现数据并将图像输出到HDMI。 我们未分组。 第一组负责处理器程序的任务,以更详细地了解必要的初始化以及有关数据可视化的问题。 我们还要求他们将屏幕分辨率提高到1024x768 [6]。 第二小组详细介绍了该部分在FPGA上的实现,然后应通过light_h2f接口总线将其提供给处理器,并对第一个原型同步检测器的可操作性进行测试。 在消除了缺陷并成功测量了几个元素的特征之后,剩下的时间不多了,因此接下来的两天专门用于将系统连接在一起,添加报告和编辑视频。

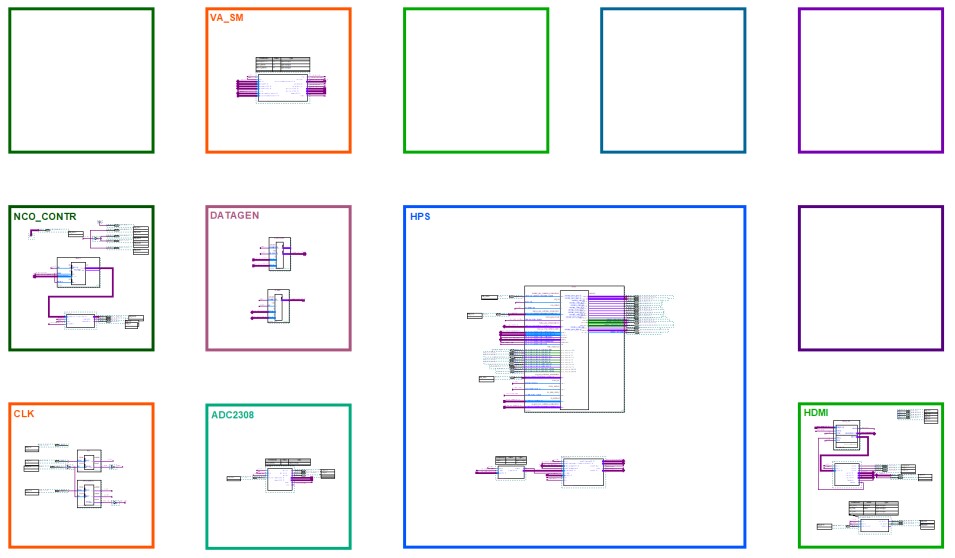

Quartus II中顶级文件的外观

Quartus II中顶级文件的外观最后一分钟

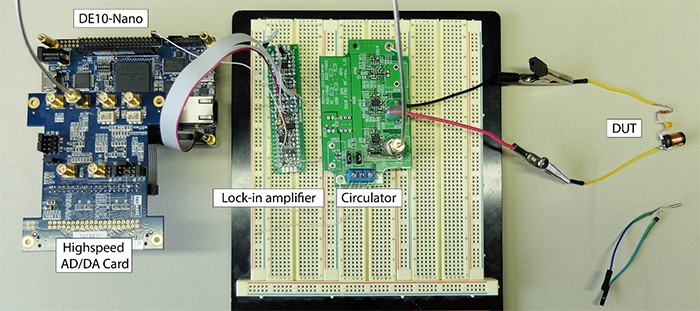

在实验室里待了超过两天后,我们组装了整个系统。 它不适用于整个潜在频率范围,仅测量了S11参数,并在监视器上反映了所连接设备的测量相位和幅度特性。 外部组装的设备看起来仍然不太吸引人-通过单芯线连接的三个独立的板,但这是一个可行的原型,您可以在下一阶段穿上Marafet。 我们编写了文字,说明了实施的阶段,拍摄了视频,所有内容都上传到了站点并开始等待。

当然,我们向一些朋友发送了这些材料的链接,以稍微增加视图。 但是,有一天,人们的观点开始增长,好像有人将其合并为晋升。 经过一番分析,结果是:在hackaday.io [7]上注意到了我们的项目,并且绝大多数意见都来自那里。 看到对我们项目的第一反应很有趣。 受到启发,我们开始等待结果。

可是

这不是我们参加比赛的第一年。 对于我们来说,该项目是先前实施的学生工作中最周到的。 但是它并没有一起发展:我们没有进入下一阶段。 也许这是由于我们与法官之间的误解。 也许该项目只是没有完全进入FPGA当前趋势的领域(加密,并行计算,神经网络等)。 但是对我们来说,这是SoC FPGA开发的一大步,这是新的开发分支,最重要的是经验。

聚苯乙烯

恭喜在决赛中获得亚军的俄罗斯代表!

我感谢我的项目同事Danila Nikiforovsky和

Yevgeny Vostrikov以及领导人

Ivan Deineku ,

Philipp Shuklin和Artem Aleinik的积极参与和支持。

参考文献

[1] 2015年欧洲创新大赛

www.innovateeurope.org/eu/2015winner.html[2]自动测试高速接口的工程师指南,何塞·莫雷拉(Jose Moreira),休伯特·韦克曼(Hubert Wekmann),2010年,附录F第503页

[3]矩形脉冲周期序列的频谱,

en.dsplib.org / content / fourier_series_pimp / fourier_series_pimp.html[4]锁定检测的原理和最新技术,苏黎世仪器公司

www.zhinst.com/applications/principles-of-lock-in-detection[5]不含铁氧体和磁体的低频环行器/绝缘体

www.cqham.ru/oth9.htm[6] DE10-Nano板的VAC项目

github.com/tvShushtov/em078_vector_analyzer[7]关于Hackaday上VAC的文章

hackaday.com/2018/05/09/vector-network-analyzer-uses-soc-fpga