使用快速DDR SDRAM存储模块的电子设备的设计需要特别注意信号完整性问题。 本文讨论了用于解决此类问题的现代建模工具。如今,几乎所有现代电子设备都配备了内存模块。 服务器,计算机,智能手机,游戏机,GPS导航器和大多数其他设备均基于处理器和FPGA设计。 这样的设备需要具有大通道带宽的高速存储器或双频存储器(DDR)存储器。 随着新一代DDR SDRAM(具有随机访问和双倍数据传输速度的同步动态内存)的出现,数据交换速度,容量和内存消耗都得到了降低。

当设计带有DDR存储器的设备的印刷电路板时,可能会出现许多困难,其中之一就是信号完整性问题。 本文讨论了确保使用DDR内存的设备中信号完整性的问题。

数字数据信号的噪声和抖动

当从控制器到微电路接收/传输内存总线的时钟信号时,由于发射器和接收器自身的抖动,传输线中的损耗,噪声和干扰,可能会发生各种干扰。 所有这些都会导致出现抖动和数字接口信号的形状失真。

任何添加到理想信号上的多余能量都可以视为噪声。 这可能是由于来自相邻线路的干扰,传输通道设计不良,阻抗不一致以及其他导致脉冲前沿模糊的因素引起的。 在没有噪声的情况下,实际信号与理想信号相同。

与理想波形的任何偏差都会影响其完整性。 时间偏差(抖动)和幅度/电压偏差(噪声)也会影响系统性能。 如果您不能确保信号的完整性,那么DDR系统将使用错误的信息,这将大大增加误码率BER(误码率)的强度。 最终,该系统将无法正常工作且效率低下。

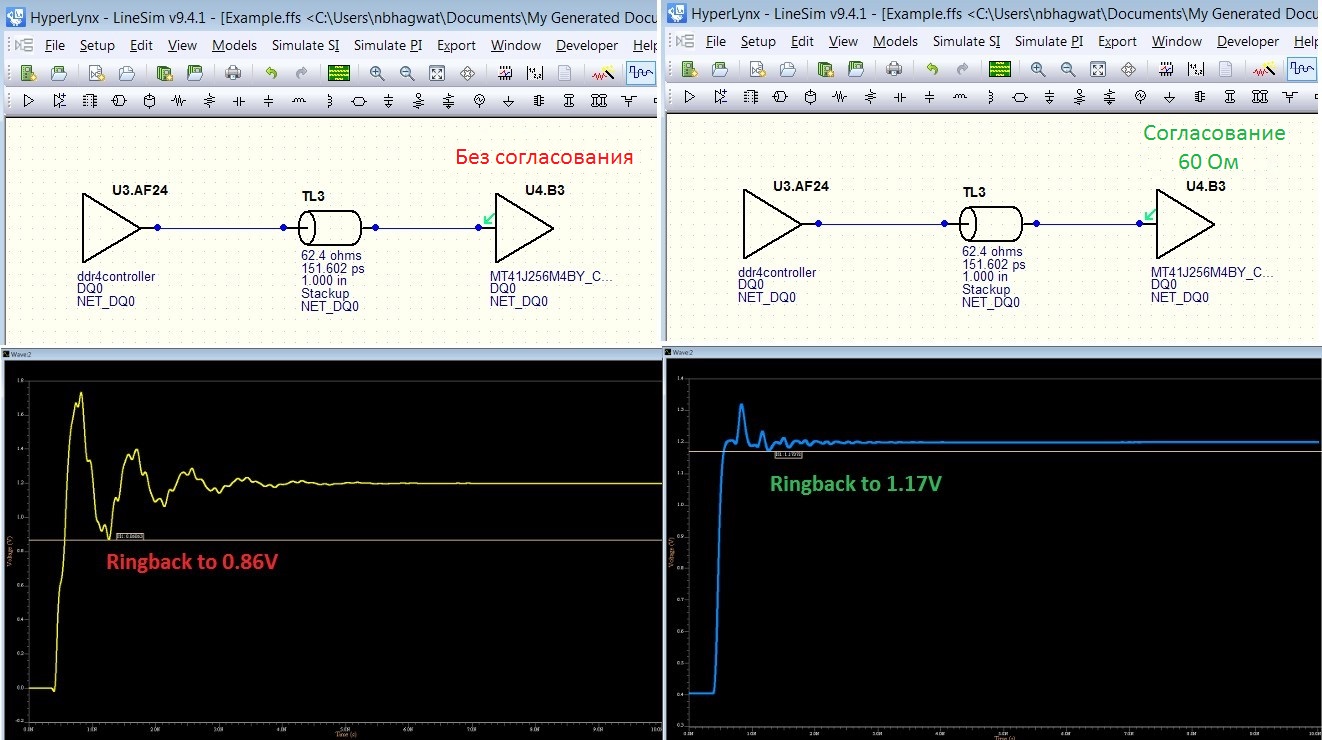

考虑一个具体的例子。 如果工程师将发射器连接到相距一定距离的不一致的接收器,则波形将类似于图1a所示:在这里,您可以清楚地看到0.86 V的“振铃”和1.75的虚假增加的发射。 V处于1.2 V信号时。所有这些都可能导致DDR4逻辑故障,如果电路板采用这种拓扑设计,则数据流中有100%的概率会出现错误,从而可能导致系统错误操作。 。

从理论上讲,可以通过减少传输线的长度来解决“振铃”和发射问题,但是不幸的是,这在实践中很少起作用。 最有效的方法是通过阻抗匹配接收器/发送器,结果是噪声电平降低,信号形状变得更好(见图1b)。

图 1.信号质量有问题的拓扑:a)协调前b)协调后

图 1.信号质量有问题的拓扑:a)协调前b)协调后在这方面,出现了一个问题,即使用哪个批准等级以及如何计算该等级,因为即使等级的很小变化也会严重影响系统性能。 解决此问题的唯一方法是特别是使用HyperLynx中使用的交互式对帐向导进行模拟。

DDRx的时序问题

由于工作在千兆赫频率的并行总线(例如DDR3 / 4)越来越多地用于印刷电路板的设计中,因此信号完整性问题尤为严重。 例如,DDR3 SDRAM在速度和频率性能上与DDR2有很大不同:DDR2的最大时钟频率为800 MHz,而DDR3的最大频率为1600 MHz。 由于单元电源电压的降低,新型RAM的创建者设法将其能耗降低了多达15%,鉴于DDR2令人印象深刻的性能,这可以称为真正的突破。 DDR3使用带有模块内(ODT)匹配的网络“ Fly-by”命令/地址/控制总线拓扑。 同时,DDR3带来了信号完整性方面的新问题,特别是与ODT电路相关的问题,更高的数据传输速率和时间失真。

尽管有一些控制器执行自动读/写校准,以优化时间间隔,但开发人员仍需要确保正确的时间。 DDR3接口中的时间边界太小,以至于无法凭经验来进行优化,因此,为了保证接口的高速运行,有必要对电路进行详细的分析。

如果没有其他工具的帮助,很难分析这种复杂的时间关系。 为了一般地识别和消除潜在的问题或计算复杂的时间关系,工程师必须分析因果关系,这是一项复杂且耗时的任务。

这种设计问题通常会导致项目计划的延迟,结果会大大增加成品进入市场所需的时间。 先进,功能强大的仿真工具可以通过将信号优化到可接受的BER级别来帮助工程师快速发现并纠正错误。

DDR SDRAM系统的信号完整性分析

JEDEC半导体工程标准化委员会已经批准了开发高质量产品时必须遵循的一系列要求。 DDR SDRAM必须满足这些要求,才能确保正常运行并防止信号完整性问题。 然而,进行所有必要的测量和计算通常充满许多困难。

有时,严格遵循控制器供应商提供的布局说明,可以完全避免这些计算。 但是,如果由于特定项目中的各种限制而无法实施此类建议,该怎么办? 如果花费大量时间来确保项目满足所有建议和要求,该怎么办? 在这种情况下,您需要使用工具来快速验证项目,然后再将其投入生产。

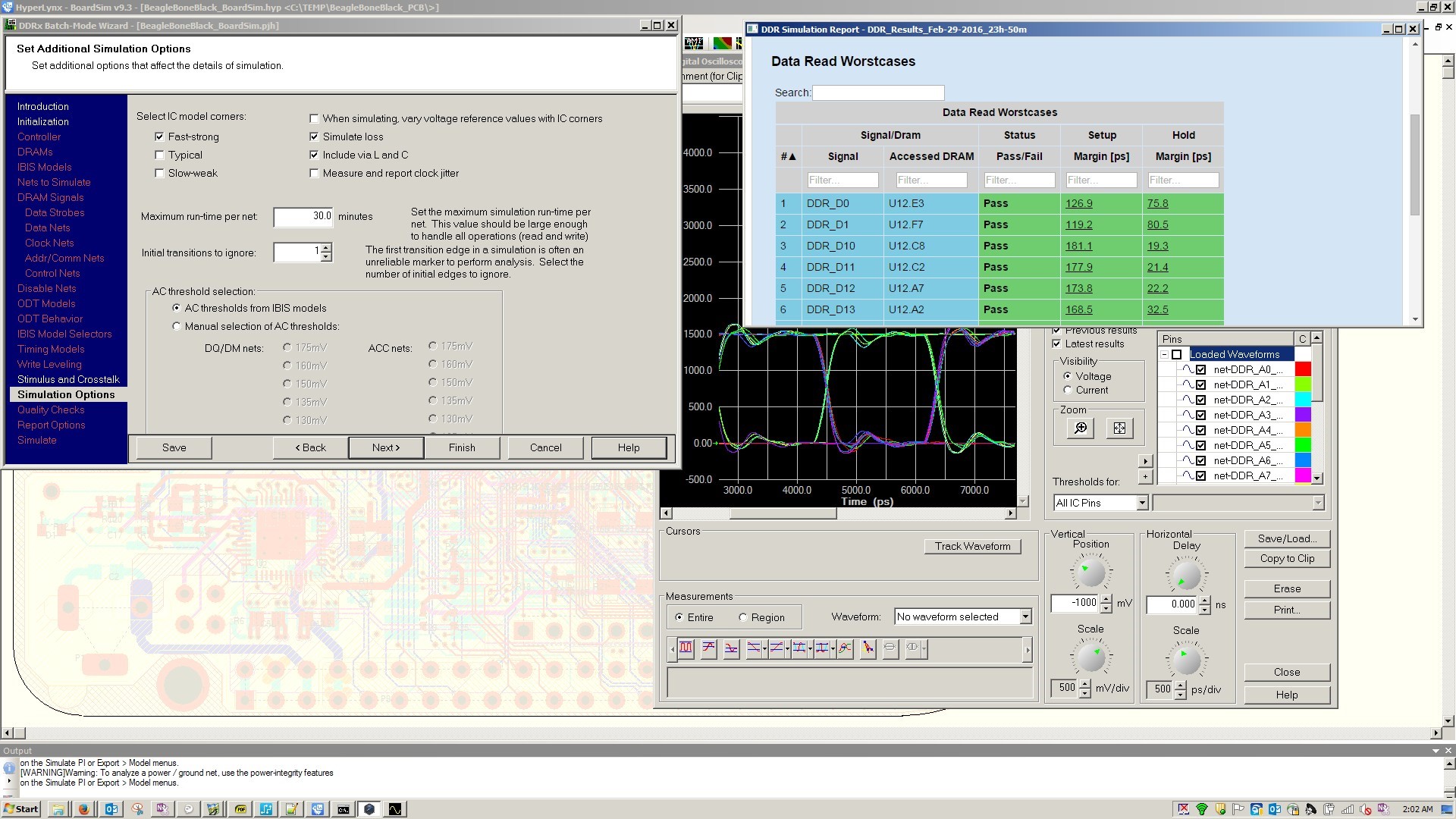

使用HyperLynx DDR(参见图2),您可以一次迭代模拟整个DDR通道。 为此,您只需要绑定制造商网站上可用的适当设备型号。 之后,仿真的建立时间将仅需十分钟,这将允许进一步建模而没有延迟。

图 2.使用HyperLynx DDR交互式助手进行建模

图 2.使用HyperLynx DDR交互式助手进行建模设置过程在直观上很简单,因为助手需要交互式地请求所有设置仿真所需的参数。 用户只需输入相关信息,例如选择控制器和存储设备的IBIS模型,读取/写入周期的传输速率,ODT等。所有创建的配置都可以保存以备将来使用,这将减少将来项目中的设置时间。 可以在跟踪之前或之后进行仿真,以帮助确定PCB堆栈的要求。

仿真结果分析

仿真包括信号完整性分析和整个DDR总线的同步。 在模拟过程完成后,根据配置信息和在交互式助手中输入的数据,将创建一个报告,其中包含有关检查通过(未通过)的数据。 可以对结果进行过滤和适当地组织,以便仔细研究数据读/写周期,地址和命令总线或差分电路中的时序和信号完整性问题。 所有报告结果都与相应的仿真数据绑定在一起,以便快速访问用于查看信号图形波形的工具。

可以将由DDRx向导创建的批处理模式下的仿真数据保存到磁盘,这使您可以使用HyperLynx示波器同时仿真多个电路,并详细研究离线模式下的信号完整性问题。

结论

DDR SDRAM为电子设备的开发开辟了新的可能性。 与其他高速接口一样,使用DDR存储器具有多种功能。 必须仔细研究信号完整性问题,以避免产品制造过程中不必要和昂贵的迭代。 建模是解决此问题的绝佳方法,可让您考虑板级的影响,例如阻抗和时间延迟的变化,从而提供对存储器接口的全面控制。 强大的分析工具将有助于确保项目符合JEDEC的建议,并确保最终产品具有高性能和可靠性。

HyperLynx DDR可以由许多CAD PCB设计公司共享,包括PADS和Xpedition。

本文发表在2018年第7期的《现代电子》杂志上(www.soel.ru)